Автоматическое блокирование позволяет вам анализировать модель, которая содержит объекты, которые не поддерживает Simulink® Design Verifier™.

Когда вы включаете автоматическую блокирующую опцию (она включена по умолчанию), программное обеспечение рассматривает только интерфейс неподдерживаемых объектов, не их фактическое поведение. Этот метод позволяет программному обеспечению завершать анализ. Однако анализ может достигнуть только частичных результатов, если какой-либо неподдерживаемый элемент модели влияет на результат симуляции.

Если вы включаете автоматическое блокирование, когда анализ Simulink Design Verifier прибывает в неподдерживаемый блок, программное обеспечение “тупики” тот блок. Анализ игнорирует поведение блока, и в результате блок выход может принять любое значение.

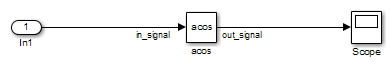

Simulink Design Verifier не поддерживает блоки Тригонометрической функции, когда параметр Function устанавливается на acos, такой как тот в следующей диаграмме.

При блокировании этого блока во время анализа, out_signal может принять любое значение, следующими результатами.

| Аналитическая модель | Результат Блокирования out_signal |

|---|---|

Поиск ошибок проектирования |

|

Генерация теста |

|

Доказательство свойства |

|

Модель sfcndemo_sfun_fcncall Simulink в качестве примера имеет Блок s-function. S-функция sfun_fcncall инициировал выполнение подсистем вызова функций f1 subsys1 и f2 subsys2 на первых и вторых элементах первого выходного порта.

Если вы не включаете поддержку S-функции в Simulink Design Verifier, и автоматическое блокирование включено, анализ игнорирует поведение S-функции. В результате код, который инициировал эти две подсистемы вызова функций, проигнорирован, приведя к двум невыполнимым целям. Поскольку вызовы функции проигнорированы, содержимое тех подсистем эффективно устраняется из анализа.

Чтобы включить поддержку S-функции в Simulink Design Verifier, смотрите Ограничения Поддержки и Факторы для Кода C/C++ и S-функций

В этом разделе описываются рабочий процесс для использования автоматического блокирования с простой моделью Simulink как пример.

Следующая модель содержит блок Discrete State-Space, который не совместим с Simulink Design Verifier.

Из Редактора Simulink существует два способа проверять, совместима ли модель с Simulink Design Verifier: проверкой совместимости Simulink Design Verifier или путем выполнения анализа Simulink Design Verifier.

Осуществлять проверку совместимости Simulink Design Verifier:

На вкладке Design Verifier нажмите Check Compatibility.

Выберите анализ, который вы хотите выполнить.

Запускать анализ Simulink Design Verifier, на вкладке Design Verifier, в разделе Mode, избранной любой из этих опций:

Выберите Design Error Detection, затем нажмите Detect Design Errors.

Выберите Test Generation, затем нажмите Generate Tests.

Выберите Property Proving, затем нажмите Prove Properties.

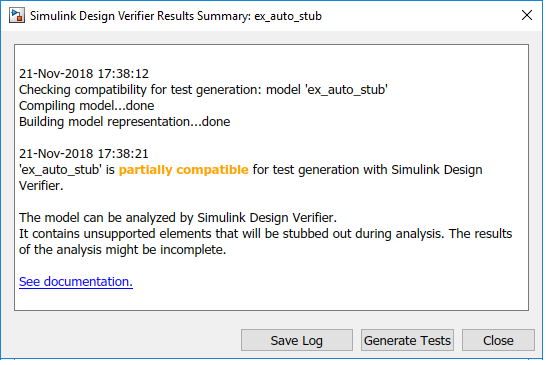

Программное обеспечение сначала проверяет совместимость модели. Если сама модель несовместима, например, если она использует решатель переменного шага, анализ не может продолжиться.

Если это находит несовместимые элементы в модели, программное обеспечение анализирует модель и, по умолчанию, гасит несовместимые элементы. Диагностическое Средство просмотра также открывается, перечисляя несовместимости.

Примечание

Для получения дополнительной информации, Диагностика вида на море.

Автоматическое блокирование включено по умолчанию. Чтобы изменить автоматические блокирующие настройки, в диалоговом окне Configuration Parameters, на основной панели Design Verifier, выбирают Automatic stubbing of unsupported block and functions. Когда вы запускаете анализ, программное обеспечение говорит вам, что блокирование включено, и анализ продолжается.

Если при запуске анализ с автоматическим включенным блокированием, убедитесь, что рассмотрели результаты. В этом отчете, сгенерированном после анализа генерации теста, вы видите таблицу неподдерживаемых блоков что программное обеспечение, с которым сталкиваются.

Неподдерживаемые блоки

Сгенерированный аналитический отчет для модели в качестве примера показывает, что цели не решены из-за блокирования. Программное обеспечение не может сгенерировать тесты, потому что оно не изучает операцию блока Discrete State-Space.

Цель, нерешенная из-за блокирования

Если ваш анализ не достигает полных результатов из-за блокирования, можно задать замены пользовательского блока, чтобы дать более точное определение неподдерживаемых блоков. Для получения дополнительной информации выполните шаги в Заменах Блока для Неподдерживаемых Блоков.