Можно использовать socExportReferenceDesign функция, чтобы сгенерировать исходный проект из модели SoC Blockset™ и избежать ручных шагов, требуемых сгенерировать и указать пользовательский исходный проект. Функция генерирует эти артефакты.

Файлы регистрации плат

Регистрационный файл исходного проекта

Репозиторий IP

Спроектируйте файлы

Ограничительные файлы

Модели SoC могут быть одним из этих типов.

Модель SoC с FPGA, памятью и дополнительным вводом-выводом (никакой процессор)

Модель SoC с процессором, FPGA, памятью и дополнительным вводом-выводом

При экспорте пользовательского исходного проекта из модели SoC исходный проект не включает проект под тестом (DUT), и интерфейс к DUT отсоединен. После генерации исходного проекта можно интегрировать пользовательский IP при помощи инструмента HDL Workflow Advisor. Ваш пользовательский IP должен иметь тот же интерфейс как блок FPGA Algorithm.

Чтобы экспортировать пользовательский исходный проект, сначала создайте модель SoC, чтобы смоделировать систему и ввод-вывод, доступный на вашей плате. Чтобы создать модель SoC Blockset, используйте один из этих методов.

Создайте модель при помощи (рекомендуемого) шаблона SoC Blockset. Для получения дополнительной информации смотрите Шаблон Использования, чтобы Создать Модель SoC.

Создайте модель SoC с нуля. Для получения дополнительной информации смотрите, Создают Приложение Проекта SoC.

Включайте подсистему DUT в модель. Эта подсистема должна иметь тот же интерфейс как ядро IP, которое вы разрабатываете. Поскольку сгенерированный исходный проект не включает подсистему DUT, DUT может быть простой моделью или только блоком передачи.

Можно использовать MATLAB в качестве ведущей функции AXI в экспортируемом исходном проекте, чтобы взаимодействовать с устройством SoC от хоста. В Simulink®, открытом диалоговое окно Configuration Parameters путем нажатия на Model Settings на вкладке Modeling, и на левой панели, выбирают Hardware Implementation. Затем расширьте Target hardware resources, выберите FPGA design (top-level), и затем выберите Include 'MATLAB AXI Master' IP for host-based interaction.

В поле IP core clock frequency (MHz) задайте тактовую частоту ядра IP в МГц.

Чтобы гарантировать, что ваша модель SoC поддерживает генерацию кода, используйте инструмент SoC Builder, чтобы сгенерировать исполняемые файлы и развернуть вашу модель. Для получения дополнительной информации об инструменте SoC Builder, смотрите, Генерируют Проект SoC.

Для примера, показывающего этот рабочий процесс на случае только для FPGA, смотрите Экспорт Пользовательский Исходный проект.

Если ваша модель содержит и FPGA и подсистемы процессора, эти дополнительные шаги требуются прежде, чем экспортировать исходный проект.

В параметрах конфигурации нажмите Hardware Implementation слева. Затем расширьте Target hardware resources и выберите Include processing system in FPGA design (top-level).

Запустите инструмент SoC Builder и выполните ведомые шаги для генерации кода. Этот шаг требуется, потому что SoC Builder автоматически генерирует файл дерева устройств (.dtb) на SD-карте под названием hdlcoder_rd/soc_prj.output.dtb и модель ПО с именами согласующего устройства.

Скопируйте файл дерева устройств с папки hdlcoder_rd к корневой папке SD-карты. В сгенерированном plugin_rd.m файл, файл дерева отдельного устройства задан как:

hRD.DeviceTreeName = 'soc_prj.output.dtb';

socExportReferenceDesign ФункцияЭкспортируйте пользовательский исходный проект для своей модели при помощи socExportReferenceDesign функция. Например, для модели под названием soc_image rotation, введите этот код в командной строке MATLAB®.

socExportReferenceDesign('soc_image_rotation')Функция генерирует эти артефакты в текущей папке.

Файлы регистрации плат

Регистрационный файл исходного проекта

Репозиторий IP

Спроектируйте файлы

Ограничительные файлы

Добавьте сгенерированную папку в путь MATLAB. Используйте инструмент HDL Workflow Advisor, чтобы провести вас по шагам для интеграции вашего IP и генерации аппаратных и программных исполняемых файлов для развертывания на устройстве SoC.

Для примера, показывающего полный рабочий процесс на случае только для FPGA, смотрите Экспорт Пользовательский Исходный проект. Если ваша модель включает систему обработки, эти дополнительные шаги требуются при использовании инструмента HDL Workflow Advisor.

В Simulink щелкните правой кнопкой по блоку DUT, который вы хотите интегрировать в исходный проект и выбрать HDL Code> HDL Workflow Advisor, чтобы открыть инструмент HDL Workflow Advisor. В качестве альтернативы используйте hdladvisor (HDL Coder) функция.

На шаге 1.1, набор Target workflow к IP Core Generation и Target platform на платформу, сгенерированную socExportReferenceDesign функция.

Нажмите Run This Task, чтобы запустить задачу Set Target Device and Synthesis Tool.

На шаге 1.3, набор целевой интерфейс путем соединения каждого порта в IP к соответствующему порту в исходном проекте.

Нажмите Run This Task, чтобы запустить задачу Set Target Interface.

Продолжите остающиеся шаги инструмента HDL Workflow Advisor.

Дополнительный: На шаге 4.2 можно принять решение сгенерировать модель программного интерфейса с блоками драйверов ядра IP (требует лицензии Embedded Coder®). Если вы принимаете решение сгенерировать эту модель программного интерфейса, очистите Skip this task под Generate a software interface model with IP core driver blocks for C code generation.

Для получения дополнительной информации смотрите, что раздел, названный ", Генерирует модель программного интерфейса" в Начале работы с Предназначением для Платформы Xilinx Zynq (HDL Coder).

Модель интерфейса сгенерированного программного обеспечения содержит блоки драйверов AXI, которые совпадают с интерфейсом подсистемы DUT. Имя устройства установлено в '/dev/mwipcore' по умолчанию. Измените имя устройства в этих блоках драйверов AXI, чтобы соответствовать в файле дерева устройств, используемом изображением SD-карты.

Существует несколько способов найти имя устройства:

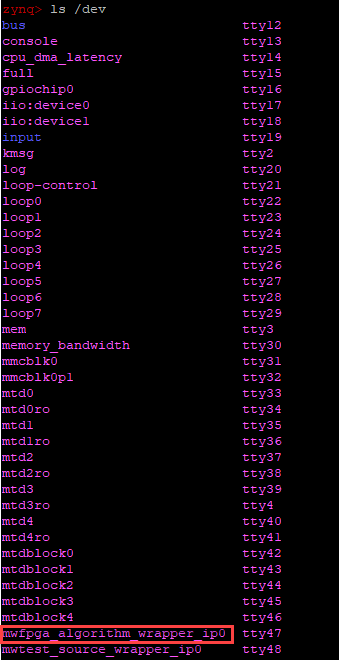

Имя устройства выведено из имени DUT модели SoC. Если вы экспортируете исходный проект с помощью модели SoC с именем DUT, заданным как 'soc_hwsw_stream_fpga/FPGA Algorithm Wrapper', сгенерированным именем устройства в блоках драйверов AXI является '/dev/mwfpga_algorithm_wrapper_ip0'.

Найдите имя устройства в своем изображении операционной системы (OS) после начальной загрузки устройства SoC. Чтобы сделать это, войдите в систему к плате с помощью UART или протоколов SSH, и выполнитесь:

ls/dev

На шаге 4.4, Метод программирования набора Загрузить.

Когда инструмент HDL Workflow Advisor сделан, создав, он возвращает сгенерированный файл потока битов. Программируйте FPGA со сгенерированным файлом потока битов.

Можно теперь развернуть модель программного интерфейса в автономном режиме или использовать его в режиме external mode, чтобы взаимодействовать с устройством SoC. Для примера смотрите раздел, названный "Запуск модель программного интерфейса на оборудовании Zynq ZC702" в Начале работы с Предназначением для Платформы Xilinx Zynq (HDL Coder).