Примечание

Для подготовки плат вам не нужны кабель Ethernet или SD-карта.

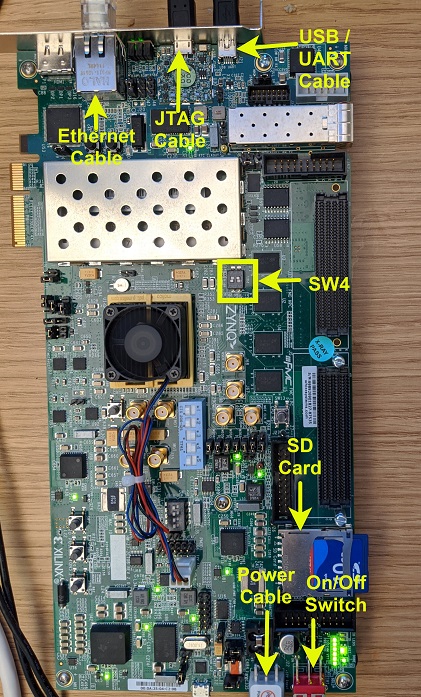

Этот рисунок показывает, как настроить оценочную плату Xilinx® Zynq®-7000 ZC706. Настраивать плату:

Сконфигурируйте SW4 показанный в изображении ниже, и использовать интерфейс Digilent USB-TO-JTAG с помощью следующей таблицы настройки:

| Источник настройки | SW4 переключатель 1 | SW4 переключатель 2 |

| 'none' | 0 | 0 |

| Коннектор кабеля J3 | 1 | 0 |

| Интерфейс Digilent USB-TO-JTAG | 0 | 1 |

| JTAG (управляющий выводом) Заголовок J62 | 1 | 1 |

Включите шнур питания и затем соедините хост - компьютер с платой FPGA при помощи кабеля JTAG как показано в изображении ниже:

Чтобы использовать Ethernet, смотрите, Создают Целевой объект, Который Имеет IP-адрес Интерфейса и Набора Ethernet.

Чтобы узнать больше о конфигурации платы, см. Руководство пользователя оценочной платы Xilinx ZC706.

После того, как вы настроили связь с платой, чтобы запустить рабочий процесс:

Создайте объект рабочего процесса при помощи имени потока битов, которое обеспечивается для платы, как упомянуто в Потоках битов Глубокого обучения Использования (Пакет Поддержки Deep Learning HDL Toolbox для FPGA Xilinx и Устройств SoC).

Чтобы узнать больше о рабочем процессе, смотрите Прототипные Нейронные сети для глубокого обучения на Рабочем процессе SoCs и FPGA.

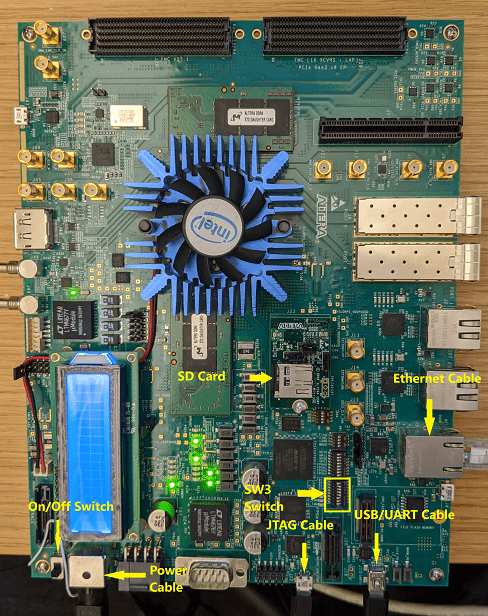

Этот рисунок показывает, как настроить комплект разработчика Intel® Arria® 10 SoC. Настраивать плату:

Включите шнур питания и затем соедините хост - компьютер с платой FPGA при помощи кабеля JTAG.

Задайте настройки переключателя SW3:

| Бит 1 | Бит 2 | Бит 3 | Бит 4 | Бит 5 | Бит 6 | Бит 7 | Бит 8 |

| Off | On | On | On | On | Off | Off | Off |

Соедините две сменных платы DDR4 с пазом плагина памяти.

Чтобы использовать Ethernet, смотрите, Создают Целевой объект, Который Имеет IP-адрес Интерфейса и Набора Ethernet.

Этот рисунок показывает параметры конфигурации для комплекта разработчика Intel Arria 10 SoC.

Чтобы узнать больше о конфигурации платы, см. руководство пользователя Arria 10 SoC Комплекта разработчика.

После того, как вы настроили связь с платой, чтобы запустить рабочий процесс:

Создайте объект рабочего процесса при помощи имени потока битов, которое обеспечивается для платы, как упомянуто в Потоках битов Глубокого обучения Использования (Пакет Поддержки Deep Learning HDL Toolbox для FPGA Intel и Устройств SoC).

Чтобы узнать больше о рабочем процессе, смотрите Прототипные Нейронные сети для глубокого обучения на Рабочем процессе SoCs и FPGA.

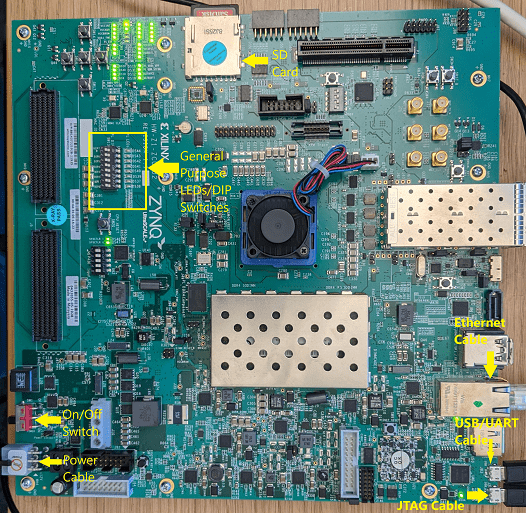

1. Настройте Xilinx Zynq UltraScale + оценочный комплект MPSoC ZCU102 как показано на рисунке ниже:

Устанавливать плату:

Включите шнур питания. Если использование JTAG соединяет плату FPGA с хостом - компьютером с помощью кабеля JTAG. При использовании connect Ethernet плата FPGA к хосту - компьютеру с помощью кабеля Ethernet.

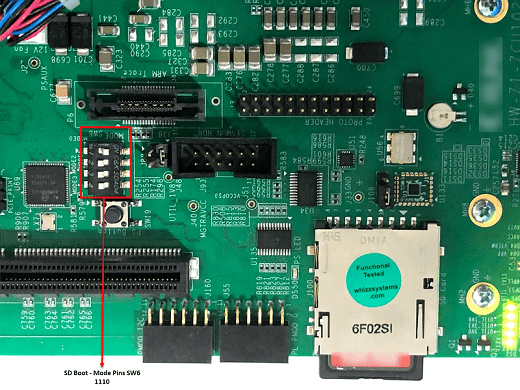

Сконфигурируйте SW6 переключитесь, который показывают в изображении ниже:

Используйте приведенную ниже таблицу настройки, чтобы сконфигурировать настройки переключателя:

| Режим начальной загрузки | Контакты режима [3:0] | SW6 Переключите положение [3:0] |

JTAG | 0, 0, 0, 0 | на, на, на, на |

QSPI32 | 0, 0, 1, 0 | на, на, прочь, на |

SD | 1, 1, 1, 0 | прочь, прочь, прочь, на |

SW6 положением по умолчанию является QSPI32. Для SW6 Dip-переключатель, перемещающий переключатель к ON метка является 0.

Чтобы использовать Ethernet, смотрите, Создают Целевой объект, Который Имеет IP-адрес Интерфейса и Набора Ethernet.

Чтобы узнать больше о настройке оборудования ZCU102, обратитесь к документации Xilinx

После того, как вы настроили связь с платой, чтобы запустить рабочий процесс:

Создайте объект рабочего процесса при помощи имени потока битов, которое обеспечивается для платы, как упомянуто в Потоках битов Глубокого обучения Использования (Пакет Поддержки Deep Learning HDL Toolbox для FPGA Xilinx и Устройств SoC).

Чтобы узнать больше о рабочем процессе, смотрите Прототипные Нейронные сети для глубокого обучения на Рабочем процессе SoCs и FPGA.