Чтобы сгенерировать пользовательский поток битов, чтобы развернуть нейронную сеть для глубокого обучения в ваше целевое устройство, используйте dlhdl.ProcessorConfig объект.

Создайте dlhdl.ProcessorConfig объект.

hPC = dlhdl.ProcessorConfig;

Setup инструмент path к вашему Design Tool. Например, чтобы установить путь к Design Tool Vivado®, введите:

hdlsetuptoolpath('ToolName', 'Xilinx Vivado', 'ToolPath', 'C:\Xilinx\Vivado\2019.2\bin\vivado.bat');

Сгенерируйте пользовательский поток битов.

dlhdl.buildProcessor(hPC);

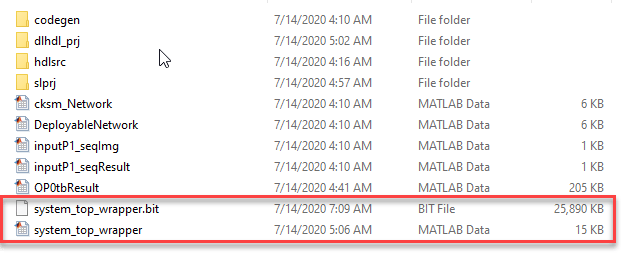

После того, как генерация потока битов завершается, можно определить местоположение файла потока битов в cwd\dlhdl_prj\vivado_ip_prj\vivado_prj.runs\impl_1, где cwd ваша текущая рабочая директория. Именем файла потока битов является system_top_wrapper.bit. Связанный system_top_wrapper.mat файл расположен в верхнем уровне cwd.

Чтобы использовать сгенерированный поток битов для поддерживаемых плат Xilinx®, необходимо скопировать system_top_wrapper.bit и system_top_wrapper.mat файлы к той же папке.

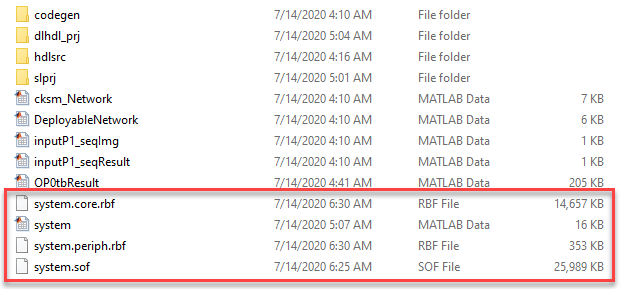

Чтобы использовать сгенерированный поток битов для поддерживаемых плат Intel®, необходимо скопировать system_core.rbf, system.mat, system_periph.rbf, и system.sof файлы к той же папке.

Разверните пользовательский поток битов и нейронную сеть для глубокого обучения к вашему целевому устройству.

hTarget = dlhdl.Target('Xilinx'); snet = alexnet; hW = dlhdl.Workflow('Network',snet,'Bitstream','system_top_wrapper.bit','Target',hTarget); % If your custom bitstream files are in a different folder, use: % hW = dlhdl.Workflow('Network',snet,'Bitstream',... % 'C:\yourfolder\system_top_wrapper.bit','Target',hTarget); hW.compile; hW.deploy;

Использование ресурса потока битов (пакет поддержки Deep Learning HDL Toolbox для FPGA Intel и устройств SoC)

Использование ресурса потока битов (пакет поддержки Deep Learning HDL Toolbox для FPGA Xilinx и устройств SoC)

dlhdl.buildProcessor | dlhdl.ProcessorConfig | dlhdl.Workflow