В этом примере показано, как сгенерировать испытательный стенд HDL и проверить сгенерированный код для простой встречной модели. Чтобы сгенерировать HDL-код для этой модели, смотрите, Генерируют HDL-код из Модели Simulink. Если у вас нет сгенерированного HDL-кода для этой модели, HDL Coder™ запускает генерацию кода прежде, чем сгенерировать испытательный стенд.

Чтобы проверить функциональность HDL-кода для DUT, сгенерируйте испытательный стенд HDL. Испытательный стенд включает:

Данные о стимуле, сгенерированные источниками сигнала, соединенными с сущностью под тестом.

Выходные данные сгенерированы сущностью под тестом. Во время запущенного испытательного стенда эти данные сравниваются с выходными параметрами модели VHDL® для верификации.

Синхронизируйте, сбросьте, и часы позволяют входным параметрам управлять сущностью под тестом.

Инстанцирование компонента сущности под тестом.

Код, чтобы управлять сущностью под тестом и сравнить его выходные параметры с ожидаемыми данными.

Можно симулировать сгенерированный испытательный стенд и файлы скрипта при помощи средства моделирования Mentor Graphics® ModelSim®.

Откройте эту модель, чтобы видеть простой счетчик. Модель подсчитывает от нуля до порогового значения и затем переносится назад, чтобы обнулить. Пороговое значение установлено в 15. Чтобы изменить пороговое значение, измените значение входа к count_threshold порт. Разрешать сигнал задает, рассчитывает ли счетчик вверх или содержит предыдущее значение. Значение 1 указывает, что счетчик рассчитывает вверх постоянно.

Если вам установили HDL Verifier™, можно также проверить сгенерированный HDL-код при помощи этих методов.

| Метод верификации | Для получения дополнительной информации |

|---|---|

| HDL Cosimulation | Cosimulation |

| Испытательный стенд SystemVerilog DPI | Испытательный стенд SystemVerilog DPI |

| FPGA в цикле | FPGA в цикле |

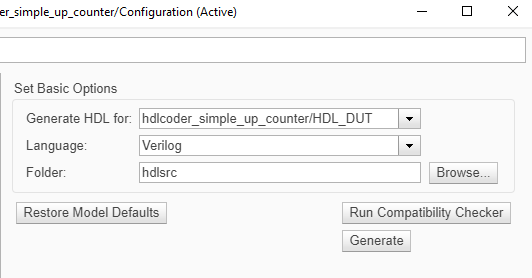

Сгенерируйте код испытательного стенда VHDL или Verilog как применимый. По умолчанию HDL-код и код испытательного стенда записаны в ту же целевую папку hdlsrc относительно текущей папки.

Для встречной модели, HDL_DUT подсистема является DUT. Чтобы сгенерировать испытательный стенд, выберите эту подсистему.

Во вкладке Apps выберите HDL Coder.

Выберите подсистему DUT, HDL_DUT, и убедитесь, что это имя появляется в опции Code for на вкладке HDL Code. Чтобы помнить выбор, прикрепите эту опцию. Нажмите Generate Testbench.

Сгенерировать код испытательного стенда Verilog для встречной модели:

Во вкладке HDL Code нажмите Settings.

В панели HDL Code Generation, для Language, выбирают Verilog.

В HDL Code Generation> панель Test Bench, нажмите Generate Test Bench.

HDL Coder компилирует модель и генерирует испытательный стенд.

Генерация испытательного стенда завершается и отображает это сообщение. Сгенерированные файлы появляются в hdlsrc папка.

### HDL TestBench Generation Complete.

Для встречной модели, hdlsrc папка содержит эти файлы испытательного стенда.

HDL_DUT_tb.vhd: Код испытательного стенда VHDL, содержащий, сгенерировал тестовые и выходные данные. Если вы сгенерировали код испытательного стенда Verilog, сгенерированным файлом является HDL_DUT_tb.v.

HDL_DUT_tb_pkg.vhd: Файл пакета для кода испытательного стенда VHDL. Этот файл не сгенерирован, если вы задали Verilog как выходной язык.

HDL_DUT_tb_compile.do: Скрипт компиляции Mentor Graphics ModelSim (vcom команды). Этот скрипт компилирует и загружает сущность, которая будет протестирована (HDL_DUT.vhd) и код испытательного стенда (HDL_DUT_tb.vhd).

HDL_DUT_tb_sim.do: Скрипт Mentor Graphics ModelSim, чтобы инициализировать средство моделирования, настройте отображения сигнала окна wave и запустите симуляцию.

Чтобы просмотреть сгенерированный код испытательного стенда в Редакторе MATLAB®, дважды кликните HDL_DUT_tb.vhd или HDL_DUT_tb.v файл в текущей папке.

Чтобы проверить результаты симуляции, можно использовать средство моделирования Mentor Graphics ModelSim. Вы, должно быть, уже установили Mentor Graphics ModelSim.

Чтобы открыть средство моделирования, используйте vsim (HDL Verifier) функция. Эта команда показывает, как открыть средство моделирования путем определения пути к исполняемому файлу:

vsim('vsimdir','C:\Program Files\ModelSim\questasim\10.6b\win64\vsim.exe')

Чтобы скомпилировать и запустить симуляцию сгенерированного кода и испытательного стенда модели, используйте сгенерированные скрипты HDL Coder. Для встречной модели запустите эти команды, чтобы скомпилировать и симулировать сгенерированный испытательный стенд для HDL_DUT Подсистема.

Откройте программное обеспечение Mentor Graphics ModelSim и перейдите к папке, которая имеет файлы сгенерированного кода и скрипты.

Используйте сгенерированный скрипт компиляции, чтобы скомпилировать и загрузить сгенерированный код места размещения модели и текста. Для HDL_DUT подсистема, запустите эту команду, чтобы скомпилировать сгенерированный код.

QuestaSim>do HDL_DUT_tb_compile.do

Используйте сгенерированный скрипт симуляции, чтобы выполнить симуляцию. Следующий листинг отображает команду. Можно проигнорировать предупреждающие сообщения. Для HDL_DUT Подсистема, запустите эту команду, чтобы симулировать сгенерированный код.

QuestaSim>do HDL_DUT_tb_sim.do

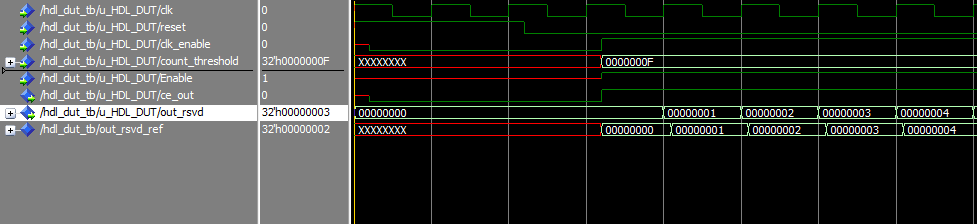

Средство моделирования оптимизирует ваш проект и отображает результаты в окне wave. если вы не видите результаты симуляции, открываете окно wave. Скрипт симуляции отображает вводы и выводы в модели включая сигналы тактовой частоты, сбросы и сигналы разрешения действии по сигналу тактовой частоты в окне wave.

Можно теперь просмотреть сигналы и проверить, что результаты симуляции совпадают с функциональностью первоначального проекта. После проверки, близко средство моделирования Mentor Graphics ModelSim, и затем закрывают открытые файлы в редакторе MATLAB.

Чтобы развернуть сгенерированный код на целевом устройстве FPGA, используйте Simulink® HDL Workflow Advisor. Смотрите генерацию HDL-кода и Синтез FPGA из Модели Simulink.