Закодируйте функцию MATLAB®, которую вы хотите экспортировать в среду SystemVerilog. Для получения информации о кодировании функций MATLAB см. "Функциональные Основы" в документации MATLAB.

Считайте добавление директивы компиляции %#codegen к вашей функции. Эта директива может помочь вам диагностировать и зафиксировать нарушения, которые привели бы к ошибкам во время генерации кода. Смотрите Направляющий % Компиляции #codegen (MATLAB Coder).

В то время как вы кодируете свою функцию, имеете в виду Ограничения, которые описывают различные аспекты генерации компонента DPI, которую необходимо знать. Эти аспекты включают, какие типы данных допустимы, какие файлы сгенерированы, и как разделяемые библиотеки скомпилированы.

В этом примере, функция MATLAB fun.m берет один вход и умножает его на 2. Функция включает директиву компиляции %#codegen.

function y = fun(x) %#codegen y = x * 2;

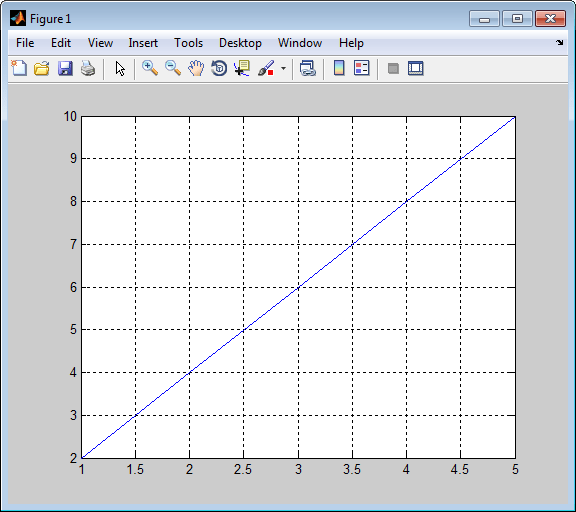

Процесс создания MATLAB включает запись кода, создание испытательного стенда и выполнение испытательного стенда в итеративном процессе. Когда вам удовлетворяют, что ваша функция делает то, что вы предназначаете его, чтобы сделать, продвинуться, чтобы Сгенерировать Компонент SystemVerilog DPI.

Создайте испытательный стенд, чтобы осуществить функцию. В этом примере испытательный стенд применяет тестовый вектор против fun.m и строит выход.

function sample=fun_tb % Testbench should not require input, however you can give an output. % Define a test vector tVecIn = [1,2,3,4,5]; % Exercise fun.m and plot results to make sure function is working correctly tVecOut = arrayfun(@(in) fun(in),tVecIn); plot(tVecIn,tVecOut); grid on; % Get my sample input to use it with function dpigen. sample = tVecIn(1);

Обратите внимание на то, что испытательный стенд не должен иметь входных параметров. Испытательный стенд может векторы нагрузочного теста с помощью файлов MAT или любого другого файла данных, таким образом, это не требует входных параметров.

Выход fun_tb, sample, будет используемым в качестве аргумента входных параметров функции для fun.m во время вызова dpigen, который является, почему это - один элемент. Смотрите Генерируют Компонент SystemVerilog DPI.

fun_tb

ans =

1

Затем сгенерируйте компонент SystemVerilog DPI. Смотрите Генерируют Компонент SystemVerilog DPI.

dpigen ФункцияИспользуйте функцию dpigen сгенерировать компонент DPI. Эта функция имеет несколько дополнительных входных параметров. Как минимум задайте функцию MATLAB, вы хотите сгенерировать компонент для и входные параметры функции. Если вы также хотите сгенерировать испытательный стенд, чтобы осуществить сгенерированный компонент, используйте -testbench опция.

dpigen func -args input_arg -testbench test_bench_name

Задайте входные параметры как требуется функцией. В этом примере, sample скалярное значение, типа double.

sample = 1;

Вызовите функцию генератора компонента DPI:

dpigen fun -args sample -testbench fun_tb

Команда, данная как показано, выполняет следующие задачи:

Генерирует fun_dpi.sv – компонент SystemVerilog для функционального fun.mВходные параметры функции.The для fun.m заданы в sample.

Генерирует fun_dpi_pkg.sv – файл пакета SystemVerilog. Этот файл содержит все импортированные объявления функции.

Создает испытательный стенд для сгенерированного компонента.

Для этого вызова dpigen, MATLAB выводит следующие сообщения:

### Generating DPI Wrapper fun_dpi.c ### Generating DPI Wrapper header file fun_dpi.h ### Generating SystemVerilog module package fun_dpi_pkg.sv ### Generating SystemVerilog module fun_dpi.sv ### Generating makefiles for: fun_dpi ### Compiling the DPI Component ### Generating SystemVerilog test bench fun_tb.sv ### Generating test bench simulation script for Mentor Graphics QuestaSim/Modelsim run_tb_mq.do ### Generating test bench simulation script for Cadence Incisive run_tb_incisive.sh ### Generating test bench simulation script for Cadence Xcelium run_tb_xcelium.sh ### Generating test bench simulation script for Synopsys VCS run_tb_vcs.sh ### Generating test bench simulation script for Vivado Simulator run_tb_vivado.bat

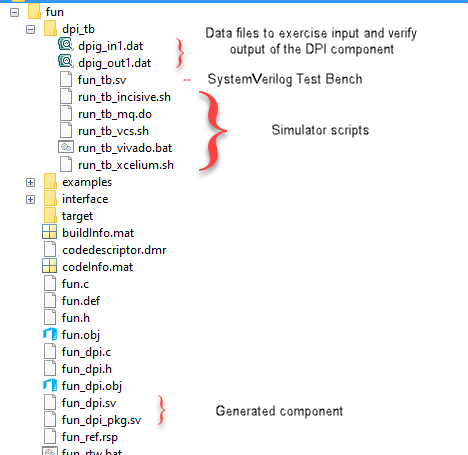

Функция, показанная в предыдущем примере, генерирует следующие папки и файлы:

Исследуйте сгенерированный файл пакета. Отметьте объявления initializeсброс, terminate, и fun функции.

Этот пример показывает код, сгенерированный для fun_dpi_pkg.sv.

// File: C:\fun_example\codegen\dll\fun\fun_dpi_pkg.sv // Created: 2017-12-19 09:18:00 // Generated by MATLAB 9.5 and HDL Verifier 5.4 `timescale 1ns / 1ns package fun_dpi_pkg; // Declare imported C functions import "DPI" function chandle DPI_fun_initialize(input chandle existhandle); import "DPI" function chandle DPI_fun_reset(input chandle objhandle,input real x,output real y); import "DPI" function void DPI_fun(input chandle objhandle,input real x,output real y); import "DPI" function void DPI_fun_terminate(input chandle existhandle); endpackage : fun_dpi_pkg

Исследуйте сгенерированный компонент так, чтобы можно было понять как dpigen функционируйте преобразовал код MATLAB в код SystemVerilog. Для получения дополнительной информации о том, что включает функция, смотрите Сгенерированную Обертку SystemVerilog.

Этот пример показывает код, сгенерированный для fun_dpi.sv.

// File: C:\fun_example\codegen\dll\fun\fun_dpi.sv

// Created: 2017-12-19 09:18:00

// Generated by MATLAB 9.5 and HDL Verifier 5.4

`timescale 1ns / 1ns

import fun_dpi_pkg::*;

module fun_dpi(

input bit clk,

input bit clk_enable,

input bit reset,

input real x,

output real y

);

chandle objhandle=null;

real y_temp;

initial begin

objhandle=DPI_fun_initialize(objhandle);

end

final begin

DPI_fun_terminate(objhandle);

end

always @(posedge clk or posedge reset) begin

if(reset== 1'b1) begin

objhandle=DPI_fun_reset(objhandle,x,y_temp);

y<=y_temp;

end

else if(clk_enable) begin

DPI_fun(objhandle,x,y_temp);

y<=y_temp;

end

end

endmoduleИсследуйте сгенерированный испытательный стенд, таким образом, вы видите как функциональный dpigen созданный этот испытательный стенд из кода MATLAB. Для получения дополнительной информации о сгенерированном испытательном стенде смотрите Сгенерированный Испытательный стенд.

Этот пример показывает код, сгенерированный для fun_tb.sv.

// File: C:\fun_example\codegen\dll\fun\dpi_tb\fun_tb.sv

// Created: 2017-12-19 09:18:13

// Generated by MATLAB 9.5 and HDL Verifier 5.4

`timescale 1ns / 1ns

module fun_tb;

real x;

real y_ref;

real y_read;

real y;

// File Handles

integer fid_x;

integer fid_y;

// Other test bench variables

bit clk;

bit clk_enable;

bit reset;

integer fscanf_status;

reg testFailure;

reg tbDone;

bit[63:0] real_bit64;

bit[31:0] shortreal_bit64;

parameter CLOCK_PERIOD= 10;

parameter CLOCK_HOLD= 2;

parameter RESET_LEN= 2*CLOCK_PERIOD+CLOCK_HOLD;

// Initialize variables

initial begin

clk = 1;

clk_enable = 0;

testFailure = 0;

tbDone = 0;

reset = 1;

fid_x = $fopen("dpig_in1.dat","r");

fid_y = $fopen("dpig_out1.dat","r");

// Initialize multirate counters

#RESET_LEN reset = 0;

end

// Clock

always #(CLOCK_PERIOD/2) clk = ~ clk;

always@(posedge clk) begin

if (reset == 0) begin

#CLOCK_HOLD

clk_enable <= 1;

fscanf_status = $fscanf(fid_x, "%h", real_bit64);

x = $bitstoreal(real_bit64);

if ($feof(fid_x))

tbDone = 1;

fscanf_status = $fscanf(fid_y, "%h", real_bit64);

y_read = $bitstoreal(real_bit64);

if ($feof(fid_y))

tbDone = 1;

y_ref <= y_read;

if (clk_enable == 1) begin

assert ( ((y_ref - y) < 2.22045e-16) && ((y_ref - y) > -2.22045e-16) ) else begin

testFailure = 1;

$display("ERROR in output y_ref at time %0t :", $time);

$display("Expected %e; Actual %e; Difference %e", y_ref, y, y_ref-y);

end

if (tbDone == 1) begin

if (testFailure == 0)

$display("**************TEST COMPLETED (PASSED)**************");

else

$display("**************TEST COMPLETED (FAILED)**************");

$finish;

end

end

end

end

// Instantiate DUT

fun_dpi u_fun_dpi(

.clk(clk),

.clk_enable(clk_enable),

.reset(reset),

.x(x),

.y(y)

);

endmodule

Затем запустите сгенерированный испытательный стенд в симуляторе HDL. Смотрите Запуск Сгенерированный Испытательный стенд в симуляторе HDL. Если вы планируете портировать и дополнительный испытательный стенд компонента от Windows® до Linux®, смотрите Порт Сгенерированный и Испытательный стенд Компонента к Linux.

Запустите испытательный стенд в средствах моделирования ModelSim и QuestaSim

Запустите испытательный стенд в остром средстве моделирования

Этот раздел включает инструкции для выполнения сгенерированного испытательного стенда в одном из поддерживаемых симуляторов HDL: Наставник Graphics® ModelSim® и Questa®Sim, Cadence Incisive® и Synopsys® VCS®. Возможно, что этот код будет работать в других (неподдерживаемых) симуляторах HDL, но это не гарантируется.

Выберите рабочий процесс для своего симулятора HDL.

Запустите ModelSim или QuestaSim в режиме GUI.

Измените свой текущий каталог в dpi_tb папка в соответствии с директорией генерации кода в MATLAB.

Введите следующую команду в интерпретатор, чтобы запустить вашу симуляцию:

do run_tb_mq.do

Этот сгенерированный скрипт содержит имя и испытательного стенда компонента и инструкции к симулятору HDL для выполнения испытательного стенда.

Когда симуляция заканчивается, необходимо видеть следующий текст, отображенный в консоли:

**************TEST COMPLETED (PASSED)**************

Это сообщение говорит вам, что испытательный стенд был запущен против сгенерированного компонента успешно.

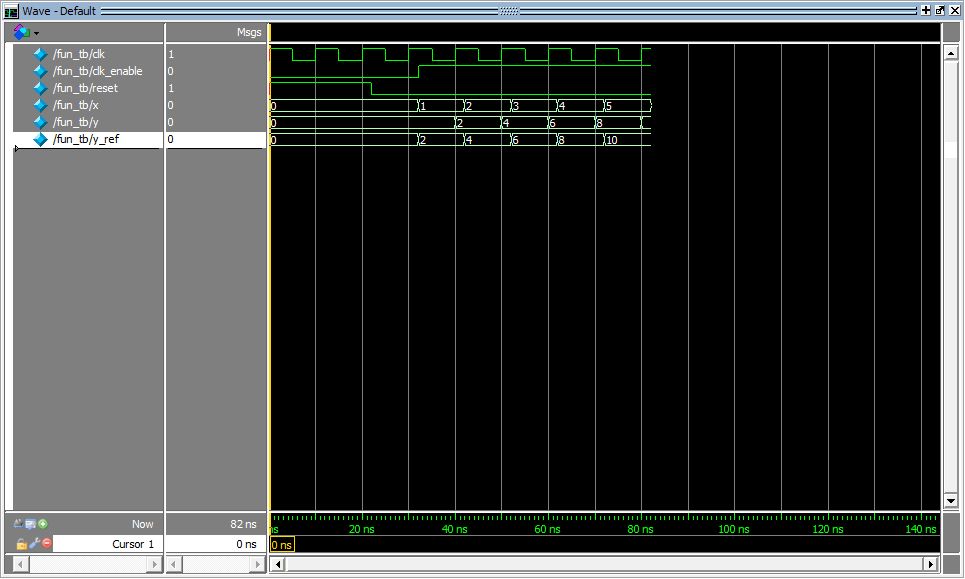

Следующее изображение формы волны из этого примера демонстрирует, что сгенерированный испытательный стенд был успешно осуществлен в симуляторе HDL.

Затем импортируйте свой компонент. Смотрите Использование Сгенерированные Функции DPI в SystemVerilog.

Запустите Incisive®.

Запустите свой терминальный интерпретатор.

Измените текущий каталог в dpi_tb в соответствии с директорией генерации кода в MATLAB.

Введите следующую команду в интерпретатор, чтобы запустить симуляцию:

sh run_tb_ncsim.sh

Этот сгенерированный скрипт содержит имя и испытательного стенда компонента и инструкции к симулятору HDL для выполнения испытательного стенда.

Когда симуляция заканчивается, необходимо видеть следующий текст, отображенный в консоли:

**************TEST COMPLETED (PASSED)**************

Это сообщение говорит вам, что испытательный стенд был запущен против сгенерированного компонента успешно.

Запустите VCS.

Запустите свой терминальный интерпретатор.

Измените текущий каталог в dpi_tb в соответствии с директорией генерации кода в MATLAB.

Введите следующую команду в свой интерпретатор, чтобы запустить симуляцию:

sh run_tb_vcs.sh

Этот сгенерированный скрипт содержит имя и испытательного стенда компонента и инструкции к симулятору HDL для выполнения испытательного стенда.

Когда симуляция заканчивается, необходимо видеть следующий текст, отображенный в консоли:

**************TEST COMPLETED (PASSED)**************

Это сообщение говорит вам, что испытательный стенд был запущен против сгенерированного компонента успешно.

Чтобы использовать сгенерированный компонент DPI в испытательном стенде SystemVerilog, сначала необходимо включать файл пакета в среду SystemVerilog. Это будет иметь функции DPI в наличии в рамках вашего модуля SystemVerilog. Затем необходимо вызвать сгенерированные функции. Когда вы компилируете код SystemVerilog, который содержит импортированные сгенерированные функции, используйте учитывающий DPI компилятор SystemVerilog и задайте компонент и имена файлов пакета наряду с кодом SystemVerilog.

Следующий пример демонстрирует добавление сгенерированного компонента DPI для fun.m к модулю SystemVerilog.

Вызовите Initialize функция.

DPI_fun_initialize();

Вызовите функцию, сгенерированную от fun.m.

DPI_fun(x,y);

Можно теперь изменить сгенерированный код по мере необходимости.

module test_twofun_tb; initial begin DPI_fun_initialize(); end always@(posedge clk) begin #1 DPI_fun(x,y); end

Чтобы портировать и дополнительный испытательный стенд компонента от операционной системы Windows до операционной системы Linux, следуйте этим инструкциям.

Примечание

У вас должна быть лицензия Embedded Coder® на порт Windows to Linux. Несмотря на то, что возможно, что порт будет работать без лицензии Embedded Coder, то использование не поддерживается.

Создайте config MATLAB Coder™ объект. Измените целевой тип устройства HW в LP64 для операционной системы Linux.

cfg=coder.config('dll');

cfg.HardwareImplementation.TargetHWDeviceType='Generic->64-bit Embedded Processor (LP64)';

Запуститесь dpigen команда с помощью опции -config использовать config возразите, что вы создали на шаге 1. Используйте опцию -c так, чтобы функция dpigen генерирует только код. Например:

dpigen -config cfg DataTypes.m -args InputSample -c

Чтобы сгенерировать zip-файл к порту к Linux, измените папку в исходную папку (где buildInfo.mat файл сгенерирован), и выполните следующие команды в командной строке:

load buildInfo buildInfo.packNGo()

Чтобы скопировать файл для портирования, возвратитесь к папке верхнего уровня. Найдите zip-файл сгенерированным на предыдущем шаге (то же имя как функция MATLAB). Скопируйте zip-файл в машину Linux.

Разархивируйте файл с помощью -j опция, чтобы извлечь все файлы со сглаженной структурой папок. Можно разархивировать в любую папку. Например:

unzip -j DataTypes.zip

Скопируйте этот типовой скрипт make-файла в пустой файл:

SRC=$(wildcard *.c) OBJ=$(SRC:.c=.o) SHARE_LIB_NAME=DPI_Component.so all: $(SRC) $(SHARE_LIB_NAME) @echo "### Successfully generated all binary outputs." $(SHARE_LIB_NAME): $(OBJ) gcc -shared -lm $(OBJ) -o $@ .c.o: gcc -c -fPIC -Wall -pedantic -Wno-long-long -fwrapv -O0 $< -o $@

Замените DPI_Component.so с именем разделяемой библиотеки вы хотите создать.

Сохраните скрипт как Porting_DPIC.mk в папке, где zip-файлы были извлечены.

Создайте разделяемую библиотеку со следующей командой:

make -f Porting_DPIC.mk all

Чтобы использовать сгенерированный компонент с SystemVerilog, смотрите Использование Сгенерированные Функции DPI в SystemVerilog.

(Необязательно) Запускает испытательный стенд, который был автоматически сгенерирован в Windows.

Скопируйте содержимое dpi_tb папка от хост-машины Windows до Linux предназначается для машины.

Запустите испытательный стенд.

Чтобы запустить испытательный стенд в симуляторе HDL, смотрите Запуск Сгенерированный Испытательный стенд в симуляторе HDL.