Представление времени симуляции значительно отличается между симулятором HDL и Simulink®. Каждое приложение имеет свой собственный механизм синхронизации, и программное обеспечение верификации должно синхронизировать времена симуляции между двумя.

В симуляторе HDL модуль времени симуляции упоминается как метка деления. Длительность метки деления задана пределом разрешения симулятора HDL. Предел разрешения по умолчанию составляет 1 нс, но может варьироваться в зависимости от средства моделирования.

ModelSim® Users:

Чтобы определить текущий предел разрешения ModelSim, введите echo $resolution или report simulator state в подсказке ModelSim. Можно заменить предел разрешения по умолчанию путем определения -t опция на командной строке ModelSim, или путем выбора различного Разрешения Средства моделирования в диалоговом окне ModelSim Simulate. Доступные разрешения в ModelSim 1x, 10x, или 100x в модулях фс, PS, не уточнено, нас, мс, или секунда. См. документацию ModelSim для получения дополнительной информации.

Incisive® Users:

Чтобы определить текущий предел разрешения симулятора HDL, введите echo $timescale в подсказке симулятора HDL. См. документацию симулятора HDL для получения дополнительной информации.

Simulink обеспечивает время симуляции как значение с двойной точностью, масштабируемое к секундам. Это представление вмещает моделирование и непрерывных и дискретных систем.

Отношение между Simulink и синхронизацией симулятора HDL влияет на следующие аспекты симуляции:

Общее время симуляции

Шаги расчета Input port

Шаги расчета выходного порта

Синхронизируйте периоды

Во время запущенной симуляции Simulink передает текущее время симуляции к симулятору HDL на каждом промежуточном шаге. (Промежуточный шаг соответствует хиту шага расчета Simulink. На каждый промежуточный шаг новые значения применяются во входных портах, или выходные порты производятся.)

Чтобы принести симулятор HDL, актуальный с Simulink во время cosimulation, необходимо преобразовать, произвел время Simulink ко времени симулятора HDL (метки деления), и позвольте симулятору HDL запускаться для вычисленного количества меток деления.

Различия в представлении времени симуляции могут быть согласованы в одном из двух способов использовать интерфейс HDL Verifier™:

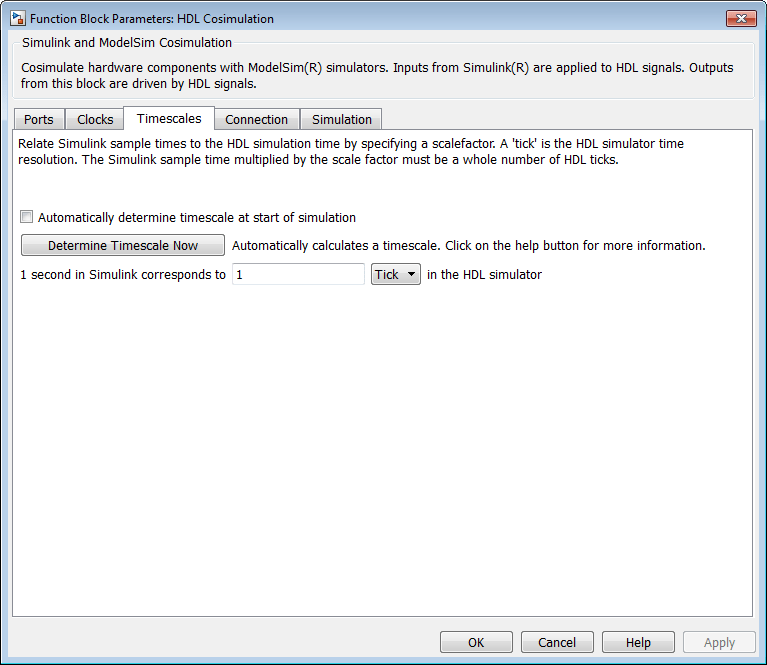

Путем определения временной зависимости вручную (с панелью Timescales)

Когда вы задаете отношение вручную, вы определяете, сколько фемтосекунд, пикосекунд, наносекунды, микросекунды, миллисекунды, секунды или метки деления в симуляторе HDL представляет 1 секунду в Simulink.

Позволяя HDL Verifier задать масштаб времени (с панелью Timescales)

Когда вы позволяете программному обеспечению задавать временную зависимость, оно пытается установиться коэффициент масштаба времени между симулятором HDL и Simulink, чтобы быть максимально близким к 1 секунде в симуляторе HDL = 1 секунда в Simulink. Если эта установка не возможна, HDL Verifier пытается установить уровень сигнала на порте модели Simulink к самому низкому количеству меток деления симулятора HDL.

Панель Timescales диалогового окна параметров блоков HDL Cosimulation задает соответствие между одной секундой времени Simulink и некоторым количеством времени симулятора HDL. Это количество времени симулятора HDL может быть описано одним из следующих способов:

В относительном выражении (i.e., как некоторое количество меток деления симулятора HDL). В этом случае cosimulation, как говорят, действует в относительном режиме синхронизации. Значения по умолчанию блока HDL Cosimulation к относительному режиму синхронизации для cosimulation. Для больше на относительном режиме синхронизации, смотрите Относительный Режим Синхронизации.

В абсолютных единицах (таких как миллисекунды или наносекунды). В этом случае cosimulation, как говорят, действует в абсолютном режиме синхронизации. Для больше на абсолютном режиме синхронизации, смотрите Абсолютный Режим Синхронизации.

Панель Timescales позволяет вам выбрать оптимальную временную зависимость между Simulink и симулятором HDL, или путем ввода эквивалентного симулятора HDL или позволяя HDL Verifier вычислить масштаб времени для вас.

Можно принять решение иметь HDL Verifier, вычисляют масштаб времени, в то время как вы устанавливаете параметры на диалоговом окне блока путем нажатия на опцию Timescale, затем нажатие по Determine Timescale Now, или у вас может быть HDL Verifier, вычисляют масштаб времени, когда симуляция начинается путем выбора Automatically determine timescale at start of simulation.

Следующий рисунок показывает настройки по умолчанию панели Timescales (показанный пример для использования с ModelSim).

Для получения инструкций по установке режима синхронизации или вручную или с диалоговым окном Timescales, смотрите панель Timescales в ссылке блока HDL Cosimulation.

Чтобы иметь программное обеспечение HDL Verifier вычисляют временную зависимость для вас:

Запустите симулятор HDL. Программное обеспечение HDL Verifier может получить предел разрешения симулятора HDL только, когда то средство моделирования запускается.

Примите решение иметь программное обеспечение HDL Verifier, предлагают масштаб времени, сразу, или вычисляют масштаб времени, когда вы запускаете симуляцию Simulink.

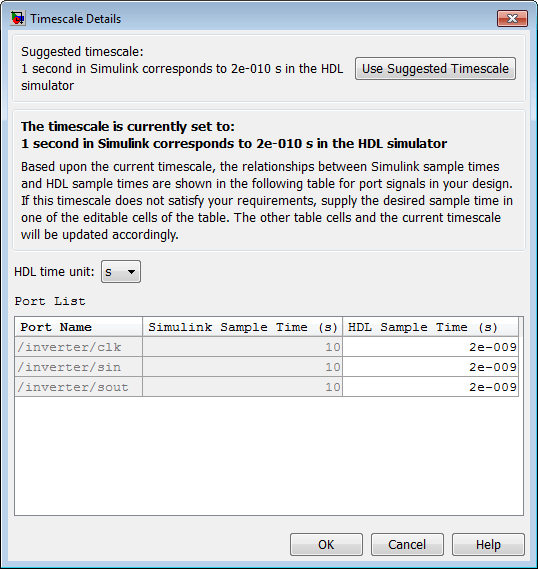

Чтобы выполнить вычисление, в то время как вы конфигурируете блок на вкладке Timescale, нажимают Determine Timescale Now. Программное обеспечение соединяет Simulink с симулятором HDL так, чтобы Simulink мог использовать разрешение симулятора HDL, чтобы вычислить лучший масштаб времени. Ссылка затем отображает те результаты вам в диалоговом окне Timescale Details.

Примечание

Для результатов отобразиться, убедитесь, что симулятор HDL запускается, и проект загружается для cosimulation. Симуляция не должна запускаться.

Можно принять предложенный масштаб времени или изменить список портов непосредственно:

Чтобы вернуться к первоначально расчетным настройкам, нажмите Use Suggested Timescale.

Чтобы просмотреть шаги расчета для всех портов в проекте HDL, выберите Show all ports and clocks.

Чтобы выполнить вычисление, когда симуляция начнется, выберите Automatically determine timescale at start of simulation и нажмите Apply. Вы получаете то же диалоговое окно Timescale Details, когда симуляция запускается в Simulink.

Примечание

Для результатов отобразиться, убедитесь, что симулятор HDL запускается, и проект загружается для cosimulation. Симуляция не должна запускаться.

Программное обеспечение HDL Verifier анализирует все часы и уровни сигнала порта от блока HDL Cosimulation, когда программное обеспечение вычисляет масштабный коэффициент.

Примечание

Программное обеспечение HDL Verifier не может автоматически вычислить демонстрационный масштаб времени на основе никаких сигналов, управляемых через команды Tcl или в симуляторе HDL. Программное обеспечение ссылки не может выполнить такие вычисления, потому что оно не может знать уровни этих сигналов.

Программное обеспечение ссылки возвращает частоту дискретизации или в секундах или в метках деления:

Если результаты находятся в секундах, то программное обеспечение ссылки смогло разрешить различия в синхронизации в пользу точности (абсолютное время).

Если результаты находятся в метках деления, то программное обеспечение ссылки лучше всего смогло разрешить различия в синхронизации в пользу КПД (относительное время).

Каждый раз, когда вы выбираете Determine Timescale Now или Automatically determine timescale at start of simulation, интерактивное отображение открывается. Это отображение объясняет результаты вычислений масштаба времени. Если программное обеспечение ссылки не может вычислить масштаб времени для данных шагов расчета, настроить ваши шаги расчета в Port List.

Нажмите Apply, чтобы фиксировать ваши изменения.

Примечание

HDL Verifier не поддерживает масштабы времени, вычисленные автоматически от основанных на системе координат сигналов.

Относительный режим синхронизации задает следующее взаимно-однозначное соответствие между временем симуляции в Simulink и симулятором HDL:

Одна секунда в Simulink соответствует меткам деления N в симуляторе HDL, где N масштабный коэффициент. |

Это соответствие содержит независимо от разрешения синхронизации симулятора HDL.

Следующий псевдокод показывает, как единицы измерения времени Simulink преобразованы в метки деления симулятора HDL:

InTicks = N * tInSecs

где InTicks время симулятора HDL в метках деления, tInSecs время Simulink в секундах и N масштабный коэффициент.

Значения по умолчанию блока HDL Cosimulation к относительному режиму синхронизации, с масштабным коэффициентом 1. Таким образом 1 второй Simulink соответствует 1 метке деления в симуляторе HDL. В случае по умолчанию:

Если общее время симуляции в Simulink задано как N секунды, затем симуляция HDL запустится для точно N метки деления (т.е. N не уточнено в пределе разрешения по умолчанию).

Точно так же, если Simulink вычислит шаг расчета входного порта блока HDL Cosimulation как секунды Tsi, новые значения будут депонированы на входном порте HDL в точных множителях меток деления Tsi. Если выходной порт будет иметь явным образом заданный шаг расчета секунд Цо, значения будут считаны из симулятора HDL во множителях меток деления Цо.

Чтобы изучить, как относительный режим синхронизации действует, анализ cosimulation следует из следующей модели в качестве примера.

Абсолютный режим синхронизации позволяет вам задать временную зависимость между Simulink и симулятором HDL в терминах абсолютных единиц измерения времени и масштабного коэффициента:

| Одна секунда в Simulink соответствует (N * Tu) секундам в симуляторе HDL, где Tu является абсолютной единицей измерения времени (например, мс, не уточнено, и т.д.), и N является масштабным коэффициентом. |

В абсолютном режиме синхронизации все шаги расчета и периоды часов в Simulink квантуются к меткам деления симулятора HDL. Следующий псевдокод иллюстрирует преобразование:

tInTicks = tInSecs * (tScale / tRL)

где:

tInTicks время симулятора HDL в метках деления.

tInSecs время Simulink в секундах.

tScale установка масштаба времени (модуль и масштабный коэффициент) выбранный в панели Timescales блока HDL Cosimulation.

tRL предел разрешения симулятора HDL.

Например, учитывая установку панели Timescales 1 с и предел разрешения симулятора HDL 1 нс, шаг расчета выходного порта 12 нс был бы преобразован в метки деления можно следующим образом:

tInTicks = 12ns * (1s / 1ns) = 12

Чтобы сконфигурировать параметры Масштабов времени для абсолютного режима синхронизации, вы выбираете модуль абсолютного времени, которое соответствует второму Simulink, а не selectingTick.

Чтобы изучить операцию абсолютного режима синхронизации, вы будете снова считать модель в качестве примера обсужденной в Операции Относительного Режима Синхронизации. Предположим, что модель реконфигурирована можно следующим образом:

Параметры симуляции в Simulink:

Параметры Timescale: 1 s из Simulink время соответствует 1 s из времени симулятора HDL.

Общее время симуляции: 60e-9 s (60ns)

Input port (/inverter/inportРазмер шага: 24e-9 s (24 ns)

Выходной порт (/inverter/outportРазмер шага: 12e-9 s (12 ns)

Часы (inverter/clk) период: 10e-9 s (10 ns)

Предел разрешения симулятора HDL: 1 ns

Учитывая эти параметры симуляции, программное обеспечение Simulink будет cosimulate с симулятором HDL для 60 нс, во время которых Simulink будет производить входные параметры в интервалы 24 нс, обновлять выходные параметры с промежутками в 12 нс и управлять часами с промежутками в 10 нс.

Следующий рисунок показывает окно ModelSim wave после запущенного cosimulation.

При установке режима масштаба времени вы, возможно, должны выбрать свою установку на основе следующих факторов.

Следующие ограничения применяются к использованию абсолютных и относительных режимов синхронизации:

Когда несколько блоков HDL Cosimulation в модели связываются с одним экземпляром симулятора HDL, все блоки HDL Cosimulation должны иметь те же настройки панели Timescales.

Если вы изменяете настройки панели Timescales в блоке HDL Cosimulation между последовательными запусками cosimulation, необходимо перезапустить симуляцию в симуляторе HDL.

Если вы зададите шаг расчета Simulink, которого нельзя выразить в целом количество меток деления HDL, вы получите ошибку.

При использовании периодов времени нецелого числа симулятор HDL не может представлять такое бесконечно повторяющееся значение. Таким образом, средство моделирования обрезает период времени, но это делает так по-другому, чем, как Simulink обрезает значение, и эти два периода времени больше не совпадают.

Следующий пример демонстрирует, как установить временную зависимость в следующем сценарии: вы хотите использовать период расчета в Simulink, который соответствует периоду времени нецелого числа.

Ключевая идея здесь состоит в том, что необходимо всегда мочь связать время Simulink с меткой деления HDL. Метка деления HDL является самым прекрасным интервалом времени, который распознает симулятор HDL; для ModelSim метка деления по умолчанию составляет 1 нс, но это может быть сделано столь же точным как 1 фс.

Однако сигнал на 3 Гц на самом деле имеет период 333,33333333333... мс, который не является допустимым периодом метки деления для симулятора HDL. Симулятор HDL обрежет такие числа. Но Simulink не принимает то же решение; таким образом, для cosimulation, где вы пытаетесь сохранить два независимых средства моделирования в синхронизации, вы ничего не должны принимать. Вместо этого необходимо решить, удобно ли обрезать или вокруг номера.

Поэтому решение состоит в том, чтобы "привязать" или шаг расчета Simulink или шаг расчета HDL (через масштаб времени) к верным номерам. Существуют бесконечные возможности, но здесь некоторые возможные способы выполнить привязку:

Измените шаги расчета Simulink с 1/3 секунды до 0,33333 секунд и установите масштаб времени блока cosimulation на '1 секунду в Simulink = 1 секунда в симуляторе HDL'. Если вы задаете часы в блоке HDL Cosimulation панель Clocks, ее период должен составить 0,33333 секунды.

Сохраните шаги расчета Simulink в 1/3 секунду. и 1 секунда в Simulink = 6 меток деления в симуляторе HDL.

Если вы задаете часы в блоке HDL Cosimulation панель Clocks, ее период должен быть 1/3. Кратко, эта спецификация говорит Simulink заставлять каждый шаг расчета Simulink соответствовать каждому (1/3*6) = 2 метки деления, независимо от разрешения времени HDL.

Если ваше разрешение симулятора HDL по умолчанию составляет 1 нс, который означает, что ваши шаги расчета HDL составляют каждые 2 нс. Этот шаг расчета будет работать способом так, чтобы для каждого шага расчета Simulink был соответствующий шаг расчета HDL.

Однако Simulink думает в терминах 1/3 периодов секунды и HDL в терминах периодов на 2 нс. Таким образом вы могли запутаться во время отладки. Если вы хотите, чтобы это совпадало с действительным периодом (такой относительно 5 мест, i.e. 333,33 мс), можно следовать следующей перечисленной опции.

Сохраните шаги расчета Simulink в 1/3 секунду и 1 секунду в Simulink = 0.99999e9 метки деления в симуляторе HDL. Если вы задаете часы в блоке HDL Cosimulation панель Clocks, ее период должен быть 1/3.

В общем случае Simulink обрабатывает шаг расчета для портов блока HDL Cosimulation можно следующим образом:

Если входной порт соединяется с сигналом, который имеет явный шаг расчета, на основе прямого распространения, Simulink применяет тот уровень к тому входному порту.

Если входной порт соединяется с сигналом, который не имеет явного шага расчета, Simulink присваивает шаг расчета, который равен наименьшему общему кратному (LCM) всех идентифицированных шагов расчета входного порта для модели.

После того, как Simulink устанавливает периоды расчета входного порта, он применяет заданные пользователями выходные шаги расчета ко всем выходным портам. Шаги расчета должны быть явным образом заданы для всех выходных портов.

Если вы разрабатываете модель для cosimulation в относительном режиме синхронизации, рассматриваете следующую инструкцию по шагу расчета:

Задайте выходной шаг расчета для блока HDL Cosimulation как целочисленное кратное предел разрешения, заданный в симуляторе HDL. Используйте команду симулятора HDL report simulator state проверять предел разрешения загруженной модели. Если предел разрешения симулятора HDL составляет 1 нс, и вы задаете выходной шаг расчета блока как 20, Simulink взаимодействует с симулятором HDL каждые 20 нс. |