Если у вас есть лицензия HDL Coder™, можно сгенерировать HDL-код из модели Simscape™ для развертывания на платформы FPGA с помощью HDL Workflow Advisor Simscape. HDL Workflow Advisor Simscape генерирует реализацию Simulink® вашей модели Simscape, затем преобразует модель Simulink в HDL-код с помощью HDL Coder. Преобразование вашей модели Simscape к HDL-коду позволяет вам:

Ускорьте симуляцию физических систем при помощи оптимизированной реализации моделей Simscape

Модели быстрого прототипирования с помощью реконфигурируемости и возможностей параллелизма FPGA

Симулируйте реализацию HDL в режиме реального времени с помощью оборудования в цикле (HIL) симуляция

Преобразуйте модель Simscape в HDL-код с помощью HDL Workflow Advisor Simscape путем выполнения этих шагов.

Сгенерируйте базовые результаты для своей модели Simscape.

Убедитесь, что модель содержит только линейный или переключила линейные блоки при помощи simscape.findNonlinearBlocks функция.

Убедитесь, что результаты симуляции модели совпадают с базовыми результатами.

Сконфигурируйте сеть Simscape для симуляции в реальном времени и генерации HDL-кода:

Добавьте блоки, которые позволяют вам контролировать прогресс рабочего процесса HDL в терминах времени симуляции.

Отобразите информацию о шаге расчета.

Сконфигурируйте сеть Simscape для фиксированного шага, симуляции фиксированных затрат.

Убедитесь, что результаты симуляции дискретной модели совпадают с базовыми результатами.

Запустите задачи HDL Workflow Advisor Simscape при помощи sschdladvisor (HDL Coder) функция. HDL Workflow Advisor:

Проверки на совместимость генерации HDL-кода путем гарантирования, что модель содержит только линейный и переключила линейные блоки и сконфигурированы для симуляции в реальном времени.

Коэффициенты пространства состояний извлечений для сети Simscape.

Генерирует совместимую с генерацией HDL-кода реализацию сети Simscape.

Убедитесь, что результаты симуляции от совместимой с генерацией HDL-кода реализации совпадают с базовыми результатами.

Сгенерируйте HDL-код:

Запуститесь hdlsetup (HDL Coder) функция. hdlsetup функция конфигурирует решатель фиксированного шага для генерации HDL-кода и указывает, что симуляция запускается и времена остановки.

Сохраните параметры модели и настройки генерации модели валидации.

Сгенерируйте код с помощью makehdl функция.

Прежде, чем запустить HDL Workflow Advisor Simscape, сконфигурируйте свою сеть, чтобы исключить:

События

Графики режима

Задержки

Enabled параметры времени выполнения

Периодические источники

Нелинейность, которая следует из сетевого соединения — Если ваша модель действительно содержит нелинейность этого вида, sschdladvisor функция может запустить все задачи к завершению, но генерирует нулевое значение выход.

В этом примере показано, как преобразовать вашу модель Simscape в HDL-код с помощью HDL Workflow Advisor Simscape. Чтобы сконфигурировать вашу сеть Simscape и модель Simulink для симуляции в реальном времени и генерации HDL-кода, смотрите Подготовку Модели. Чтобы открыть версию модели, которая уже подготовлена к использованию HDL Workflow Advisor Simscape, смотрите, Генерируют HDL-код при помощи HDL Workflow Advisor Simscape.

Подготовить вашу модель Simscape к развертыванию FPGA:

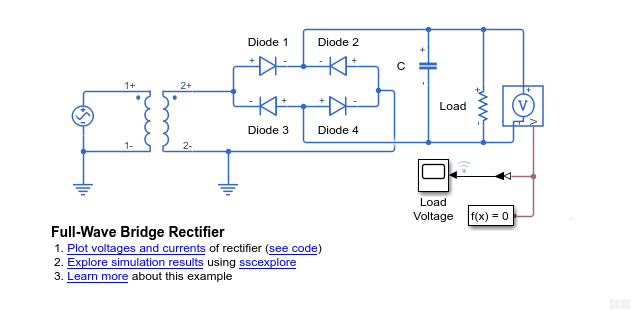

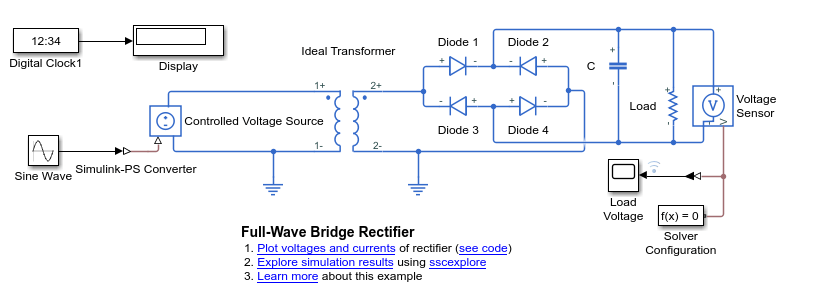

Откройте ssc_bridge_rectifier модель и показывает скрытые имена блока. В командной строке MATLAB® войти

baselineModel = 'ssc_bridge_rectifier'; load_system(baselineModel) set_param(baselineModel,'HideAutomaticNames','off') open_system(baselineModel)

Чтобы сравнить базовые результаты симуляции с последующими итерациями, удалите ограничение точки данных на блок Scope помеченный блок Load Voltage scope и получите сигнал что входные данные с блоком Scope путем включения регистрации данных Инспектору Данных моделирования для.

Откройте блок Scope. Нажмите View> Configuration Properties. На вкладке Logging очистите Limit data points to last.

Щелкните правой кнопкой по связи с блоком Scope и выберите Log selected signals. Значок логгирования![]() появляется выше сигнала.

появляется выше сигнала.

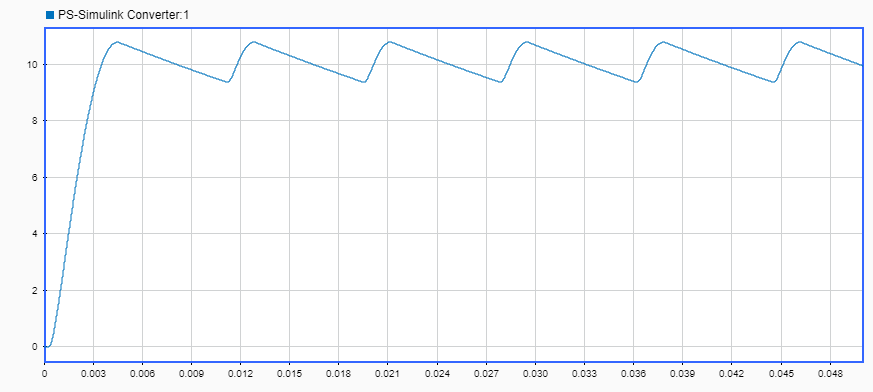

Симулируйте модель и просмотрите результаты в Инспекторе Данных моделирования.

%% Simulate baseline model sim(baselineModel) %% Get Simulation Data Inspector run IDs for runIDs = Simulink.sdi.getAllRunIDs; runID = runIDs(end); run = Simulink.sdi.getRun(runID); signal1 = run.getSignalByIndex(1); % run.signalCount signal1.checked = true; Simulink.sdi.view

По мере необходимости нажмите клавишу "Пробел" на своей клавиатуре, чтобы соответствовать Инспектору Данных моделирования график просмотреть.

Базовая симуляция возвращает ожидаемые результаты для двухполупериодного напряжения загрузки мостового выпрямителя.

Прежде, чем запустить советника, идентифицируйте и замените блоки, которые заставляют вашу сеть быть нелинейной. Чтобы идентифицировать блоки, используйте simcape.findNonlearBlocks функция.

simscape.findNonlinearBlocks(baselineModel)

Found network that contains nonlinear equations in the following blocks:

'ssc_bridge_rectifier/AC Voltage Source'

The number of linear or switched linear networks in the model is 0.

The number of nonlinear networks in the model is 1.

ans =

1×1 cell array

{'ssc_bridge_rectifier/AC Voltage Source'}Модель содержит блок AC Voltage Source, периодический источник, который дает к нелинейным уравнениям.

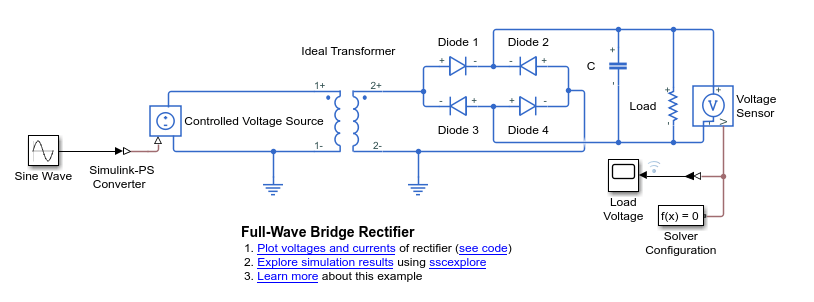

Можно заменить периодический источник на блок Controlled Voltage Source в сети Simscape с блоком Sine Wave вне сети.

Удалите блок AC Voltage Source.

Добавьте блок Sine Wave из библиотеки Simulink> Sources.

Добавьте блок Simulink-PS Converter из библиотеки Simscape> Utilities.

Добавьте блок Controlled Voltage Source из библиотеки Simscape Foundation Library Electrical Electrical Sources.

Соедините блок Sine Wave с блоком Simulink-PS Converter и блоком Simulink-PS Converter с блоком Controlled Voltage Source.

Сконфигурируйте блок Sine Wave, чтобы совпадать с параметрами блока AC Voltage Source, который вы удалили.

Установите параметр Amplitude на sqrt(2)*120.

Установите параметр Frequency (rad/sec) на 60*2*pi.

Установите параметр Sample time на 1e-5. Затем кликните по значку с тремя точками![]() рядом с полем Sample time и выберите Create variable. Назовите переменную

рядом с полем Sample time и выберите Create variable. Назовите переменную Ts и нажмите Create. Можно теперь просмотреть и отредактировать эту переменную в вас рабочая область.

Убедитесь, что нет никаких блоков, которые заставляют вашу сеть быть нелинейной.

% Simulate sim(baselineModel) % Check for nonlinear blocks simscape.findNonlinearBlocks(baselineModel)

The number of linear or switched linear networks in the model is 1. ans = 0×0 empty cell array

Модель содержит только блоки, которые дают к линейным или коммутируемым линейным уравнениям.

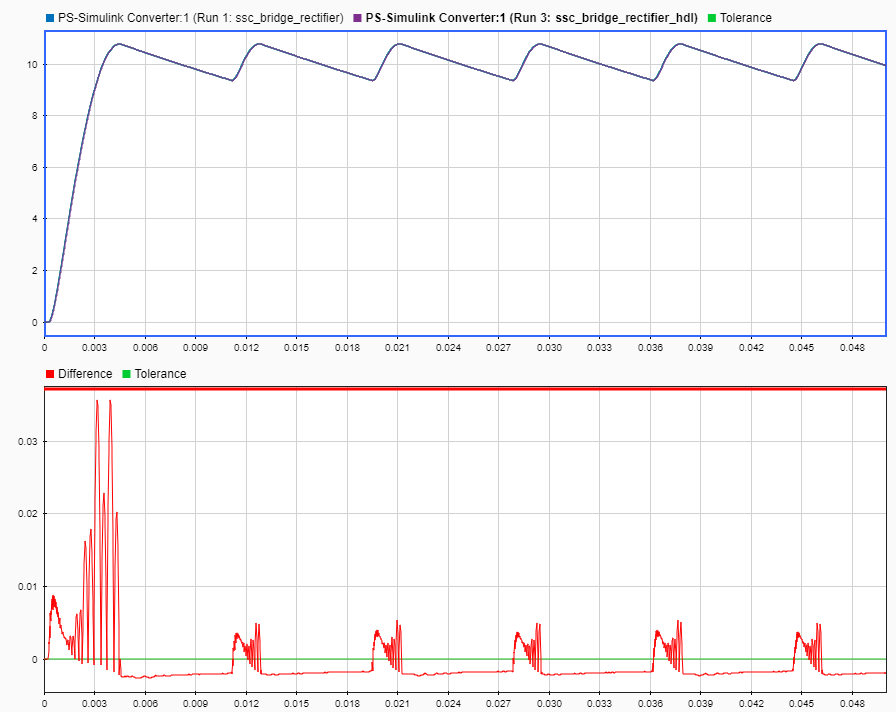

Симулируйте модель и сравните результаты с базовыми результатами в Инспекторе Данных моделирования.

% Get Simulation Data Inspector run IDs runIDs = Simulink.sdi.getAllRunIDs; runBaseline = runIDs(end - 1); runSwitchedLinear = runIDs(end); % Open the Simulation Data Inspector Simulink.sdi.view compBaseline1 = Simulink.sdi.compareRuns(runBaseline,... runSwitchedLinear);

Результаты похожи на базовые результаты.

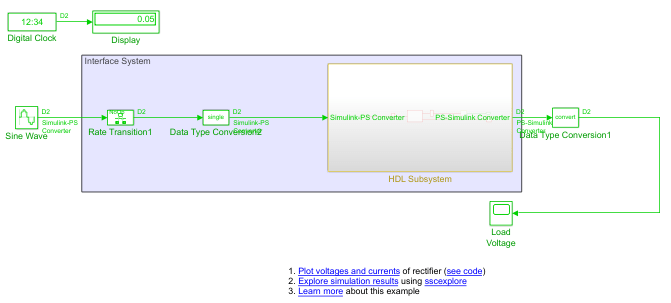

Чтобы выполнить будущие проверки прогресса для HDL Workflow Advisor Simscape, добавьте и соедините блок Digital Clock из библиотеки Simulink> Sources и блок Display из библиотеки Simulink Sinks, как показано на рисунке. Для Digital Clock, установленного параметр Sample time на Ts.

Модель все еще собирается использовать решатель переменного шага. Для оперативной симуляции необходимо использовать решатель фиксированного шага. Используйте цвета шага расчета и аннотации, чтобы помочь вам определить, содержит ли ваша модель какие-либо непрерывные настройки. Чтобы включить цвета шага расчета и аннотации, на вкладке Debug, нажимают Information Overlays, и в группе Sample Time, выбирают Colors и Text.

Диаграмма модели обновляется и отображения панели Легенды Синхронизации.

Сконфигурируйте модель для симуляции в реальном времени.

Сконфигурируйте модель Simulink для фиксированного шага, симуляции фиксированных затрат. В окне Configuration Parameters нажмите Solver и установите:

Type к Fixed-step

Solver к discrete (no continuous states)

Сконфигурируйте сеть Simscape для фиксированного шага, симуляции фиксированных затрат. Для блока Solver Configuration:

Выберите Use локальный решатель.

Убедитесь, что Solver type установлен в Backward Euler.

Задайте Ts для Sample time.

Симулируйте модель и сравните результаты с базовыми результатами в Инспекторе Данных моделирования.

% Simulate sim(baselineModel) % Get Simulation Data Inspector run IDs runIDs = Simulink.sdi.getAllRunIDs; runBaseline = runIDs(end - 2); runRealTime = runIDs(end); % Open the Simulation Data Inspector Simulink.sdi.view compBaseline1 = Simulink.sdi.compareRuns(runBaseline,... runRealTime);

Результаты похожи на базовые результаты.

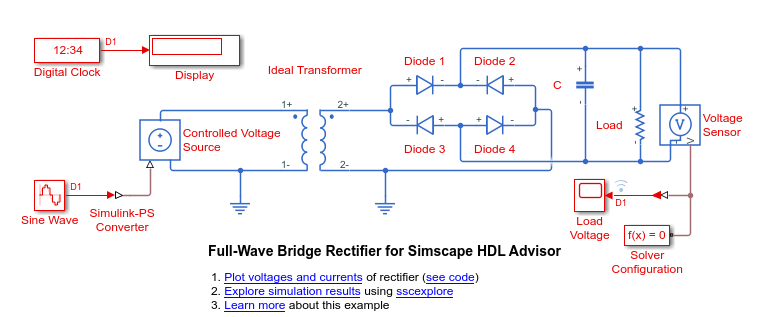

Сгенерируйте HDL-код путем выполнения HDL Workflow Advisor Simscape или на модели Simscape, которую вы подготовили в разделе Model Preparation или путем открытия ssc_bridge_rectifier_hdl модель, которая подготовлена к генерации кода.

Переименуйте модель.

Если вы подготовили модель в разделе Model Preparation, переименуйте модель ssc_model.

Чтобы открыться и использовать модель, которая уже подготовлена к генерации HDL-кода в командной строке MATLAB, входят

open_system('ssc_bridge_rectifier_hdl')Сохраните модель в локальную директорию как ssc_model.

Запустите HDL Workflow Advisor Simscape.

sschdladvisor('ssc_model')HDL Workflow Advisor Simscape открывается.

Осуществите проверки совместимости генерации кода.

Выберите Code generation compatibility> Check solver configuration , затем нажмите Run This Task.

Выберите Check model compatibility, затем нажмите Run this task.

Советник сообщает, когда модель передает эти проверки.

Извлеките коэффициенты пространства состояний. Выберите State-space conversion и нажмите Run All. Преобразование может занять время.

После выполнения задачи советник отображает сводные данные представления пространства состояний и таблицу параметров.

Количество состояний: 5

Количество входных параметров: 1

Количество выходных параметров: 1

Количество режимов: 7

Количество дифференциальных переменных: 1

Дискретный шаг расчета: 1e-05

| Параметр | Размер параметра |

| A | 5 x 5 x 7 |

| B | 5 x 1 x 7 |

| F0 | 5 x 1 x 7 |

| C | 1 x 5 x 1 |

| D | 1 x 1 x 1 |

| Y0 | 1 x 1 x 1 |

Размер состояния, режима и данных о параметре помогает вам оценить, сколько из ресурсов FPGA требуется, чтобы развертывать модель. Чем выше значения, тем требуется больше ресурсов FPGA. Входные и выходные данные указывают на номер и тип связей ввода-вывода, необходимых для развертывания приложений и визуализации.

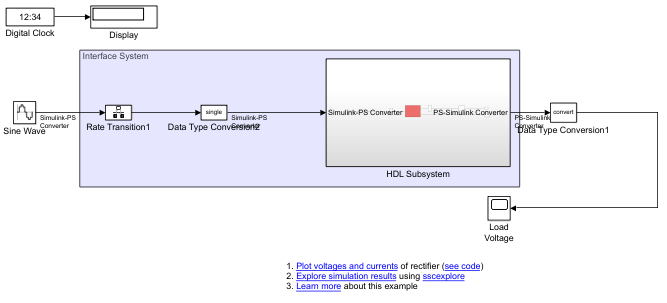

Сгенерируйте реализацию HDL своей модели. Выберите Implementation model generation> Generate implementation model и нажмите Run this task.

Когда HDL Workflow Advisor Simscape генерирует модель реализации, советник сообщает, что задача передала и отображает ссылку на сгенерированную модель реализации, которую называют gmStateSpaceHDL_ssc_model.

Откройте сгенерированную модель реализации путем нажатия на gmStateSpaceHDL_ssc_model.

Модель содержит блоки из исходной модели, а также новые блоки, которые поддерживают HDL Workflow Advisor:

Digital Clock, Display, Sine Wave и Load Voltage — Остатки из вашей исходной модели

Уровень Transition1 — Указатели передача данных между блоками, действующими на различных уровнях.

Тип данных Conversion1, Тип данных Conversion2 — Преобразует между типами данных двойной и одинарной точности. Генерация HDL-кода требует данных с одинарной точностью

Подсистема HDL — Содержит совместимую версию генерации HDL-кода вашей сети Simscape.

Загрузите блок Voltage — Scope, который отображает напряжение загрузки.

Подготовьте модель реализации к сравнению симуляции с базовыми результатами:

Можно настроить автоматически сгенерированную модель и удалить остаточные блоки по мере необходимости, чтобы улучшить чистоту модели. Блок Digial Clock и блок Display являются ненужными, но не запретят результаты симуляции.

Щелкните правой кнопкой по входному сигналу с блоком Scope и нажмите Log Selected Signals.

Блок Display в окне модели показывает прошедшее время симуляции.

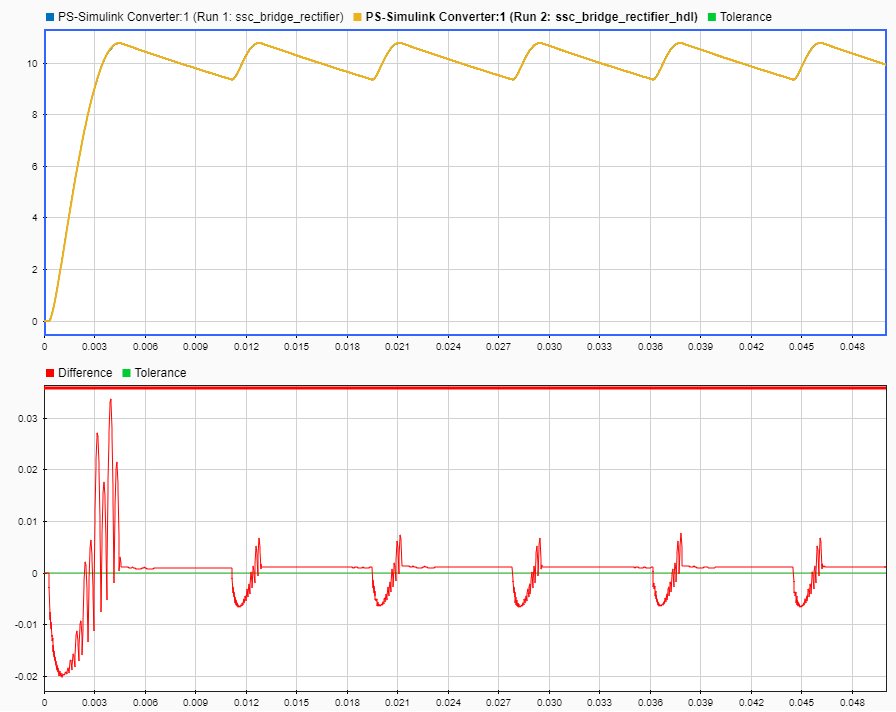

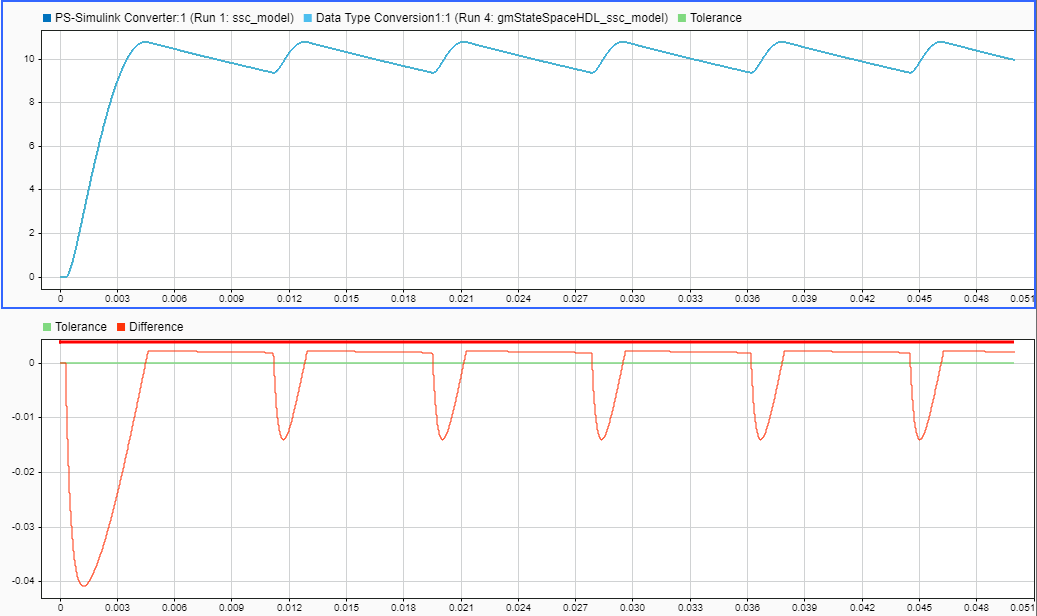

Чтобы гарантировать, что подсистема HDL соответствует вашей исходной модели Simscape, симулируйте модель и сравните результаты с базовыми результатами симуляции.

% Simulate sim('gmStateSpaceHDL_ssc_model') % Get Simulation Data Inspector run IDs runIDs = Simulink.sdi.getAllRunIDs; runBaseline = runIDs(end - 3); runHDLImplementation = runIDs(end); % Open the Simulation Data Inspector Simulink.sdi.view compBaseline1 = Simulink.sdi.compareRuns(runBaseline,... runHDLImplementation);

Результаты похожи на базовые результаты. Модель Simscape совместима с генерацией HDL-кода.

Сгенерируйте HDL-код от реализации:

Доступ к окну Configuration Parameters из модели реализации HDL. Расширьте HDL Code Generation и выберите Report. Установите флажки для опций Generate resource utilization report и Generate traceability report.

Запуститесь hdlsetup функция.

hdlsetup('gmStateSpaceHDL_ssc_model')Сохраните установки параметров подсистемы и модель.

hdlsaveparams('gmStateSpaceHDL_ssc_model');

%% Set Model 'gmStateSpaceHDL_ssc_model' HDL parameters

hdlset_param('gmStateSpaceHDL_ssc_model', 'FloatingPointTargetConfiguration', hdlcoder.createFloatingPointTargetConfig('NativeFloatingPoint' ...

, 'LatencyStrategy', 'MIN') ...

);

hdlset_param('gmStateSpaceHDL_ssc_model', 'HDLSubsystem', 'gmStateSpaceHDL_ssc_model/HDL Subsystem');

hdlset_param('gmStateSpaceHDL_ssc_model', 'MaskParameterAsGeneric', 'on');

hdlset_param('gmStateSpaceHDL_ssc_model', 'Oversampling', 49);

% Set SubSystem HDL parameters

hdlset_param('gmStateSpaceHDL_ssc_model/HDL Subsystem', 'FlattenHierarchy', 'on');

hdlset_param('gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/Generate Mode Vector', 'Architecture', 'MATLAB Datapath');

% Set SubSystem HDL parameters

hdlset_param('gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/State Update/Multiply State', 'SharingFactor', 1);

Сохраните настройки генерации модели валидации.

HDLmodelname = 'gmStateSpaceHDL_ssc_model'; hdlset_param(HDLmodelname, 'GenerateValidationModel', 'on');

Сгенерируйте HDL-код.

makehdl('gmStateSpaceHDL_ssc_model/HDL Subsystem')### Generating HDL for 'gmStateSpaceHDL_ssc_model/HDL Subsystem'.

### Using the config set for model gmStateSpaceHDL_ssc_model for HDL code generation parameters.

### Running HDL checks on the model 'gmStateSpaceHDL_ssc_model'.

### Begin compilation of the model 'gmStateSpaceHDL_ssc_model'...

### Applying HDL optimizations on the model 'gmStateSpaceHDL_ssc_model'...

### The code generation and optimization options you have chosen have introduced additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for compensation.

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Begin model generation.

### Model generation complete.

### Clock-rate pipelining results can be diagnosed by running this script: hdlsrc\gmStateSpaceHDL_ssc_model\highlightClockRatePipelining.m

### To clear highlighting, click the following MATLAB script: hdlsrc\gmStateSpaceHDL_ssc_model\clearhighlighting.m

### Generating new validation model: gm_gmStateSpaceHDL_ssc_model_vnl.

### Validation model generation complete.

### Begin VHDL Code Generation for 'gmStateSpaceHDL_ssc_model'.

### MESSAGE: The design requires 49 times faster clock with respect to the base rate = 3.33333e-06.

### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem7 as ...

hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1.vhd.

### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem6 as ...

hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1_block.vhd.

### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem5 as ...

hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1_block1.vhd.

### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem4 as ...

hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1_block2.vhd.

### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem3 as ...

hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1_block3.vhd.

### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem2 as ...

hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1_block4.vhd.

### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem1 as ...

hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1_block5.vhd.

### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/nfp_mul_single as hdlsrc\gmStateSpaceHDL_ssc_model\nfp_mul_single.vhd.

### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/nfp_add_single as hdlsrc\gmStateSpaceHDL_ssc_model\nfp_add_single.vhd.

### Working on dot_product_2 as hdlsrc\gmStateSpaceHDL_ssc_model\dot_product_2.vhd.

### Working on dot_product_1 as hdlsrc\gmStateSpaceHDL_ssc_model\dot_product_1.vhd.

### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/nfp_uminus_single as hdlsrc\gmStateSpaceHDL_ssc_model\nfp_uminus_single.vhd.

### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/nfp_relop_single as hdlsrc\gmStateSpaceHDL_ssc_model\nfp_relop_single.vhd.

### Working on HDL Subsystem_tc as hdlsrc\gmStateSpaceHDL_ssc_model\HDL_Subsystem_tc.vhd.

### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem as hdlsrc\gmStateSpaceHDL_ssc_model\HDL_Subsystem.vhd.

### Generating package file hdlsrc\gmStateSpaceHDL_ssc_model\HDL_Subsystem_pkg.vhd.

### Code Generation for 'gmStateSpaceHDL_ssc_model' completed.

### Creating HDL Code Generation Check Report HDL_Subsystem_report.html

### HDL check for 'gmStateSpaceHDL_ssc_model' complete with 0 errors, 7 warnings, and 2 messages.

### HDL code generation complete.Отчет генерации HDL-кода открывает и включает в себя любые сгенерированные ошибки или предупреждения. Отчет включает в себя ссылку на отчет использования ресурса, который описывает требования к ресурсам для развертывания FPGA.

Сгенерированный HDL-код и модель валидации сохранены в hdlsrc\gmStateSpaceHDL_ssc_model\html директория. Сгенерированный код сохранен как HDL_Subsystem_tc.vhd.

Чтобы сгенерировать HDL-код для развертывания на заданной цели, используйте HDL Workflow Advisor.

simscape.findNonlinearBlocks | hdladvisor (HDL Coder) | hdlsaveparams (HDL Coder) | hdlset_param (HDL Coder) | hdlsetup (HDL Coder) | makehdl (HDL Coder) | sschdladvisor (HDL Coder)