N-канал со стороны рассеял металлооксидный полупроводник или вертикально рассеял метал-оксидные полупроводниковые транзисторы, подходящие для высокого напряжения

Simscape / Электрический / Semiconductors & Converters

Блок N-Channel LDMOS FET позволяет вам модель LDMOS (или VDMOS) транзисторы, подходящие для высокого напряжения. Модель основана на поверхностном потенциале и включает эффекты из-за расширенного дренажа (дрейф) область:

Нелинейные емкостные эффекты сопоставлены с областью дрейфа

Поверхностное рассеивание и скоростное насыщение в области дрейфа

Скоростное насыщение и модуляция длины канала в области канала

Заряжайте сохранение в модели, таким образом, можно использовать модель для заряда чувствительные симуляции

Внутренний диод тела

Противоположное восстановление в диодной модели тела

Температурное масштабирование физических параметров

Для теплового варианта (см. Тепловой Порт), динамическое самонагревание

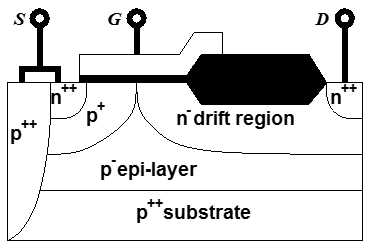

Физическую структуру модели показывают в следующем рисунке.

Область канала находится в p + область, от в большой степени n-doped источник хорошо в конец p + область. Область дрейфа является слегка содержащим присадку расширением дренажа. Далее вниз существует эпитаксиальный слой p-типа, и затем целая структура включена в большой степени p-doped подложка. Окись логического элемента является тонкой по целой области канала и по части области дрейфа. Далее в область дрейфа, окись логического элемента имеет большую толщину в локальном оксидировании кремния (LOCOS) область.

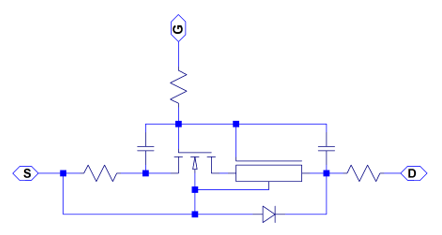

Следующий рисунок показывает эквивалентную схему модели.

Подход моделирования похож на [1]. Перекрытия контакта логического элемента с источником и n-скважинами дренажа моделируются как смешанные линейные емкости. Канал (p +) область моделируется с помощью поверхностной-потенциалом модели MOSFET. P-n переход между источником/объемом и дренажом моделируется с помощью идеального диода, и включая соединение и включая емкости диффузии. Область дрейфа под тонкой окисью логического элемента моделируется согласно поверхностно-потенциальной формулировке, которая включает:

Ток из-за слоя накопления в полупроводниково-окисном интерфейсе

Ток из-за электронов, текущих к дренажу глубже в области дрейфа

Область пространственного заряда между эпитаксиальным слоем и область дрейфа представлены с помощью эффекта зажимания на текущем течении через объем области дрейфа. Часть LOCOS области дрейфа моделируется как смешанный, последовательный резистор, и существуют также серийные сопротивления, добавленные к источнику, и пропускают контакты.

Для подробного описания модели канала см. поверхностную-потенциалом модель блока N-Channel MOSFET. Модель области дрейфа так же выведена из поверхностного потенциала с помощью уравнения Poisson. Для полупроводника n-типа при приближении постепенного канала уравнения определения:

где:

ψ является электростатическим потенциалом.

q является величиной электронного заряда.

ND является плотностью легирования области дрейфа.

ɛSi является диэлектрической проницаемостью полупроводникового материала (например, кремний).

ϕB является различием между внутренним параметром уровень Ферми и уровнем Ферми глубоко в области дрейфа.

VCB является потенциалом квазиферми области дрейфа, на которую ссылаются к объему.

ϕT является тепловым напряжением.

kB является константой Больцманна.

T является температурой.

Если мы пропускаем инверсию для модели постоянного тока, мы получаем следующее текущее выражение:

где:

ID является текущим дренажом.

θsat является скоростным насыщением.

Vij является разностью потенциалов между узлами i и j, где индексы D и K относятся к дренажу и к соединению канала и областей дрейфа, соответственно, и индекс G относится к логическому элементу с коррекцией из-за flatband применяемого напряжения.

flin/RD представляет проводимость объема области дрейфа, включая эффект зажимания из-за истощения от интерфейса дрейфа эпитаксиального слоя.

β является усилением слоя накопления в интерфейсе между областью дрейфа и тонкой окисью логического элемента.

θsurf является параметром, который составляет рассеивание в слое накопления из-за вертикального электрического поля.

Зажимание прочь объемной части области дрейфа описано

где:

λD является параметром, представляющим n-сторону вертикальная глубина области пространственного заряда вдоль интерфейса дрейфа эпитаксиального слоя при нулевом смещении, разделенном на вертикальную глубину неистощенной части области дрейфа при нулевом смещении.

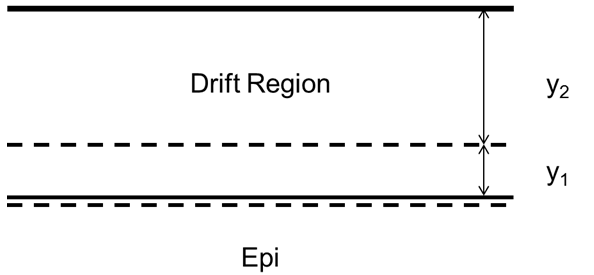

На рисунке главная сплошная линия является полупроводниковой поверхностью. Более низкая сплошная линия является соединением между областью дрейфа и эпитаксиальным слоем. Пунктирные линии показывают степень области пространственного заряда вокруг интерфейса эпитаксиального слоя дрейфа. λD является y1/y2 при нулевом смещении.

Vbi является встроенным напряжением для диода дрейфа эпитаксиального слоя.

VSB является напряжением исходного тела, используемым в качестве приближения к смещению, примененному через диод дрейфа эпитаксиального слоя. Используя это напряжение вместо VKB более численно устойчиво, и выравнивается по ширине потому что большинство падений напряжения источника дренажа через область дрейфа в транзисторе на состоянии.

Модель заряда похожа на ту из поверхностной-потенциалом модели MOSFET с дополнительными выражениями с учетом заряда в области дрейфа. Блок использует выведенные уравнения как описано в [1], которые включают и инверсию и накопление в области дрейфа.

Блок моделирует диод тела как идеал, экспоненциальный диод и с соединением и с емкостями диффузии:

где:

Idio является током через диод.

Is является противоположным текущим насыщением.

VDB является напряжением тела дренажа.

n является фактором идеальности.

ϕT является тепловым напряжением.

Cj является емкостью перехода диода.

Cj0 является емкостью перехода нулевого смещения.

Vbi является встроенным напряжением.

Cdiff является емкостью диффузии диода.

τ является временем транспортировки.

Емкости заданы посредством явного вычисления зарядов, которые затем дифференцируются, чтобы дать емкостные выражения выше. Блок вычисляет емкостные диодные токи как производные времени соответствующих зарядов, похожих на расчет в поверхностной-потенциалом модели MOSFET.

Поведение по умолчанию состоит в том, что зависимость от температуры не моделируется, и устройство симулировано при температуре, для которой вы обеспечиваете параметры блоков. Чтобы смоделировать зависимость от температуры в процессе моделирования, выберите Model temperature dependence для параметра Parameterization на вкладке Temperature Dependence.

Модель включает температурные эффекты на характеристиках емкости, а также моделирование зависимости транзистора статическое поведение на температуре в процессе моделирования.

Параметр Measurement temperature на вкладке Main задает температурный Tm1, в котором были извлечены другие параметры устройства. Параметры Temperature Dependence обеспечивают температуру симуляции, Ts и температурные масштабные коэффициенты для других параметров устройства. Для получения дополнительной информации смотрите Температурную Зависимость.

Блок имеет дополнительный тепловой порт, скрытый по умолчанию. Чтобы осушить тепловой порт, щелкните правой кнопкой по блоку по своей модели, и затем из контекстного меню выбирают Simscape> Block choices> Show thermal port. Это действие отображает тепловой порт H на значке блока и отсоединяет параметры Thermal Port.

Используйте тепловой порт, чтобы симулировать эффекты выработанного тепла и температуры устройства. Для получения дополнительной информации об использовании тепловых портов и на параметрах Thermal Port, смотрите Термальные эффекты Симуляции в Полупроводниках.

Тепловой вариант блока включает динамическое самонагревание, то есть, позволяет вам симулировать эффект самонагревания на электрических характеристиках устройства.

[1] Aarts, A., Н. Д'Аллевеин и Р. ван Лэнджевелд. “Поверхностная-потенциалом высоковольтная компактная транзисторная модель LDMOS”. Транзакции IEEE на электронных устройствах. 52 (5):999 - 1007. Июнь 2005.

[2] Ван Лэнджевелд, R., А. Дж. Шолтен и D. B.M. Клаассен. "Физическое образование модели 11 MOS. Уровень 1101". Nat.Lab. Несекретный отчет 2003/00239. Апрель 2003.

[3] О, S-Y., Д. Э. Уорд и Р. В. Даттон. “Анализ переходных процессов МОП-транзисторов”. IEEE J. Твердотельные схемы. SC-15, стр 636-643, 1980.