Приложение SoC состоит из одного или нескольких алгоритмов. Когда алгоритм передает данные другому алгоритму, данные представлены как сигнальная линия в Simulink®. Для поведенческих моделей передача данных мгновенна.

Эта схема показывает поведенческую модель datapath между двумя алгоритмами.

В материальном мире алгоритмы могут быть на двух отдельных устройствах, и передач данных не происходит мгновенно. Кроме того, алгоритмы могут запуститься на различных уровнях, и поэтому потребовать буферизации и управляющей логики для квитирования. Например, простое квитирование, такое как “данные допустимо” от производителя данных и “готово признать, что данные” от потребителя служат управляющей логикой.

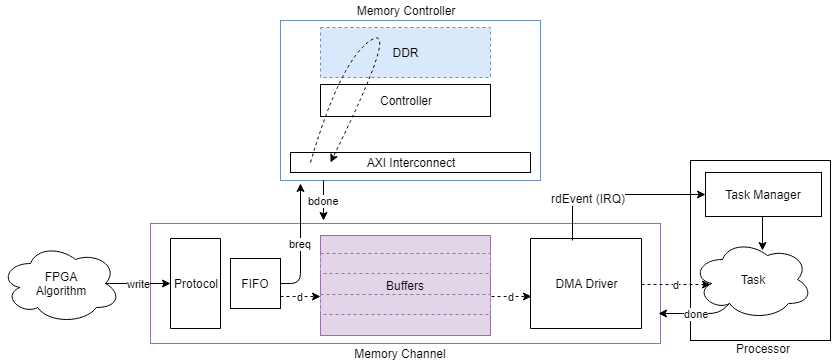

Если один элемент обработки выполняется в FPGA или ASIC, и следующий элемент обработки выполняется на встраиваемом процессоре, то простая сигнальная линия представляет больше, чем только комплексное оборудование datapath. Передача данных также представляет обработчик прерывания процессора, планировщика задач операционной системы и стек программного драйвера.

В SoC Blockset™, вы передачи данных модели и протоколы квитирования через общую память. Используйте блок Memory Channel для внешней памяти или блок Register Channel для регистров.

Блок Memory Channel представляет абстракцию комплексу datapath через внешнюю память и поддерживает различные протоколы квитирования. Это упрощает улучшение связи между обработкой элементов от мгновенного, провода протокола меньше до полной связи прямого доступа к памяти (DMA) между процессором и FPGA.

Путем добавления блока Memory Channel вы можете перемещение данных модели от одной части алгоритма другому.

Блок предоставляет модель коммуникационного конвейера. Канал также обеспечивает сигнальный интерфейс.

Интерфейсный протокол зависит от того, где обработка выполняется. FPGA или алгоритм ASIC могут выполнить передачи данных при помощи стандартных протоколов, таких как AXI4-поток или AXI4. Встроенный алгоритм центрального процессора может использовать интерфейс драйвера, экспортируемый в пространство пользователя.

Этот рисунок показывает модель datapath из алгоритма FPGA, передающего данные потоком к алгоритму процессора.

Другая модель выборов типа Memory Channel дополнительный общий datapaths через внешнюю память. Для получения дополнительной информации о настройках Memory Channel, смотрите Memory Channel.

Средство записи и читатель соединяются с памятью и запрашивают доступ к внешней памяти от контроллера памяти. Для получения дополнительной информации о блоке Memory Controller, смотрите Memory Controller.

Блок Register Channel представляет сериализацию чтений процессора или записей через общую шину конфигурирования такой как AXI-облегченную.

Блок Register Channel предоставляет модель синхронизации для передачи значений регистра между алгоритмами процессора и оборудования через общую шину конфигурирования. Используйте этот блок, когда процессор пишет команду или регистр конфигурации или когда процессор читает регистр состояния.

Memory Channel | Register Channel