Вынесите решение транзакции памяти для одного или нескольких блоков Канала Памяти

SoC Blockset / Память

Блок Memory Controller выносит решение между ведущими устройствами и предоставляет им уникальный доступ к общей памяти. Сконфигурируйте этот блок, чтобы поддержать несколько каналов с различными арбитражными протоколами. Блок Memory Controller также оснащен, чтобы регистрировать и отобразить данные о производительности, позволив вам отладить и изучить эффективность вашей системы во времени симуляции.

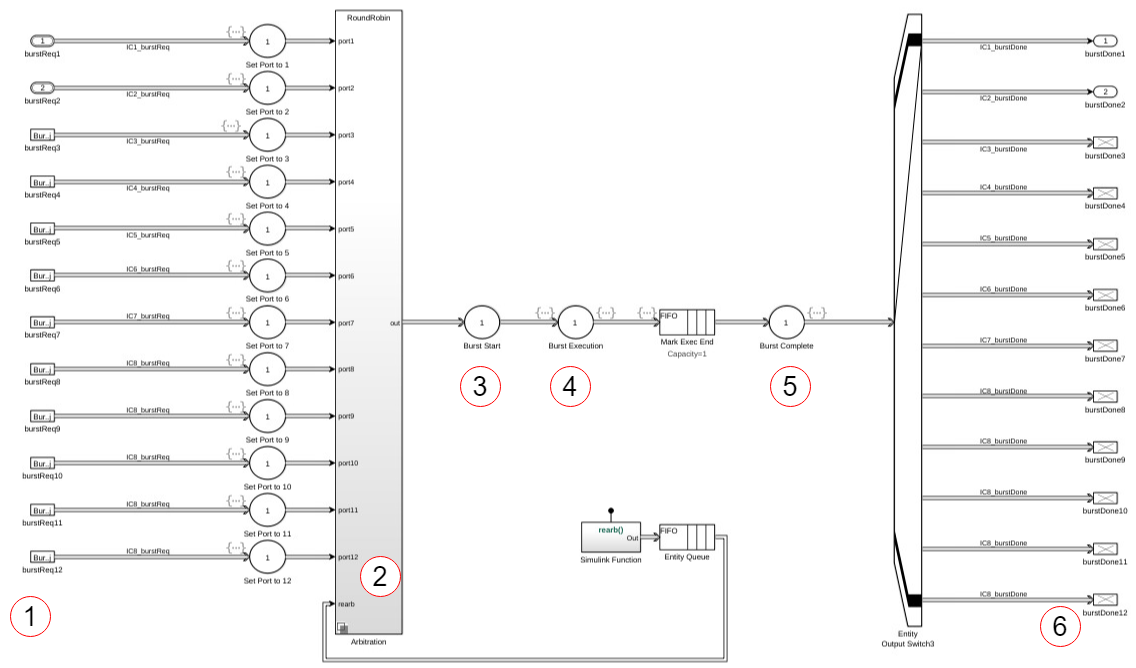

Следующее изображение показывает реализацию блока Memory Controller.

Числа в изображении представляют различные этапы задержки блока.

Пакетный запрос вводит блок.

Запрос может быть задержан арбитражем, пока это не предоставленный доступ к шине. Установите арбитражную политику во Взаимосвязанном арбитраже.

Если ваша модель требует дополнительной задержки, прежде чем первая передача запустится, установите то значение в Просьбе сначала передать (в часах).

Пакетная задержка выполнения вычисляется пакетным размером, шириной данных, тактовой частотой и Пропускной способностью, снижающей норму (%) значение.

Если ваша модель требует задержки от пакетного завершения, пока пакетный ответ не выпущен к каналу, установите то значение в Последней передаче в завершенную транзакцию (в часах).

Контроллер памяти имеет внутреннее состояние, которое отображается при использовании Logic Analyzer, чтобы просмотреть метрики симуляции и выполнения. Значения состояния:

BurstRequest: Пакетный запрос вводит блок.

BurstExecuting: Пакет выполняется.

BurstDone: Пакет сделан, выполнившись.

BurstComplete: Пакет завершен, и сигнал burstDone отправляется ведущему устройству.

Для получения информации о визуализации задержек контроллера памяти см. Графики Задержки Контроллера памяти.

Когда Interconnect arbitration установлен в Round Robin, модель не поддерживает продвижение симуляции. Для получения дополнительной информации о продвижении симуляции смотрите Степпер Симуляции.

Memory Channel | Memory Traffic Generator | Register Channel