Для быстрого прототипирования сетей глубокого обучения на FPGA от MATLAB ® используйте управляемый MATLAB процессор глубокого обучения. Процессор интегрирует общий процессор глубокого обучения с HDL Verifier™ MATLAB в качестве AXI Master IP. Для получения дополнительной информации:

Общий IP-адрес процессора глубокого обучения см. в разделе Приложения процессора глубокого обучения.

MATLAB в качестве AXI Master IP, см. Настройка для MATLAB AXI Master (HDL Verifier).

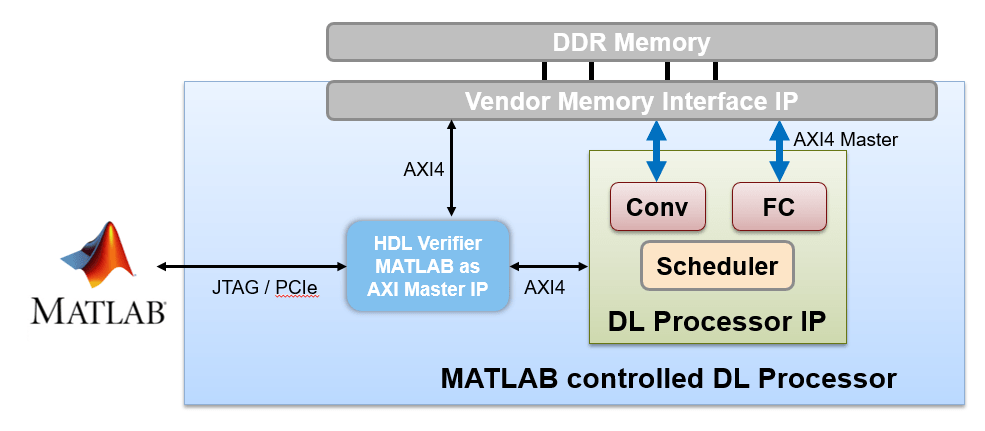

Вы можете использовать этот процессор для запуска нейронных сетей с различными входами, весами и смещениями на одной платформе FPGA, потому что ядро IP процессора глубокого обучения может обрабатывать тензоры и формы любого размера. Перед использованием MATLAB в качестве AXI Master убедитесь, что установлены пакеты поддержки HDL Verifier для плат FPGA. На этом рисунке показана управляемая MATLAB архитектура процессора глубокого обучения.

Для интеграции универсального процессора глубокого обучения IP с MATLAB в качестве AXI Master используйте интерфейс AXI4 Slave ядра процессора глубокого обучения IP. Используя экспресс-интерфейс JTAG или PCI, IP отвечает на команды чтения или записи из MATLAB. Поэтому вы можете использовать управляемый MATLAB процессор глубокого обучения, чтобы развернуть нейронную сеть глубокого обучения на платах FPGA из MATLAB, выполнить операции, указанные сетевой архитектурой, а затем вернуть предсказанные результаты в MATLAB. В следующем примере показано, как развернуть предварительно обученную сеть AlexNet на комплекте для разработки Intel ® Arria ® 10 SoC.