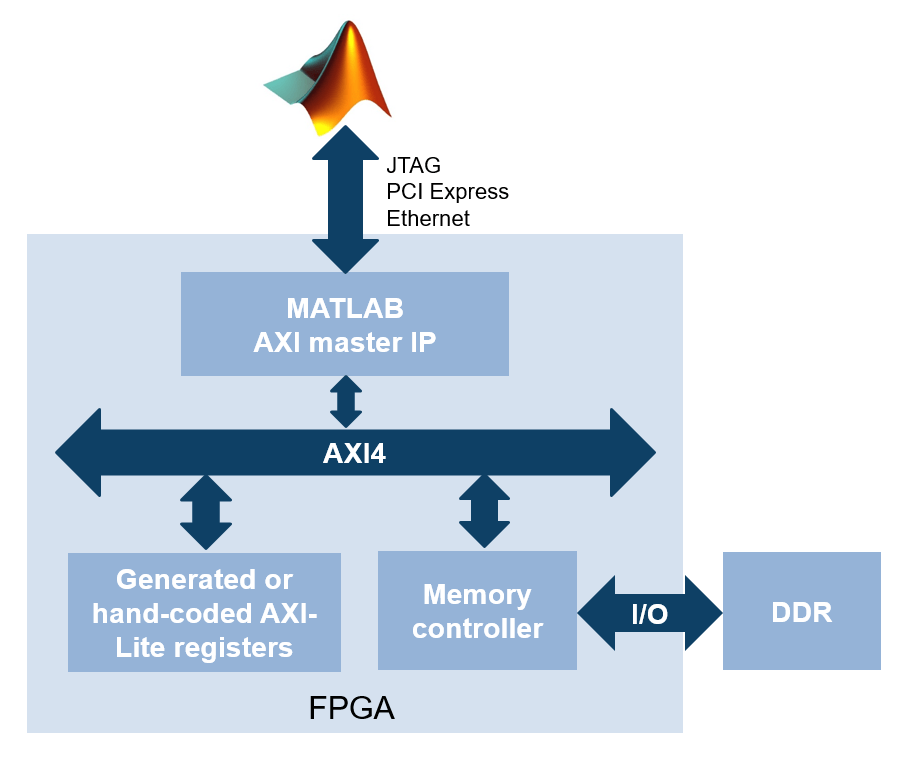

Доступ к расположениям встроенной памяти можно получить из MATLAB, используя главный IP-адрес MATLAB AXI в конструкции FPGA, а также aximaster объект. Объект подключается к IP по физическому кабелю и позволяет выполнять команды чтения и записи в подчиненные ячейки памяти из командной строки MATLAB.

Для использования этой функции необходимо загрузить пакет аппаратной поддержки для платы FPGA. См. раздел Загрузка пакета поддержки платы FPGA.

Для доступа к встроенной памяти MATLAB ® необходимо включить главный IP-адрес MATLAB AXI в конструкцию FPGA. Этот IP-адрес подключается к расположениям ведомой памяти на плате. IP также отвечает на команды чтения и записи из командной строки MATLAB по кабелю JTAG, PCI Express или Ethernet.

Чтобы настроить главный IP-адрес AXI для доступа из MATLAB, выполните следующие шаги настройки:

Включите главный IP-адрес MATLAB AXI в конструкцию FPGA. Чтобы добавить путь к IP-файлам в проект, вызовите setupAXIMasterForVivado или setupAXIMasterForQuartus функции.

В проекте FPGA укажите, к каким адресам разрешено обращаться главному IP-интерфейсу AXI.

Примечание

Ведущий IP-адаптер AXI поддерживает AXI4 расположения ведомой памяти Lite, AXI4 и Altera ® Avalon. Межсоединение FPGA автоматически преобразует AXI4 транзакции в протокол каждого адреса.

Скомпилировать проект FPGA, включая главный IP-адрес MATLAB AXI.

Подключите плату FPGA к компьютеру с помощью физического кабеля (кабеля JTAG, PCI Express или Ethernet).

Программирование FPGA с помощью скомпилированного дизайна.

Примечание

С другой стороны, Вы можете выступить, эти шаги в HDL Coder™ вели технологический процесс при помощи типового справочного дизайна, такого как тот, включенный в эти примеры: IP Основной Технологический процесс Поколения Без Встроенного Процессора РУКИ: Стрела ДЕКА МАКС 10 Комплектов Оценки FPGA (Кодер HDL) или IP Основной Технологический процесс Поколения без Встроенного Процессора РУКИ: Xilinx Kintex-7 KC705 (Кодер HDL).

После запуска программы на плате FPGA можно создать главный объект MATLAB AXI, aximaster. Для доступа к расположениям ведомой памяти на плате используйте readmemory и writememory методы данного объекта.

При использовании JTAG в качестве физического соединения с платой могут использоваться дополнительные IP-адреса, использующие одно и то же соединение JTAG. Такие IP-адреса включают в себя данные FPGA, Altera SignalTap II или ядра Xilinx ® Vivado ® Logic Analyzer. Главный IP-адрес MATLAB AXI может сосуществовать в вашей конструкции с другими IP-адресами, использующими соединение JTAG, однако только одно из этих приложений может одновременно использовать кабель JTAG. Отпустите клавишуaximaster объект для возврата ресурса JTAG для использования другими приложениями.

Наиболее распространенным противоречивым использованием кабеля JTAG является перепрограммирование FPGA. Остановите сбор данных FPGA или главное соединение MATLAB AXI JTAG, прежде чем использовать кабель для программирования FPGA.

Максимальная скорость передачи данных между главным компьютером и FPGA ограничена тактовой частотой JTAG. Для плат Altera тактовая частота JTAG составляет 12 МГц. или 24 МГц. Для плат Xilinx тактовая частота JTAG составляет 33 МГц. или 66 МГц. Частота JTAG зависит от типа кабеля и максимальной тактовой частоты, поддерживаемой платой FPGA.