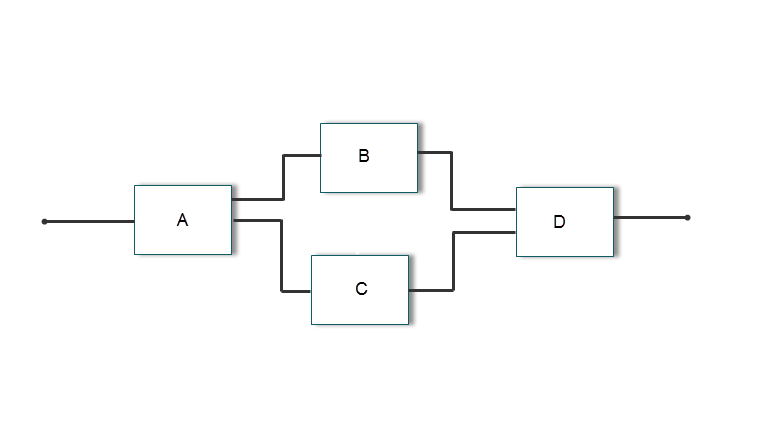

Рассмотрим модель верхнего уровня, состоящую из компонентов A, B, C, и D:

A и B - существующие компоненты, для которых ранее был создан и протестирован код.

C, ссылочная модель и D, подсистема, являются новыми компонентами.

При моделировании ПО в цикле (SIL) и процессора в цикле (PIL) можно использовать следующие подходы к тестированию числовой эквивалентности:

Тестовый код всех компонентов вместе. См. раздел Тестирование кода верхней модели.

Тестирование новых компонентов по отдельности (перед тестированием кода всех компонентов). См. Код модели и код подсистемы тестирования.

Для некоторых форм тестирования требуется тестовая модель электрического жгута. Модель тестового электрического жгута:

Генерирует тестовые векторы или входные сигналы стимула, которые подают тестируемый блок.

Позволяет наблюдать или фиксировать выходные данные блока.

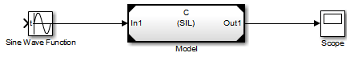

В следующем примере показана простая модель тестового кабеля.

Тестируемый блок является блоком модели. Блок синусоидальной волны генерирует входные данные для блока модели. Через блок Область (Scope) можно наблюдать вывод из блока Модель (Model). Сведения о создании и использовании тестовых жгутов см. в разделах Создание тестовых жгутов и Выбор свойств (Simulink Test) и Процесс проверки генерации кода с помощью Simulink Test (Simulink Test).

Для совместного тестирования кода, сформированного из компонентов верхней модели (A, B, C, и D) можно использовать SIL/PIL верхней модели или блок модели SIL/PIL.

Верхняя модель SIL/PIL:

Создание тестовых векторов или входных сигналов стимула в рабочей области MATLAB.

Запустите верхнюю модель в режимах моделирования Normal, SIL и PIL. Программа загружает тестовые векторы или входные сигналы стимула из рабочей области MATLAB ®.

Для каждого режима моделирования наблюдайте или захватывайте выходные данные.

Проверьте числовую эквивалентность путем сравнения нормальных выходов с выходами SIL и PIL.

Блок модели SIL/PIL:

Создайте блок «Модель», содержащий компоненты верхней части модели.

Вставьте блок «Модель» в расчетную модель, например модель тестового кабеля.

Выполните моделирование, переключив блок модели между нормальным, SIL и PIL режимами. Для режимов моделирования SIL и PIL установите

для параметра блока Code interface Model значение Top model.

Проверьте числовую эквивалентность путем сравнения нормальных выходов с выходами SIL и PIL.

Дополнительные сведения см. в разделе Моделирование с использованием модели верхнего уровня и Workflow-процесс проверки SIL/PIL Manager.

Тестирование кода, сгенерированного из компонента C в качестве части ссылочной иерархии модели используйте подход SIL/PIL блока модели:

Вставка блока модели C в расчетной модели, например в модели тестового электрического жгута.

Выполните моделирование, переключив блок модели между нормальным, SIL и PIL режимами. Для режимов моделирования SIL и PIL установите

для параметра блока Code interface Model значение Model reference.

Проверьте числовую эквивалентность путем сравнения нормальных выходов с выходами SIL и PIL.

Дополнительные сведения см. в разделах Моделирование с блоками модели и Поток операций проверки SIL/PIL Manager.

Тестирование кода, генерируемого подсистемой D, используйте один из этих рабочих процессов.

| Технологический процесс | Описание |

|---|---|

| Тестовый жгут Simulink с SIL/PIL Manager | Выполните модульные тесты для кода подсистемы, который является частью кода, созданного из родительской модели.

Дополнительные сведения см. в разделе Тест сгенерированного кода атомной подсистемы. Если подсистема не поддерживается данным рабочим процессом, используйте рабочий процесс блока SIL или PIL. Дополнительные сведения о неподдерживаемых подсистемах и других ограничениях см. в разделе Ограничения рабочего процесса атомной подсистемы. |

| Блок SIL или PIL | Создайте и протестируйте новый автономный код из подсистемы.

Дополнительные сведения см. в разделе Моделирование блоков SIL или PIL. |

| Компонент, на основе которого создается код | Использование моделирования | Шаги | Сгенерированный интерфейс кода | Источник тестового сигнала |

|---|---|---|---|---|

| Топ-модель | Верхняя модель SIL/PIL | В SIL/PIL Manager:

| Автономный | Рабочее пространство MATLAB |

| Модель, на которую ссылается блок модели | Блок модели SIL/PIL |

| Определяется параметром блока модели Интерфейс кода - автономная или ссылочная модель. | Расчетная модель, например, тестовая модель электрического жгута |

| Подсистема | Тестовый жгут Simulink и диспетчер SIL/PIL |

| Определяется сгенерированным кодом родительской модели - автономной или ссылочной моделью. | Test™ жгут Simulink ® |

| Подсистема | Блок SIL или PIL | Подстановка блоков вручную | Автономный | Расчетная модель, например, тестовая модель электрического жгута. |