Деление ввода на константу и округление до целого числа и создание оптимизированного кода HDL

Поддержка HDL/математические операции конструктора фиксированных точек

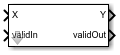

Блок Divide by Constant HDL Optimized выводит результат деления входного сигнала на константу и округляет результат до целого числа с использованием указанного метода округления с использованием архитектуры, оптимизированной для HDL, с запаздыванием «cycle-true».

В блоке «Деление на константу, оптимизированную для HDL» используется алгоритм, функционально аналогичный методу Гранлунда-Монтгомери-Уоррена. Операция деления вычисляется посредством умножения на обратное, что обычно приводит к лучшей производительности встроенных систем.

Блоки Divide by Constant HDL Optimized, Real Divide HDL Optimized и Complex Divide HDL Optimized выполняют операцию разделения и генерируют оптимизированный код HDL.

Оптимизация реального разделения HDL и оптимизация комплексного разделения HDL основаны на алгоритме CORIDC. Эти блоки принимают широкий спектр входных данных, но приводят к большей задержке.

Деление на постоянный HDL Optimized принимает только вещественные входные данные и постоянный делитель. Использование этого блока потребляет фрагменты DSP, но завершит операцию разделения за меньшее количество циклов и с более высокой тактовой частотой.