В помощнике по рабочим процессам HDL можно выбрать режим синхронизации процессора/FPGA для процессора и FPGA, если:

Создание пользовательского IP-ядра для использования в проекте интеграции встраиваемых систем.

Используйте рабочий процесс ввода-вывода FPGA в режиме реального времени Simulink.

Доступны следующие режимы синхронизации:

Free running (по умолчанию)

Coprocessing – blocking

Coprocessing – nonblocking with delay (доступно только для рабочего процесса ввода-вывода FPGA Simulink в реальном времени)

В режиме свободной работы процессор и FPGA работают несинхронизированно, непрерывно и параллельно.

Выберите режим синхронизации Процессор/FPGA (Free running), если не требуется автоматическая синхронизация процессора и FPGA.

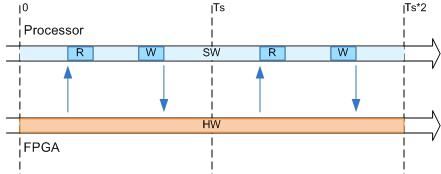

На следующей схеме показано, как процессор и FPGA могут взаимодействовать в режиме свободной работы. Затененные области указывают, что процессор и FPGA работают непрерывно.

В режиме блокировки сопроцессора HDL Coder™ автоматически генерирует логику синхронизации для FPGA, чтобы процессор и FPGA работали совместно.

Выберите Coprocessing - blocking в качестве режима синхронизации процессора/FPGA, когда время выполнения FPGA является коротким относительно времени выборки процессора, и необходимо, чтобы FPGA была завершена до продолжения работы процессора.

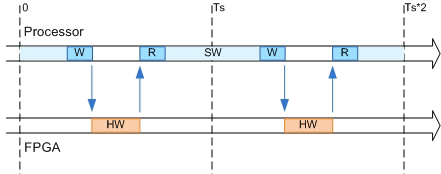

На следующей схеме показано, как процессор и FPGA работают в режиме блокирующей сообработки.

Затененные области указывают, когда процессор и FPGA работают. В течение каждого времени выборки процессор записывает данные в FPGA, затем останавливается и ожидает индикации того, что FPGA завершила обработку, прежде чем продолжить выполнение. Каждый раз при запуске FPGA выполняет логику, сгенерированную для времени выборки одной подсистемы DUT.

В режиме замедленного неблочного сопроцессора кодер HDL автоматически генерирует логику синхронизации для FPGA, так что процессор и FPGA работают параллельно. Этот режим доступен только для модулей ввода-вывода Speedgoat, использующих Xilinx ® ISE с рабочим процессом ввода-вывода Simulink Real-Time FPGA.

Выберите Coprocessing - non blocking with delay в качестве режима синхронизации Процессор/FPGA, когда время обработки FPGA является большим относительно времени выборки процессора, или вы не хотите, чтобы процессор ожидал завершения FPGA, прежде чем процессор продолжит работу.

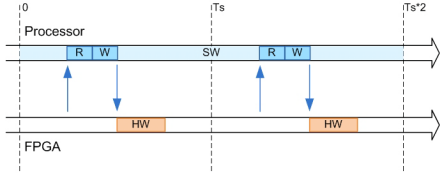

На следующей схеме показано, как процессор и FPGA работают в режиме замедленного неблочного сопроцессора.

Затененные области указывают, когда процессор и FPGA работают. В течение каждого времени выборки процессор считывает данные FPGA из предыдущего времени выборки, затем записывает в FPGA и продолжает работать, не дожидаясь завершения FPGA. Каждый раз при запуске FPGA выполняет логику, сгенерированную для времени выборки одной подсистемы DUT.