По умолчанию кодер представляет константы как скаляры или агрегаты в зависимости от размера и типа данных. Кодер представляет значения, которые меньше 232-1, как целые числа, и значения, которые больше или равны 232-1, как агрегаты. Следующие объявления констант VHDL являются примерами объявлений, генерируемых по умолчанию для значений менее 32 бит:

CONSTANT coeff1: signed(15 DOWNTO 0) := to_signed(-60, 16); -- sfix16_En16 CONSTANT coeff2: signed(15 DOWNTO 0) := to_signed(-178, 16); -- sfix16_En16

Если требуется, чтобы значения констант представлялись в виде агрегатов, установите значение Представить значения констант в виде агрегатов следующим образом:

Выберите вкладку Глобальные настройки (Global Settings) в диалоговом окне Создать ЛПВП (Generate HDL).

Выберите вкладку Дополнительно.

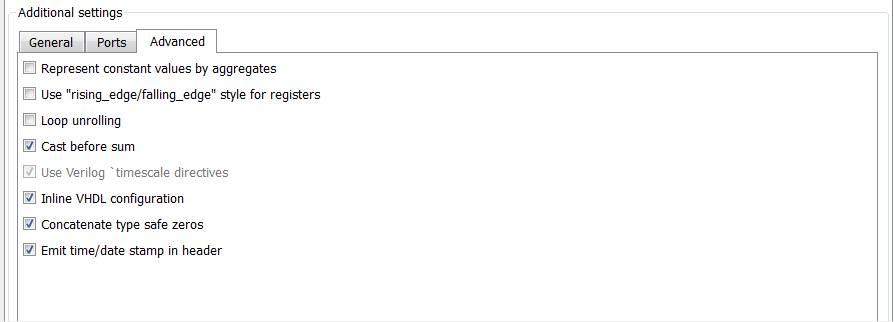

Выберите Представление значений констант по агрегатам, как показано на следующем рисунке.

Предшествующие постоянные объявления теперь будут выглядеть следующим образом:

CONSTANT coeff1: signed(15 DOWNTO 0) := (5 DOWNTO 3 => '0',1 DOWNTO 0 => '0,OTHERS =>'1'); CONSTANT coeff2: signed(15 DOWNTO 0) := (7 => '0',5 DOWNTO 4 => '0',0 => '0',OTHERS =>'1');

Альтернатива командной строки: generatehdl функция со свойством UseAggregatesForConst для представления констант в коде HDL в виде агрегатов.

По умолчанию кодер поддерживает петли VHDL. Однако некоторые инструменты EDA их не поддерживают. Если вы используете такой инструмент вместе с VHDL, вы можете развернуть и удалить FOR и GENERATE петли из сгенерированного кода VHDL. Код Verilog уже разблокирован.

Распаковка и удаление FOR и GENERATE петли,

Выберите вкладку Глобальные настройки (Global Settings) в диалоговом окне Создать ЛПВП (Generate HDL).

Выберите вкладку Дополнительно. Появится панель Дополнительно (Advanced).

Выберите Loop unrolling, как показано на следующем рисунке.

Альтернатива командной строки: generatehdl функция со свойством LoopUnrolling для раскручивания и удаления петель из сгенерированного кода VHDL.

Кодер может генерировать два стиля кода VHDL для проверки растущих краев, когда фильтр работает на регистрах. По умолчанию сгенерированный код проверяет событие синхронизации, как показано на ELSIF оператор следующего технологического блока VHDL.

Delay_Pipeline_Process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

delay_pipeline(0 TO 50) <= (OTHERS => (OTHERS => '0'));

ELSEIF clk'event AND clk = '1' THEN

IF clk_enable = '1' THEN

delay_pipeline(0) <= signed(filter_in);

delay_pipeline(1 TO 50) <= delay_pipeline(0 TO 49);

END IF;

END IF;

END PROCESS Delay_Pipeline_Process ;

Если вы предпочитаете, кодер может создавать код VHDL, который применяет VHDL rising_edge вместо этого функция. Например, ELSIF оператор в предыдущем блоке процесса будет заменен следующим оператором:

ELSIF rising_edge(clk) THEN

Для использования rising_edge функция,

Щелкните Глобальные настройки (Global Settings) в диалоговом окне Создать ЛПВП (Generate HDL).

Выберите вкладку Дополнительно. Появится панель Дополнительно (Advanced).

Выберите Use 'rising _ edge' для регистров, как показано в следующем диалоговом окне.

Альтернатива командной строки: generatehdl функция со свойством UseRisingEdge для использования VHDL rising_edge функция для проверки растущих краев во время операций регистра.

Конфигурации VHDL могут быть встроены в остальную часть кода VHDL для объекта или внешними в отдельных исходных файлах VHDL. По умолчанию кодер включает конфигурации для фильтра в сгенерированном коде VHDL. При создании собственных файлов конфигурации VHDL подавите генерацию встроенных конфигураций.

Для подавления генерации встроенных конфигураций

Выберите вкладку Глобальные настройки (Global Settings) в диалоговом окне Создать ЛПВП (Generate HDL).

Выберите вкладку Дополнительно. Появится панель Дополнительно (Advanced).

Снимите флажок «Встроенная конфигурация VHDL», как показано на следующем рисунке.

Альтернатива командной строки: generatehdl функция со свойством InlineConfigurations для подавления генерации встроенных конфигураций.

В VHDL конкатенация нулей может быть представлена в двух синтаксических формах. Одна форма, '0' & '0', является безопасным по типу. Этот синтаксис используется по умолчанию. Альтернативный синтаксис, "000000...", может быть легче для чтения и более компактен, но может привести к неоднозначным типам.

Использование синтаксиса "000000..."для конкатенированных нулей,

Выберите вкладку Глобальные настройки (Global Settings) в диалоговом окне Создать ЛПВП (Generate HDL).

Выберите вкладку Дополнительно. Появится панель Дополнительно (Advanced).

Снимите нулевые значения типа Concatenate, как показано на следующем рисунке.

Альтернатива командной строки: generatehdl функция со свойством SafeZeroConcat для использования синтаксиса "000000...", для конкатенированных нулей.

По умолчанию сгенерированный код HDL работает с входными данными, используя типы данных, определенные конструкцией фильтра, а затем преобразует результат в указанный тип результата.

Типичные процессоры DSP перед работой с данными приводят входные данные к типу результата. В зависимости от операции результаты могут быть различными. Если необходимо, чтобы сгенерированный код HDL обрабатывал ввод результата таким образом, используйте опцию Cast before sum следующим образом:

Выберите вкладку Глобальные настройки (Global Settings) в диалоговом окне Создать ЛПВП (Generate HDL).

Выберите вкладку Дополнительно. Появится панель Дополнительно (Advanced).

Выберите Литейная форма перед суммированием, как показано на следующем рисунке.

Альтернатива командной строки: generatehdl функция со свойством CastBeforeSum приведение входных значений к типу результата для операций сложения и вычитания.

Опция Cast before sum связана с настройкой конструктора фильтров для опции квантования Cast signals before sum следующим образом:

Некоторые типы объектов фильтра не имеют сигналов Cast перед свойством sum. Для таких объектов фильтра при формировании кода ЛПВП фактически выключается команда Cast before sum; он не относится к фильтру.

Если объект фильтра имеет свойство Cast signals before sum, кодер по умолчанию следует за настройкой Cast signals before sum в объекте фильтра. Этот параметр отображается в интерфейсе пользователя. Если изменить настройку Литейные сигналы перед суммированием, кодер обновит настройку Литейные сигналы перед суммированием.

Однако, явно задав параметр Привести перед суммой (Cast before sum), можно переопределить сигналы приведения перед установкой суммы, переданной из Конструктора фильтров (Filter Designer).

В Verilog кодер генерирует директивы шкалы времени (ˋtimescale) по умолчанию. Эта директива компилятора предоставляет способ указания различных значений задержки для нескольких модулей в файле Verilog.

Подавление использования ˋtimescale директивы,

Выберите вкладку Глобальные настройки (Global Settings) в диалоговом окне Создать ЛПВП (Generate HDL).

Выберите вкладку Дополнительно. Появится панель Дополнительно (Advanced).

Снимите флажок Использовать директивы Verilog ˋtimescale, как показано на следующем рисунке.

Альтернатива командной строки: generatehdl функция со свойством UseVerilogTimescale для подавления использования директив шкалы времени.

Кодер поддерживает комплексные коэффициенты и комплексные входные сигналы.

Для генерации портов и сигнальных трактов для действительной и мнимой составляющих комплексного входного сигнала задайте для параметра Сложность ввода значение Complex. Значение по умолчанию для сложности ввода: Realотключение формирования портов для сложных входных данных.

Соответствующее свойство командной строки: InputComplex. По умолчанию InputComplex имеет значение 'off'отключение формирования портов для сложных входных данных. Для включения генерации портов для сложных входных данных установите InputComplex кому 'on', как в следующем примере кода:

filt = design(fdesign.lowpass,'equiripple','Filterstructure','dffir','SystemObject',true); generatehdl(filt,numerictype(1,16,15),'InputComplex','on')

Следующий фрагмент кода VHDL показывает определение объекта, сгенерированное предыдущими командами:

ENTITY firfilt IS

PORT( clk : IN std_logic;

clk_enable : IN std_logic;

reset : IN std_logic;

filter_in_re : IN std_logic_vector(15 DOWNTO 0); -- sfix16_En15

filter_in_im : IN std_logic_vector(15 DOWNTO 0); -- sfix16_En15

filter_out_re : OUT std_logic_vector(37 DOWNTO 0); -- sfix38_En31

filter_out_im : OUT std_logic_vector(37 DOWNTO 0) -- sfix38_En31

);

END firfilt;

В фрагменте кода имена портов, сгенерированные для реальных компонентов сложных сигналов, имеют постфикс по умолчанию '_re'и имена портов, сгенерированные для мнимых компонентов комплексных сигналов, имеют постфикс по умолчанию '_im'.

Два свойства генерации кода позволяют настроить правила именования для действительных и мнимых компонентов сложных сигналов в сгенерированном коде HDL. Эти свойства:

Опция постфикса «Сложная вещественная часть» (соответствует ComplexRealPostfix свойство командной строки) определяет вектор символов, добавляемый к именам, генерируемым для действительной части сложных сигналов. Постфикс по умолчанию: '_re'.

Опция постфикса сложной мнимой части (соответствует ComplexImagPostfix свойство командной строки) определяет вектор символов, добавляемый к именам, генерируемым для мнимой части комплексных сигналов. Постфикс по умолчанию: '_im'.