Поведенческая модель интегральной схемы таймера

Simscape/Электрические/Интегральные схемы

Блок таймера является поведенческой моделью интегральной схемы таймера, такой как NE555.

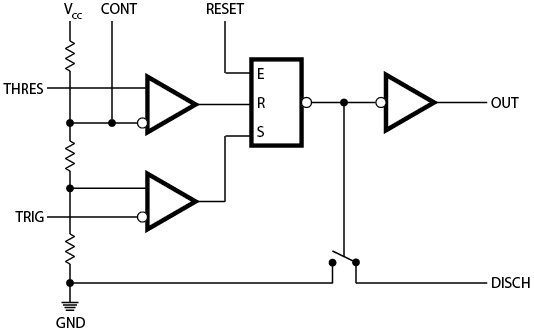

На следующем рисунке показана структура внедрения.

Параметр сопротивления компонента делителя потенциала задает значения трех резисторов, создающих делитель потенциала. Два входа компаратора имеют бесконечное входное сопротивление и нулевую входную емкость. Блок S-R-защелки обеспечивает функциональные возможности защелки установки-сброса. Он включает в себя выходной конденсатор и резистор со значениями, установленными так, чтобы соответствовать значению параметра задержки распространения. Блок моделирует инвертор выходного каскада с использованием блока CMOS NOT. Выходное сопротивление, низкое выходное напряжение и высокое выходное напряжение для вентиля CMOS определяются в диалоговом окне Блок таймера (Timer block). Разрядный переключатель аппроксимирует биполярный транзистор NPN на реальном таймере как переключатель с определенными значениями включенного и выключенного сопротивления.

Поведение абстрагировано. Результаты не так точны, как модель транзисторного уровня.

Задержка в ответ на изменение входных сигналов зависит исключительно от постоянной времени RC сети резистор-конденсатор на выходе защелки. На практике задержка имеет более сложную зависимость от структуры устройства. Установите это значение на основе времени нарастания и падения выходного импульса.

Падение выходного напряжения является линейной функцией выходного тока. На практике соотношение является соотношением двухтактной пары биполярных транзисторов.

Управляемое переключающее устройство, используемое блоком, является аппроксимацией устройства с открытым коллектором.

Источник питания подключается внутри компонента, и блок предполагает, что контакт GND заземлен.