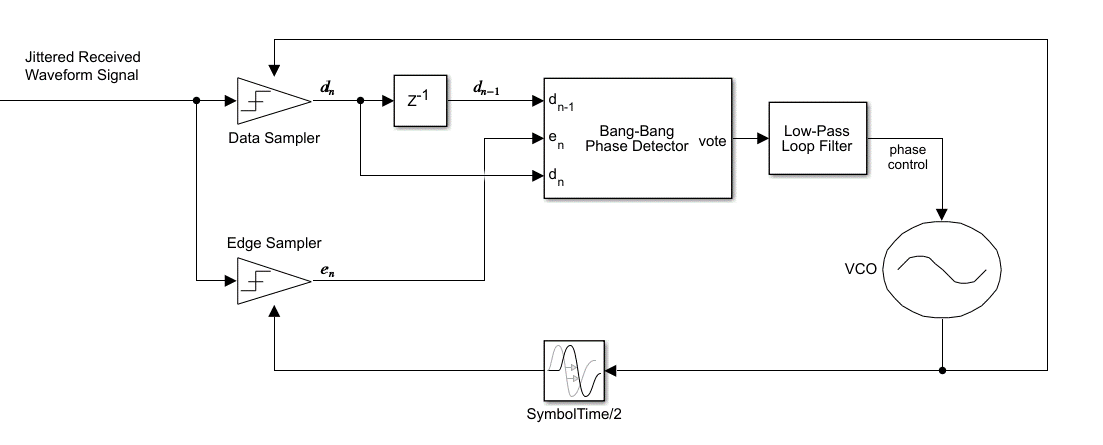

Высокоскоростные аналоговые системы SerDes используют схемы восстановления тактовой частоты и данных (CDR), чтобы извлечь надлежащее время для правильной выборки входящей формы сигнала. Схема CDR создает тактовый сигнал, который выравнивается по фазе и в некоторой степени по частоте передаваемого сигнала. Отслеживание фазы (CDR первого порядка) обычно осуществляется с помощью нелинейного детектора bang-bang или Alexander, который приводит в действие генератор, управляемый напряжением (ГУН). Отслеживание частоты (CDR второго порядка) интегрирует любые оставшиеся фазовые ошибки и компенсирует общие различия между опорным тактовым сигналом передатчика и опорным тактовым сигналом приемника. serdes.CDR и serdes.DFECDR использовать алгоритм CDR первого порядка.

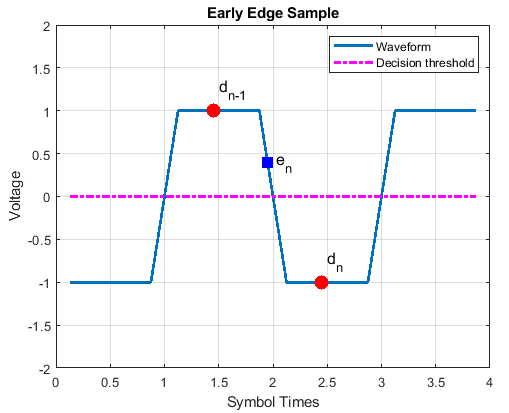

Детектор фазы Alexander или bang-bang производит выборку принятого сигнала на краю и середине каждого символа. Граничная выборка (en) и выборки данных (dn-1 и dn) обрабатываются некоторой цифровой логикой для определения, является ли граничная выборка и, следовательно, тактовая фаза ранней или поздней. Краевая выборка, en, и выборка данных, dn, разделены половиной времени символа.

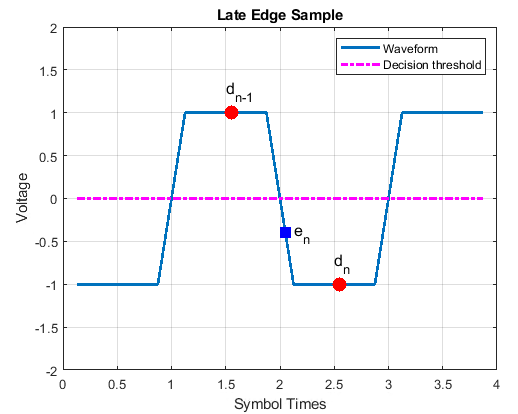

Рассмотрим форму сигнала, где произошел переход данных, и как en, так и dn ниже порогового напряжения принятия решения. Двоичные значения, разрешенные из en и dn, соответствуют, что указывает на запаздывание тактовой фазы.

Аналогично, когда двоичные значения, разрешенные из en и dn-1, совпадают, фаза синхронизации ранняя.

Представляя двоичный выход дискретизатора на ± 1, поведение фазового детектора для модуляции NRZ или PAM4 суммировано здесь:

| dn-1 | en | dn | Действие |

|---|---|---|---|

| −1 | −1 | 1 | Фаза синхронизации ранняя. Сдвиг фазы вправо. |

| 1 | 1 | −1 | |

| −1 | 1 | 1 | Фаза синхронизации запаздывает. Сдвиг фазы влево. |

| 1 | −1 | −1 | |

| −1 | X | −1 | Никаких действий не требуется. |

| 1 | X | 1 |

Для PAM3 модуляции уровни символов равны − 0,5, 0 и 0,5. Пороговые уровни по умолчанию (th) равны ± 0,25. Таким образом, измененная таблица истинности становится:

| dn-1 | en | dn | Действие |

|---|---|---|---|

| −0.5 | en > − th | 0 | поздно |

| −0.5 | en < − th | 0 | рано |

| −0.5 | en > 0 | 0.5 | поздно |

| −0.5 | en < 0 | 0.5 | рано |

| 0 | en > th | 0.5 | поздно |

| 0 | en < th | 0.5 | рано |

| 0 | en > − th | −0.5 | рано |

| 0 | en < − th | −0.5 | поздно |

| 0.5 | en > th | 0 | рано |

| 0.5 | en < th | 0 | поздно |

| 0.5 | en > 0 | −0.5 | рано |

| 0.5 | en < 0 | −0.5 | поздно |

Возбуждение ГУН непосредственно с выхода фазового детектора приводит к чрезмерному дрожанию тактового сигнала. Для устранения дрожания выходной сигнал фазового детектора фильтруется в нижних частотах путем накопления его в голосе. Когда накопленный голос превышает определенный порог подсчета, фаза ГУН увеличивается или уменьшается.

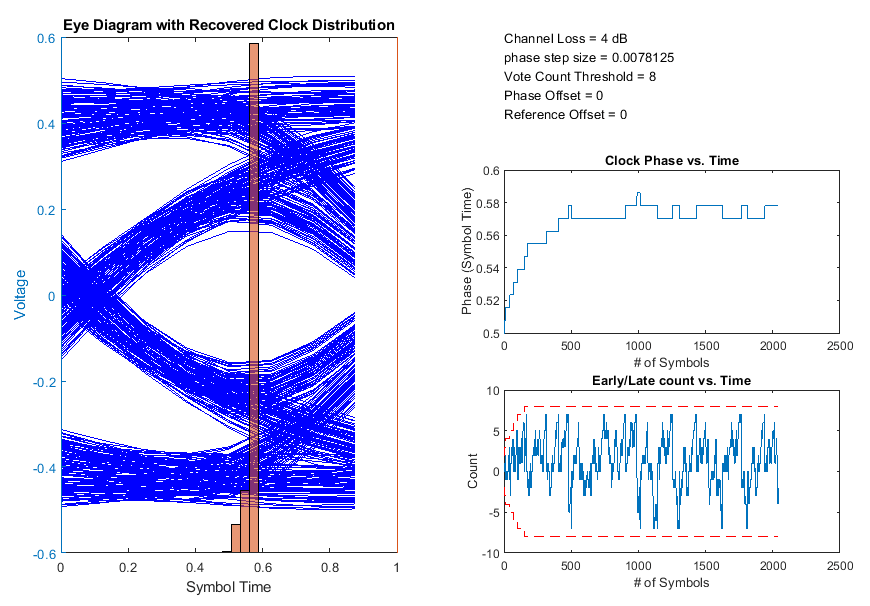

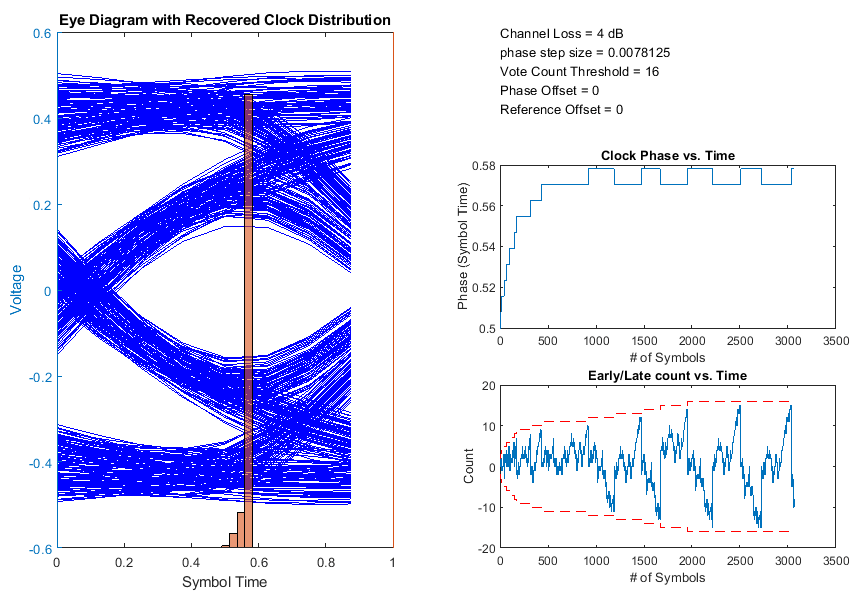

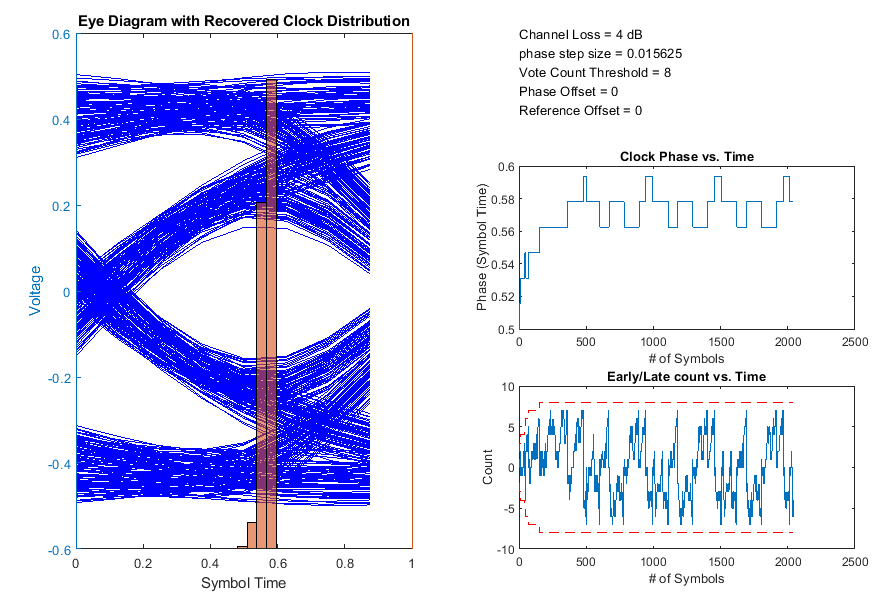

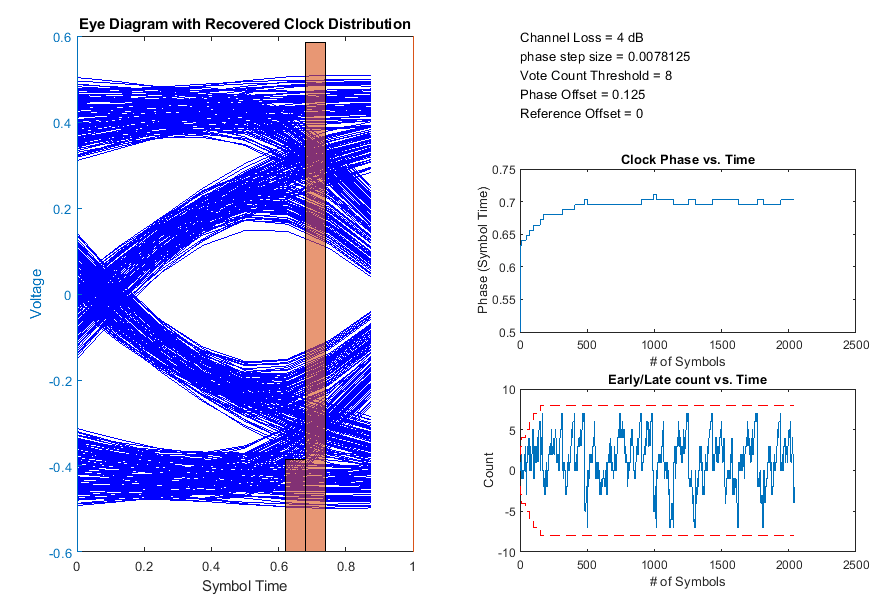

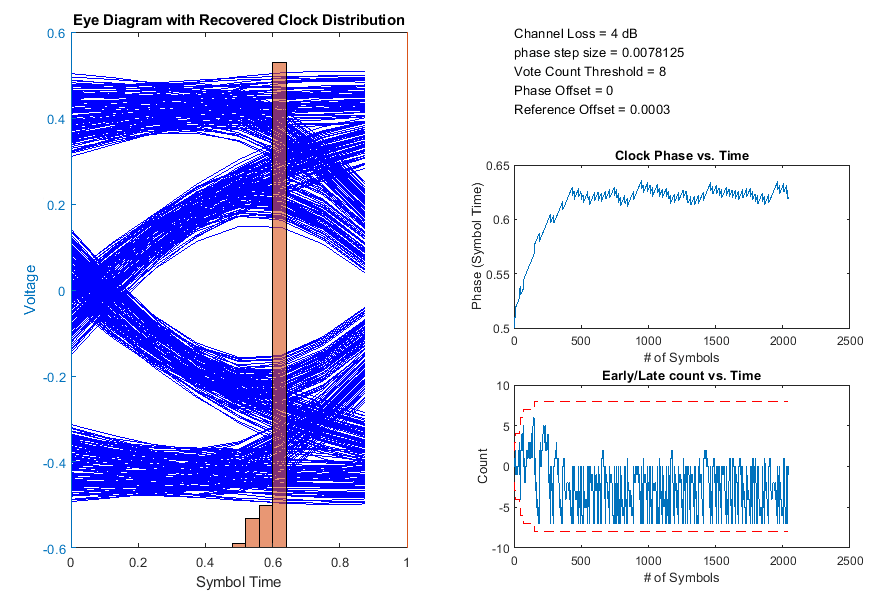

Восстановите тактовый сигнал из повторяющейся псевдослучайной двоичной последовательности (PRBS9), не возвращаемой в нулевой (NRZ) сигнал. Предположим, что канал имеет потери 4 дБ, размер шага фазы равен , порог подсчета голосов равен 8, и что нет сдвигов фаз или опорных смещений.

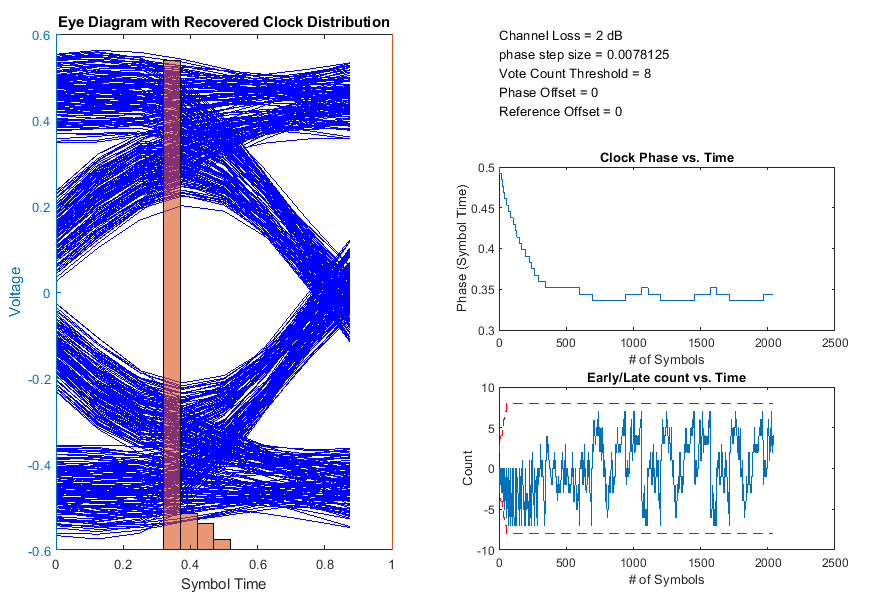

Базовое поведение показано с помощью диаграммы глаз и результирующей функции распределения вероятности синхронизации (PDF). PDF очень близко к центру глаза. Тактовая фаза устанавливается между значением 0,5703 и 0,5781. Колебание между двумя значениями является следствием нелинейного фазового детектора bang-bang и является источником дрожания поиска CDR. Для уменьшения величины расслоения уменьшите размер шага фазы. Чтобы сократить период рассогласования, уменьшите порог подсчета голосов.

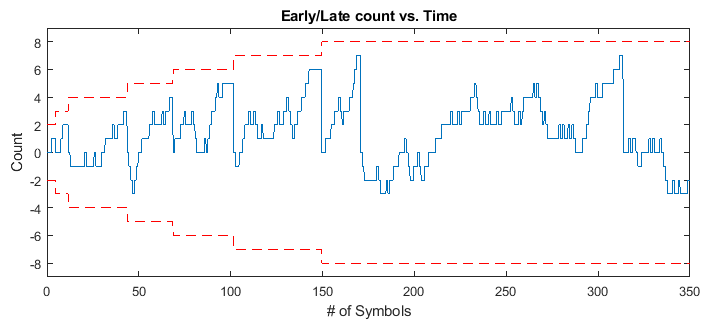

Выходной сигнал фазового детектора накапливается при раннем/позднем подсчете голосов. Когда подсчет превышает порог подсчета голосов, фаза увеличивается или уменьшается. Чтобы ускорить сходимость CDR, порог подсчета начинается с 2, и каждый раз, когда величина голосования превышает порог, порог увеличивается до тех пор, пока не достигнет максимального подсчета. На этом рисунке показаны первые 350 символов раннего/позднего счета (синий) и порог (пунктирная красная линия). Внутри блока CDR голос увеличивается или уменьшается, проверяется относительно порогового значения и при необходимости сбрасывается. Значение внешнего голосования, показанное на рисунке ниже, не затрагивает порог, но становится очевидным, когда голосование сбрасывается до 0.

Для отображения синхронизации, сходящейся к другой фазе, измените потери канала на 2 дБ. Фаза синхронизации теперь адаптируется к времени около 0,35 символа.

Увеличение порога подсчета голосов до 16 приводит к увеличению периода рассогласования.

Увеличение размера шага фазы до увеличивает величину расслоения.

Если выровненный глаз не отображает левую/правую симметрию, то при ручном сдвиге местоположения дискретизатора данных высота глаза может быть максимизирована. Например, сдвигать тактовую фазу вправо на символов времени для сдвига выходной тактовой фазы с 0,57 символа времени на 0,7 символа времени.

Для реализации более реалистичного CDR можно также ввести небольшую величину ослабления смещения опорной тактовой частоты.

[1] Sonntag, J. L. and Stonick, J. «Архитектура цифровых часов и восстановления данных для многогигабитных/двоичных каналов». IEEE Journal of Solid-State Circuits, 2006.

[2] Razavi, B. «Проблемы в проектировании высокоскоростных синхросигналов и схем восстановления данных». IEEE Communications Magazine, 2002.

CDR | DFECDR | serdes.CDR | serdes.DFECDR