В этом примере показано, как выполнить проверку модели во временной области с помощью блоков Simulink ® Design Optimization™ Model Verification. Во время проверки временной области программное обеспечение отслеживает сигнал, чтобы проверить, соответствует ли он характеристикам временной области, таким как характеристики ступенчатой реакции и верхняя и нижняя амплитуды, или отслеживает опорный сигнал.

Также можно использовать блоки из библиотек Simulink и Simulink Control Design™ Model Verification для разработки сложной логики утверждения для проверки во временной и частотной областях, а также мониторинга сигналов. Можно построить имитационные тесты для модели с помощью диспетчера верификации в построителе сигналов.

Откройте модель Simulink.

sys = 'sldo_model1_stepblk';

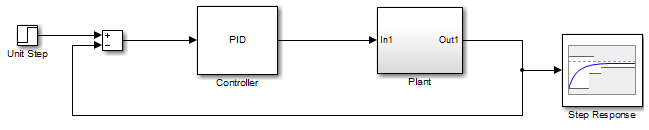

open_system(sys);

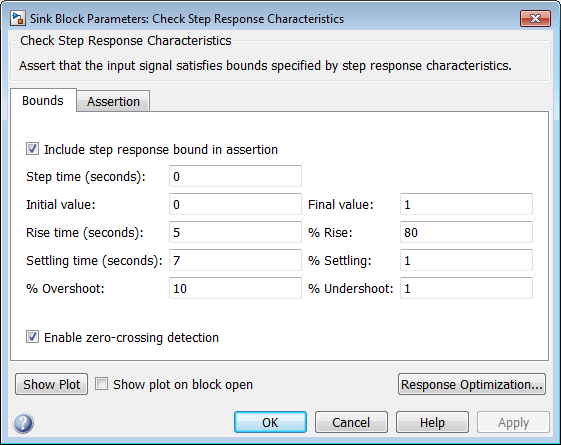

Модель включает в себя блок Step Response, который является блоком Check Step Response Characteristics из библиотеки Simulink Design Optimization Model Verification и имеет границы ответа шага по умолчанию.

В редакторе Simulink в разделе Simulation (Моделирование) нажмите кнопку Run (Выполнить).

Блок утверждает несколько раз во время моделирования, поскольку сигнал, к которому подключен блок, нарушает заданные границы. Предупреждения об утверждении появляются в окне команд MATLAB ®.

Параметры модели можно оптимизировать в соответствии с границами и исключить предупреждения об утверждении. См. раздел Оптимизация конструкции для удовлетворения требований к ответу на шаг (GUI).