Определение истинной длительности на входе и построение истинной длительности вывода на основе типа вывода

Программа Simulink Design Verifier

Истинная длительность сигнала - последовательные временные шаги, в течение которых сигнал является истинным

Длина истинной длительности сигнала - количество временных шагов, составляющих истинную длительность

Фаза обнаружения входных данных - фаза, завершенная на заключительном шаге времени ожидаемой продолжительности истинной длительности входных данных.

Фаза построения вывода - фаза, когда блок создает истинную длительность на выходе на основе типа вывода блока

Длительность задержки - количество временных шагов задержки после обнаружения входного сигнала, после которых выходной сигнал является истинным

Входы и выходы блока детектора имеют логический тип.

При обнаружении входного сигнала блок детектора создает выходной сигнал на основе одного из двух указанных типов выходного сигнала:

Delayed Fixed Duration- После завершения обнаружения входного сигнала и после дополнительной задержки выходной сигнал становитсяtrue для фиксированного количества временных шагов. Истинная продолжительность выходного сигнала не зависит от входного сигнала.

Synchronized- На заключительном временном шаге обнаружения входа выход становитсяtrue и остается true при условии, что входной сигнал продолжает оставаться true. Истинная продолжительность выходного сигнала изменяется и синхронизируется с истинной продолжительностью входного сигнала.

Укажите, может ли блок быть сброшен к началу обнаружения входа внешним логическим сигналом сброса.

Выбрать Delayed Fixed Duration (значение по умолчанию) для указания фиксированной длины истинной длительности вывода после необязательной задержки. Выбрать Synchronized для синхронизации истинной длительности выходного сигнала с длительностью входного сигнала.

Длина истинной длительности для обнаружения входных данных (не менее 1).

Для Delayed Fixed Duration, при необходимости укажите продолжительность задержки, после которой выходной сигнал становится истинным.

Для Delayed Fixed Duration, укажите длину выходного значения true duration (не менее 1).

В следующих примерах используйте время выборки 1 второй.

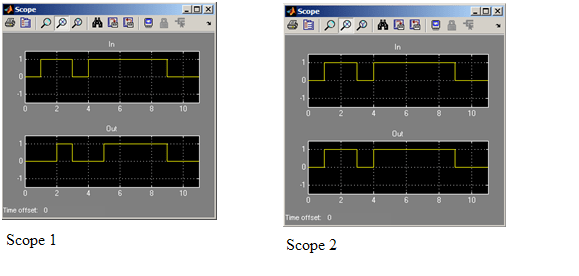

В этом примере для параметра «Тип вывода» установлено значение Delayed Fixed Durationфаза обнаружения входа не продолжается во время построения выходного сигнала. Следующие параметры блока для блока детектора устанавливаются следующим образом:

Временные шаги для обнаружения входных данных = 2

Временные шаги для задержки (необязательно) = 1

Временные шаги для длительности вывода = 2

Область 1 показывает сценарий, где второй true продолжительность не обнаружена, потому что некоторые из true временные шаги происходят во время построения выходных данных.

Однако второй true длительность в Области 2 обнаружена, так как оставшаяся true длительность после построения выходного сигнала удовлетворяет количеству шагов, необходимых для обнаружения входного сигнала.

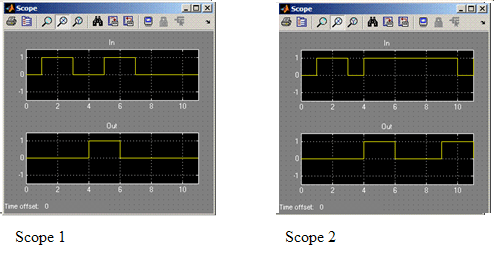

В этом примере для типа Output установлено значение Synchronized и Временные шаги для обнаружения входных данных, для которых установлено значение 2, выход становится true на заключительном этапе обнаружения входных данных. Выходной сигнал остается истинным до тех пор, пока входной сигнал true.

Область 1 показывает, что выходной сигнал становится истинным на втором временном шаге, который является последним временным шагом фазы обнаружения входного сигнала. Когда количество временных шагов для обнаружения входных данных установлено в 1, выходные данные идентичны входным данным, как показано в Области 2.