Определение целей проверки или тестирования без влияния на результаты моделирования или сгенерированный код

Программа Simulink Design Verifier

Этот блок является блоком подсистемы, который предварительно сконфигурирован в качестве отправной точки для создания подсистемы, определяющей цели проверки или тестирования для использования с программным обеспечением Simulink ® Design Verifier™.

Программное обеспечение Simulink Coder™ игнорирует блоки подсистемы проверки во время генерации кода, ведя себя так, как будто подсистемы не существуют. Блок «Подсистема проверки» позволяет добавлять компоненты Simulink Design Verifier в модель без влияния на созданный код.

Примечание

Если блок подсистемы верификации содержит блоки, зависящие от абсолютного времени, и для генерации кода выбирается целевой объект на основе ERT (Simulink Coder), установите для программной среды абсолютное время. Откройте диалоговое окно «Параметры конфигурации». На панели «Создание кода» > «Интерфейс» в разделе «Программная среда» выберите абсолютное время. Не выбирайте непрерывное время. Дополнительные сведения об этом параметре см. в разделе Поддержка: абсолютное время (встроенный кодер).

При сборе покрытия модели программное обеспечение Simulink Coverage™ записывает покрытие только для блоков Simulink Design Verifier в блоке Verification Subsystem; он не записывает покрытие для любых других блоков в подсистеме проверки.

Чтобы создать подсистему проверки в модели, выполните следующие действия.

Скопируйте блок «Подсистема проверки» из библиотеки Simulink Design Verifier в модель.

Откройте блок «Подсистема проверки», дважды щелкнув его.

В окне Verification Subsystem (Подсистема проверки) добавьте блоки, определяющие цели проверки или тестирования. Блоки Inport используются для представления входных данных вне подсистемы.

Блок подсистемы проверки в библиотеке Simulink Design Verifier предварительно настроен для работы с программным обеспечением Simulink Design Verifier. Блок подсистемы проверки должен:

Не содержат блоков Outport.

Включите параметр Treat as Atomic Unit.

Укажите его параметр типа Mask как VerificationSubsystem.

Если изменить блок «Подсистема проверки» так, чтобы не были выполнены предыдущие условия, программа Simulink Design Verifier отобразит предупреждение.

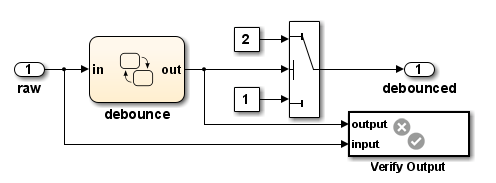

sldvdemo_debounce_validprop пример модели включает в себя подсистему проверки, называемую верификацией выходных данных, как показано на рисунке ниже.

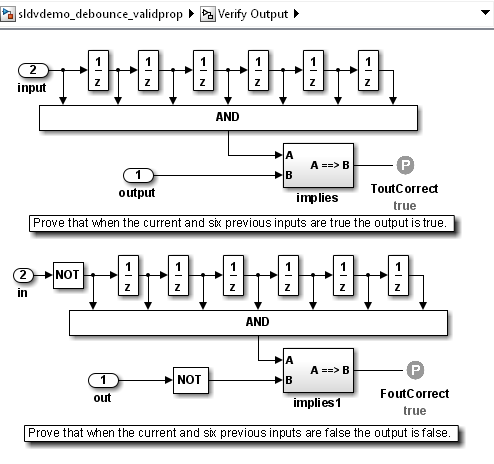

Подсистема Verify Output определяет две цели проверки, подробно описанные на следующем рисунке.