Во время анализа обнаружения ошибок конструкции программное обеспечение проверяет указанные минимальное и максимальное значения на промежуточных сигналах в модели и на выходных портах. Эти значения определяют проектные диапазоны.

Анализ проверяет указанные минимальное и максимальное значения на:

Выходы блоков Simulink ®, за исключением ограничений, описанных в следующем разделе

Simulink.Signal объекты

Объекты данных Stateflow ®

MATLAB ® для объектов данных генерации кода

Записи в глобальное хранилище данных

Если анализ обнаруживает, что сигнал превышает проектный диапазон, результаты определяют, где в модели произошли ошибки. Кроме того, можно создать модель кабельных трасс, содержащую тестовые примеры, демонстрирующие, как произошла ошибка.

При анализе проверки модели, если указанные минимальное и максимальное значения превышены, программа не может проверить минимальное и максимальное значения, указанные в:

Любой блок мультиплексора с выходом, подключенным к блоку селектора

Объединять входы блоков

Чтобы обойти это ограничение, используйте Simulink.Signal объект на выходе блока объединения и укажите диапазон на Simulink.Signal объект.

Примечание

Сведения о том, как анализ Simulink Design Verifier™ обрабатывает указанные минимальные и максимальные значения на входных портах, см. в разделе Минимальные и максимальные входные ограничения.

В этом разделе рассматривается создание и анализ модели, для которой заданы минимальные и максимальные значения проекта:

Порты ввода

Выходные порты двух промежуточных блоков

Анализ обнаружения ошибок проекта определяет блоки, выходные значения которых превышают проектный диапазон. Если анализ обнаруживает эту ошибку, в этом примере показано, как анализ использует указанные минимальное и максимальное значения при продолжении анализа.

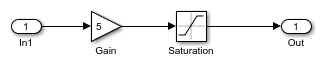

Создайте модель для этого примера:

На панели инструментов MATLAB на вкладке Главная (Home) выберите Создать (New) > Модель Simulink (Simulink Model).

Из библиотеки часто используемых блоков Simulink добавьте в модель следующие блоки и назначьте указанные значения параметров.

| Блок | Счет | Параметр | Стоимость |

|---|---|---|---|

| Inport | Атрибуты сигнала | Минимум | 0 |

| Inport | Атрибуты сигнала | Максимум | 5 |

| Выгода | Главный | Выгода | 5 |

| Выгода | Атрибуты сигнала | Минимум выходных данных | 0 |

| Выгода | Атрибуты сигнала | Максимальное выходное значение | 20 |

| Выгода | Атрибуты сигнала | Тип выходных данных | int16 |

| Насыщенность | Главный | Верхний предел | 25 |

| Насыщенность | Главный | Нижний предел | -25 |

| Насыщенность | Атрибуты сигнала | Минимум выходных данных | -25 |

| Насыщенность | Атрибуты сигнала | Максимальное выходное значение | 25 |

| Вспомогательный порт | Без изменений | ||

Подключите четыре блока, как показано на рисунке.

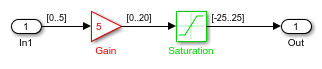

Для отображения указанных минимального и максимального значений на вкладке «Отладка» выберите «Информационные наложения» > «Диапазоны данных сигнала».

На вкладке Моделирование (Modeling) щелкните Параметры модели (Model Settings).

В диалоговом окне Параметры конфигурации (Configuration Parameters) на панели Решатель (Solver) в разделе Выбор решателя (Solver selection):

Задать тип для Fixed-step.

Программа Simulink Design Verifier не поддерживает решатели с переменным шагом.

Задать для решателя значение discrete (no continuous states).

На панели Design Verifier установите для параметра Режим значение Design error detection.

На панели «Проверка конструкции» > «Обнаружение ошибок конструкции»:

Выберите Указанные нарушения минимального и максимального значений.

Сбросьте параметры Переполнение целых чисел (Integer overflow) и Деление (Division) на ноль.

В этом примере проверяется наличие только промежуточных минимальных и максимальных нарушений.

Чтобы сохранить эти настройки и выйти из диалогового окна Параметры конфигурации (Configuration Parameters), нажмите кнопку ОК.

Сохраните модель и присвойте ей имя ex_interim_minmax.

Чтобы проанализировать примерную модель для выявления любых промежуточных сигналов, которые нарушают указанные минимальное и максимальное значения, выполните анализ обнаружения ошибок конструкции.

На вкладке «Проверка проекта» выберите «Обнаружение ошибок проекта».

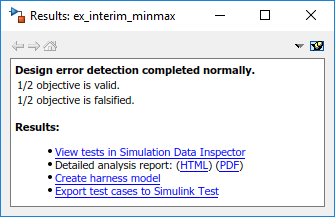

После завершения анализа:

Программа выделяет модель с результатами анализа.

Диалоговое окно Simulink Design Verifier Results открывает и показывает резюме анализа.

В окне модели блок усиления окрашен в красный цвет, а блок насыщения - в зеленый. Это означает, что:

По крайней мере одна цель, связанная с блоком Gain, была сфальсифицирована. Для этого примера анализ сфальсифицировал ровно одну цель.

Все цели, связанные с блоком Насыщения, выполнены. Для этого примера анализ удовлетворял ровно одной цели.

Чтобы понять эти результаты:

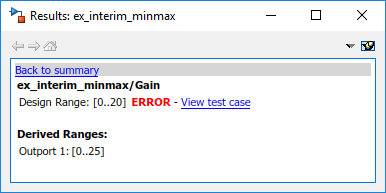

Щелкните блок усиления.

В окне Simulink Design Verifier Results (Результаты Simulink Design Verifier) показано, что диапазон проектирования для выходных данных составлял [0.. 20], но анализ обнаружил ошибку и создал тестовый пример, демонстрирующий эту ошибку. Поскольку расчетный диапазон для входного блока равен [0.. 5], при 5 входного сигнала для блока усиления выходной сигнал равен 25, что превышает указанное максимальное значение для этого порта.

Анализ вычисляет и отображает производный диапазон, чтобы понять, как был превышен проектный диапазон.

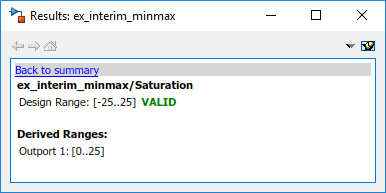

Щелкните на блоке «Насыщенность».

Окно Simulink Design Verifier Results показывает, что выходные данные блока насыщенности никогда не превышали проектный диапазон [-25.. 25]. Входной сигнал блока Насыщения никогда не превышал [0.. 25], который является производным диапазоном, который анализ распространил из блока усиления.

После завершения анализа можно создать модель кабельных трасс, содержащую контрольные примеры, которые приводят к ошибкам.

В примере модели просмотрите тестовый случай, вызвавший ошибку диапазона проектирования в блоке усиления:

После завершения анализа и выделения модели щелкните блок усиления.

В окне Результатов Свидетельства Дизайна Simulink нажмите прецедент View.

Программа создает модель кабельных трасс с именем ex_interim_minmax_harness и открывает блок Построитель сигналов (Signal Builder) в модели кабельных трасс, содержащей тестовый пример.

В блоке Signal Builder один тестовый случай, значение сигнала которого равно 5, привел к тому, что выходной сигнал блока усиления составил 25, что превышает указанный максимум 20.

Перед моделированием этого теста в диалоговом окне «Параметры конфигурации» на панели «Диагностика» > «Валидность данных» установите для параметра «Проверка диапазона моделирования» значение warning или error.

Установка этого параметра определяет действие диагностики, выполняемое при обнаружении Simulink сигналов, превышающих указанные минимальные или максимальные значения во время моделирования.

При указании warning, моделирование отображает предупреждающее сообщение и продолжается.

При указании error, моделирование отображает сообщение об ошибке и останавливается.

Нажмите кнопку ОК, чтобы сохранить изменения и закрыть диалоговое окно Параметры конфигурации (Configuration Parameters).

В окне блока Построитель сигналов (Signal Builder) щелкните Начало моделирования (Start simulation), чтобы смоделировать модель с помощью этого тестового случая.

Как и ожидалось, в окне MATLAB при моделировании отображается предупреждение или ошибка о том, что выходное значение блока усиления превышает заданный максимум.

Можно также создать HTML-отчет, содержащий подробную информацию об аналитическом отчете для ex_interim_minmax модель. Чтобы создать этот отчет, в окне Результатов Свидетельства Дизайна Simulink, нажимают отчет о подробном анализе Generate. Отчет об анализе открывается в браузере.

В отчете об анализе в главе «Состояние целей обнаружения ошибок проектирования» отчета представлены подробные результаты по двум категориям:

Targets Proven Valid - выходные значения блока насыщения всегда находятся в пределах проектного диапазона.

Цели, сфальсифицированные в тестовых примерах - выходные значения блока усиления нарушают проектный диапазон.