Автоматическое блокирование позволяет анализировать модель, содержащую объекты, которые Simulink ® Design Verifier™ не поддерживает.

При включении опции автоматической остановки (она включена по умолчанию) программа учитывает только интерфейс неподдерживаемых объектов, а не их фактическое поведение. Этот метод позволяет программному обеспечению завершить анализ. Однако анализ может давать только частичные результаты, если какой-либо неподдерживаемый элемент модели влияет на результат моделирования.

Если включить автоматическое блокирование, когда анализ Simulink Design Verifier приходит к неподдерживаемому блоку, программное обеспечение блокирует этот блок. Анализ игнорирует поведение блока, и в результате вывод блока может принимать любое значение.

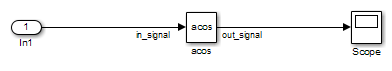

Simulink Design Verifier не поддерживает тригонометрические функциональные блоки, если для параметра Function установлено значение acos, например, на следующем рисунке.

При блокировании этого блока во время анализа out_signal может принимать любое значение со следующими результатами.

| Модель анализа | Результат упора out_signal |

|---|---|

Обнаружение ошибок конструкции |

|

Создание тестового случая |

|

Проверка свойств |

|

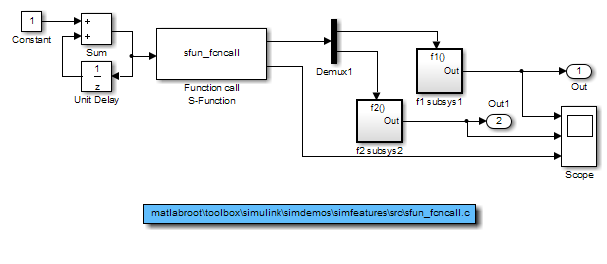

Пример модели Simulink sfcndemo_sfun_fcncall имеет S-функциональный блок. S-функция sfun_fcncall запускает выполнение подсистем f1 subsys1 и f2 subsys2 функционального вызова на первом и втором элементах первого выходного порта.

Если поддержка S-функции в Simulink Design Verifier не включена, а автоматическое блокирование включено, анализ игнорирует поведение S-функции. В результате код, запускающий две подсистемы вызова функций, игнорируется, что приводит к двум неудовлетворительным целям. Поскольку вызовы функций игнорируются, содержимое этих подсистем эффективно исключается из анализа.

Чтобы включить поддержку S-функции в Simulink Design Verifier, см. раздел Ограничения поддержки и рекомендации по S-функциям и коду C/C + +

В этом разделе описывается рабочий процесс использования автоматического stubbing с простой моделью Simulink в качестве примера.

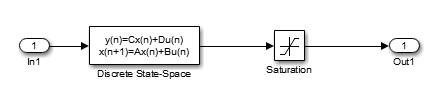

Следующая модель содержит блок дискретного состояния пространства, который несовместим с Simulink Design Verifier.

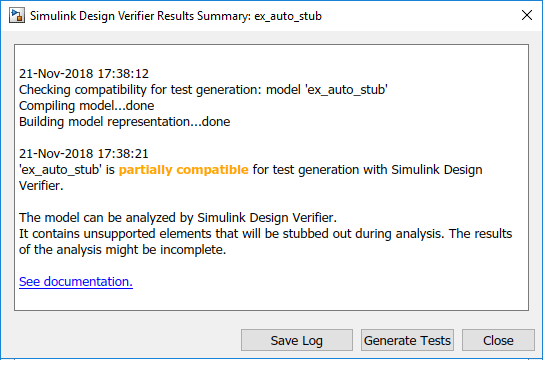

В редакторе Simulink существует два способа проверки совместимости модели с Simulink Design Verifier: проверка совместимости Simulink Design Verifier или выполнение анализа Simulink Design Verifier.

Чтобы запустить проверку совместимости Simulink Design Verifier:

На вкладке «Проверка проекта» нажмите кнопку «Проверить совместимость».

Выберите анализ, который требуется выполнить.

Чтобы выполнить анализ Simulink Design Verifier, на вкладке Design Verifier в разделе Режим (Mode) выберите любую из следующих опций.

Выберите «Обнаружение ошибок конструкции», затем щелкните «Обнаружение ошибок конструкции».

Выберите Генерация тестов и нажмите Генерация тестов.

Выберите Проверка свойств, затем нажмите Доказать свойства.

Программное обеспечение сначала проверяет совместимость модели. Если сама модель несовместима, например, если она использует решатель с переменным шагом, анализ не может быть продолжен.

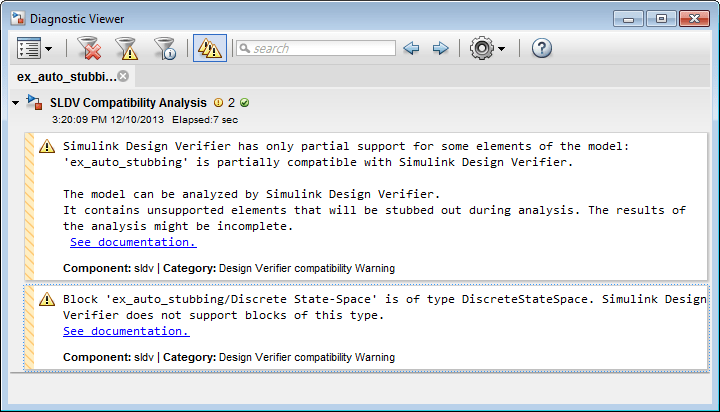

При обнаружении несовместимых элементов в модели программа анализирует модель и по умолчанию выключает несовместимые элементы. Откроется также Средство просмотра диагностики (Diagnostic Viewer) со списком несовместимостей.

Примечание

Дополнительные сведения см. в разделе Просмотр диагностики.

Автоматическое блокирование включено по умолчанию. Чтобы изменить параметр автоматической остановки, в диалоговом окне «Параметры конфигурации» на главной панели Design Verifier выберите параметр «Автоматическая блокировка неподдерживаемых блоков и функций». При выполнении анализа программа сообщает, что остановка включена, и анализ продолжается.

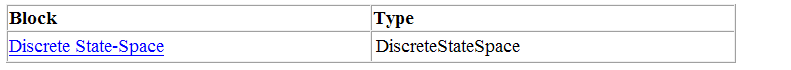

При выполнении анализа с включенным автоматическим stubbing обязательно просмотрите результаты. В этом отчете, созданном после анализа генерации тестового случая, отображается таблица неподдерживаемых блоков, обнаруженных программным обеспечением.

Неподдерживаемые блоки

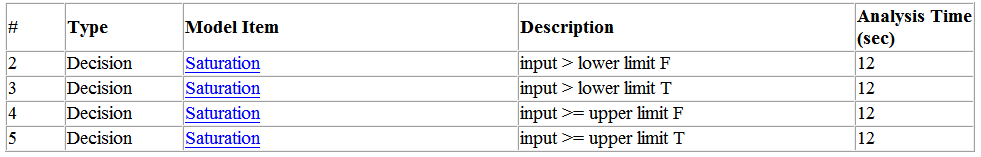

Созданный аналитический отчет для примерной модели показывает, что цели не определены из-за тупика. Программное обеспечение не может генерировать тестовые примеры, поскольку оно не понимает работу блока дискретного состояния-пространства.

Цель не определена из-за тупицы

Если анализ не дает полных результатов из-за тупика, можно определить пользовательские замены блоков, чтобы дать более точное определение неподдерживаемых блоков. Дополнительные сведения см. в разделе Замены блоков для неподдерживаемых блоков.