В этом примере используется slvnvdemo_powerwindow , чтобы показать, как проверить компонент в контексте модели, содержащей этот компонент. При работе с этим примером используются функции проверки компонентов Simulink ® Design Verifier™ для создания тестовых примеров и измерения покрытия для ссылочной модели. Кроме того, ссылочную модель можно выполнить как в режиме моделирования, так и в режиме программного обеспечения в цикле (SIL) с помощью API проверки генерации кода (CGV).

Примечание

Для выполнения этого примера необходимо иметь следующие лицензии на продукты:

Поток данных Stateflow ®

Встроенный кодер ®

Симулинк Coder™

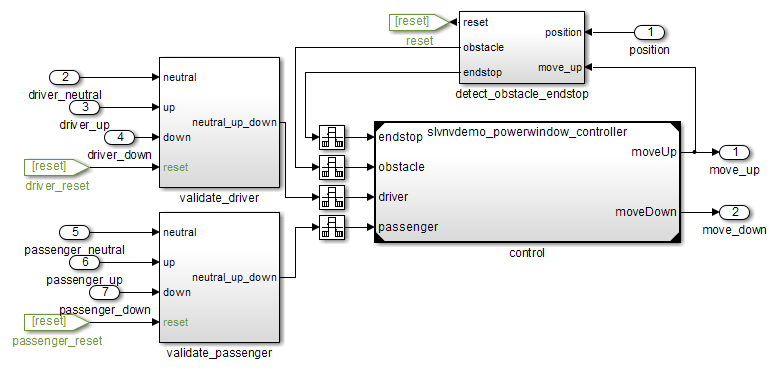

Проверяемый компонент является блоком модели с именем control. Этот компонент находится внутри power_window_control_system подсистема на верхнем уровне slvnvdemo_powerwindow модель. power_window_control_system подсистема показана ниже.

control

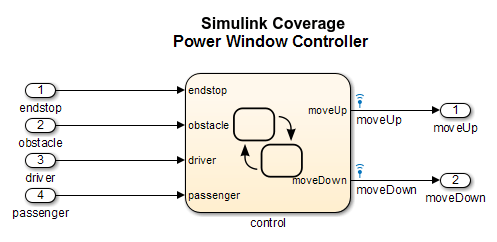

Блок модели ссылается на slvnvdemo_powerwindow_controller модель.

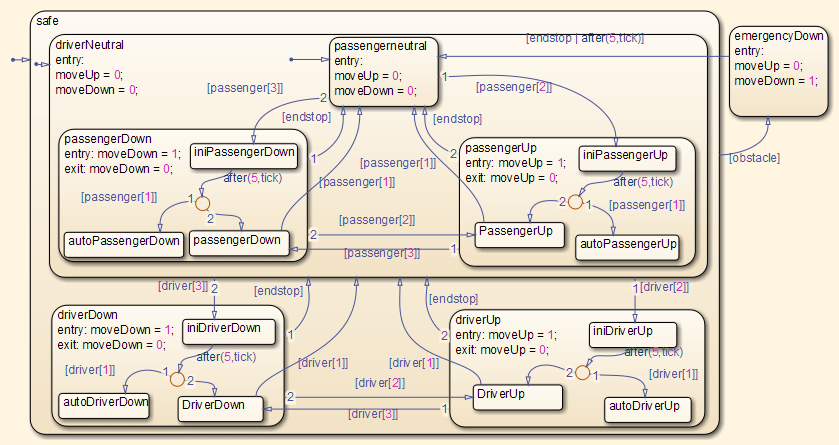

Ссылочная модель содержит диаграмму Stateflow control, который реализует логику для контроллера окна питания.

Проверка ссылочной модели slvnvdemo_powerwindow_controllerсоздайте модель электрического жгута, которая содержит входные сигналы, моделирующие контроллер в модели завода:

Откройте окно slvnvdemo_powerwindow пример модели и ссылочная модель:

open_system('slvnvdemo_powerwindow'); open_system('slvnvdemo_powerwindow_controller');

Откройте окно power_window_control_system в примерной модели.

Блок модели с именем control в power_window_control_system подсистема ссылается на компонент, проверенный в этом примере, slvnvdemo_powerwindow_controller.

Моделирование блока модели, который ссылается на slvnvdemo_powerwindow_controller модель и протоколирование входных сигналов в блок Модель:

loggedSignalsPlant = sldvlogsignals( ... 'slvnvdemo_powerwindow/power_window_control_system/control');

sldvlogsignals сохраняет зарегистрированные сигналы в loggedSignalsPlant.

Создайте модель электрического жгута с зарегистрированными сигналами:

harnessModelFilePath = sldvmakeharness( ... 'slvnvdemo_powerwindow_controller', loggedSignalsPlant);

sldvmakeharness создает и открывает модель кабельных трасс с именем slvnvdemo_powerwindow_controller_harness. Блок Signal Builder содержит один тестовый пример, содержащий записанные сигналы.

Дополнительные сведения о моделях кабелей см. в разделе Simulink Design Verifier Модели кабелей.

Для последующего использования в этом примере сохраните имя модели кабельных трасс:

[~, harnessModel] = fileparts(harnessModelFilePath);

Оставьте все окна открытыми для следующей части этого примера.

Далее вы запишете покрытие для slvnvdemo_powerwindow_controller модель.

Охват модели - это показатель того, насколько тщательно тестовый случай тестирует модель, и процент путей, которые выполняет тестовый случай. Запись покрытия для slvnvdemo_powerwindow_controller модель:

Создайте объект параметров по умолчанию, необходимый для sldvruntest функция:

runOpts = sldvruntestopts;

Укажите, чтобы смоделировать модель и записать покрытие:

runOpts.coverageEnabled = true;

Моделирование ссылочной модели и покрытия записей:

[~, covDataFromLoggedSignals] = sldvruntest( ... 'slvnvdemo_powerwindow_controller', loggedSignalsPlant, runOpts);

Просмотрите отчет о покрытии в формате HTML:

cvhtml('Coverage with Test Cases', covDataFromLoggedSignals); slvnvdemo_powerwindow_controller модель достигнута:

Охват принятием решений: 40%

Охват условиями: 35%

Охват MCDC: 10%

Дополнительные сведения о покрытии решений, покрытии условий и покрытии MCDC см. в разделе Типы покрытия модели (покрытие Simulink).

Потому что вы не достигли 100% покрытия для slvnvdemo_powerwindow_controller Далее модель анализируется для записи дополнительного покрытия и создания дополнительных тестовых примеров.

Вы можете использовать Simulink Design Verifier для анализа slvnvdemo_powerwindow_controller моделирование и сбор покрытия. Можно указать, что анализ игнорирует любые ранее выполненные цели и записывает дополнительное покрытие.

Для записи дополнительного покрытия для модели:

Сохраните данные покрытия, записанные для зарегистрированных сигналов, в файле:

cvsave('existingCovFromLoggedSignal', covDataFromLoggedSignals);Создайте объект опций по умолчанию для анализа:

opts = sldvoptions;

Укажите, что анализ генерирует тестовые примеры для записи решения, условия и покрытия измененного условия/решения:

opts.ModelCoverageObjectives = 'MCDC';Укажите, что анализ игнорирует цели, удовлетворяемые при регистрации сигналов в блоке Модель (Model):

opts.IgnoreCovSatisfied = 'on';Укажите имя файла, содержащего удовлетворенные целевые данные:

opts.CoverageDataFile = 'existingCovFromLoggedSignal.cvt';Укажите, что анализ создает длительные тестовые примеры, удовлетворяющие нескольким целям:

opts.TestSuiteOptimization = 'LongTestcases';Создание меньшего числа тестовых примеров, каждый из которых удовлетворяет нескольким целям тестирования, экономит время при выполнении созданного кода в следующем разделе.

Укажите, чтобы создать модель электрического жгута, которая ссылается на компонент с помощью блока «Модель»:

opts.saveHarnessModel = 'on'; opts.ModelReferenceHarness = 'on';

Модель электрического жгута, созданная на основе зарегистрированных сигналов в разделе «Подготовка компонента к проверке», использует блок модели, который ссылается на slvnvdemo_powerwindow_controller модель. В модели кабельных трасс, которую создает анализ, также должен использоваться блок модели, который ссылается на slvnvdemo_powerwindow_controller. Можно добавить данные тестового примера к первой модели кабельных трасс, создав единый набор тестов.

Проанализируйте модель с помощью Simulink Design Verifier:

[status, fileNames] = sldvrun('slvnvdemo_powerwindow_controller', ... opts, true);

Анализ создает и открывает модель электрического жгута slvnvdemo_powerwindow_controller_harness. Блок Signal Builder содержит один длинный тестовый пример, удовлетворяющий 74 контрольным целям.

Этот тестовый случай можно объединить с тестом, созданным в окне Подготовка компонента к проверке, для записи дополнительного покрытия для slvnvdemo_powerwindow_controller модель.

Сохраните имя новой модели электрического жгута и откройте ее:

[~, newHarnessModel] = fileparts(fileNames.HarnessModel); open_system(newHarnessModel);

Затем необходимо объединить две модели кабельных трасс для создания единого набора тестов.

Две модели кабельных трасс были созданы при выполнении следующих действий:

Регистрируют сигналы в блоке модели управления, который ссылается на slvnvdemo_powerwindow_controller модель.

Проанализировал slvnvdemo_powerwindow_controller модель.

При объединении тестовых примеров в обеих моделях кабельных трасс можно записать покрытие, которое приближает вас к достижению 100% покрытия:

Объедините модели кабельных трасс путем добавления последних тестовых примеров к тестовым случаям для регистрируемых сигналов:

sldvmergeharness(harnessModel, newHarnessModel);

Блок построителя сигналов в slvnvdemo_powerwindow_controller_harness модель теперь содержит оба тестовых случая.

Запишите сигналы в модель электрического жгута:

loggedSignalsMergedHarness = sldvlogsignals(harnessModel);

Использование комбинированных тестовых примеров для регистрации покрытия для slvnvdemo_powerwindow_controller_harness модель. Сначала настройте объект options для sldvruntest:

runOpts = sldvruntestopts; runOpts.coverageEnabled = true;

Смоделировать модель и записать и просмотреть данные покрытия:

[~, covDataFromMergedSignals] = sldvruntest( ... 'slvnvdemo_powerwindow_controller', loggedSignalsMergedHarness, ... runOpts); cvhtml('Coverage with Merged Test Cases', covDataFromMergedSignals);

slvnvdemo_powerwindow_controller модель теперь достигает:

Охват принятием решений: 100%

Охват условиями: 80%

Охват MCDC: 60%

Чтобы убедиться, что созданный код для модели дает те же результаты, что и при моделировании модели, используйте методы API проверки генерации кода (CGV).

Примечание

Для выполнения модели в различных режимах выполнения используйте API CGV для проверки числовой эквивалентности результатов. Дополнительные сведения о CGV API см. в разделе Программная проверка генерации кода (встроенный кодер).

При выполнении этой процедуры моделирование компилирует и выполняет код модели с использованием обоих тестовых примеров.

Создание объекта параметров по умолчанию для sldvruncgvtest:

runcgvopts = sldvruntestopts('cgv');Укажите выполнение модели в режиме моделирования:

runcgvopts.cgvConn = 'sim';Выполните команду slvnv_powerwindow_controller модель с использованием двух тестовых случаев и runcgvopts объект:

cgvSim = sldvruncgvtest('slvnvdemo_powerwindow_controller', ... loggedSignalsMergedHarness, runcgvopts);

Эти шаги позволяют сохранить результаты в переменной рабочей области. cgvSim.

Затем выполните одну и ту же модель с одинаковыми тестовыми примерами в режиме программного обеспечения в цикле (SIL) и сравните результаты обоих моделирований.

Дополнительные сведения о режиме нормального моделирования см. в разделе Выполнение модели (встроенный кодер).

При выполнении модели в режиме программного обеспечения в цикле (SIL) моделирование компилирует и выполняет сгенерированный код на главном компьютере.

В этом разделе выполняется slvnvdemo_powerwindow_controller модель в режиме SIL и сравнить результаты с предыдущим разделом при выполнении модели в режиме моделирования.

Укажите выполнение модели в режиме SIL:

runcgvopts.cgvConn = 'sil';Выполните команду slvnv_powerwindow_controller модель с использованием двух тестовых случаев и runcgvopts объект:

cgvSil = sldvruncgvtest('slvnvdemo_powerwindow_controller', ... loggedSignalsMergedHarness, runcgvopts);

Переменная рабочей области cgvSil содержит результаты выполнения режима SIL.

Сравнение результатов в cgvSil к результатам в cgvSim, созданный при выполнении режима моделирования. Используйте compare (Embedded Coder)

for i=1:length(loggedSignalsMergedHarness.TestCases) simout = cgvSim.getOutputData(i); silout = cgvSil.getOutputData(i); [matchNames, ~, mismatchNames, ~ ] = ... cgv.CGV.compare(simout, silout); end

Результаты сравнения отображаются в окне команд MATLAB ®:

fprintf(['\nTest Case(%d):%d Signals match, %d Signals mismatch\r'],... i, length(matchNames), length(mismatchNames));

Как и ожидалось, результаты двух симуляций совпадают.

Дополнительные сведения о моделировании ПО в цикле (SIL) см. в разделе Что такое моделирование SIL и PIL? (Встроенный кодер).