В этом учебном пособии описываются шаги по созданию аппаратных и программных исполняемых файлов для модели и выполнения приложения. Модель SoC может содержать модель процессора, модель FPGA или и то, и другое.

SoC Builder требует установки пакета поддержки на основе платы, выбранной в параметрах конфигурации. Дополнительные сведения см. в разделе Оборудование, поддерживаемое блоками SoC.

Для создания двоичных файлов SoC необходимо включить в системный путь путь к исполняемым файлам Vivado ® или Quartus ®. Если исполняемые файлы еще не указаны в системном пути, используйтеhdlsetuptoolpath , чтобы добавить их в свой путь.

На панели инструментов Simulink ® на вкладке «Система на кристалле» нажмите кнопку «Настроить, построить и развернуть».

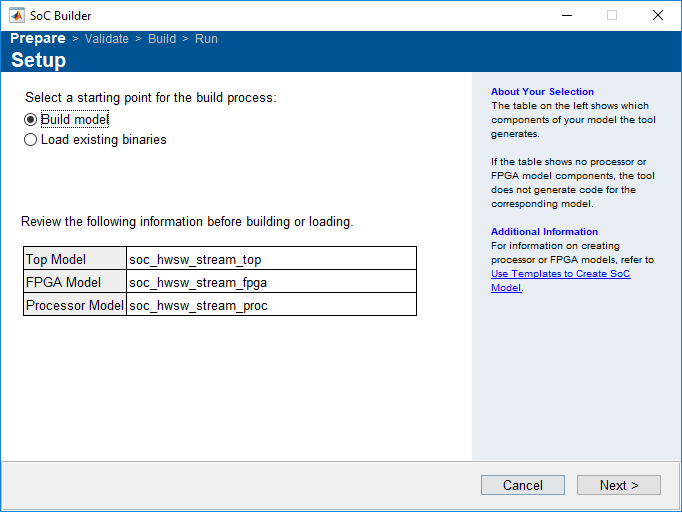

Подготовьте модель, выбрав начальную точку для процесса построения, а затем просмотрите информацию о модели.

Примечание

Если пакет поддержки не обнаружен, SoC Builder сначала предлагает установить требуемый пакет поддержки.

Укажите начальную точку для процесса построения. При построении модели, которая ранее не создавалась, выберите Компоновать модель (Build model). Если ранее вы завершили процесс построения и сохранили двоичные файлы в папке, выберите Загрузить существующие двоичные файлы.

SoC Builder анализирует модель и отображает верхнюю модель, модель FPGA (если она существует) и модель ARM (если она существует). Проверьте эту информацию на точность. Если это кажется неправильным, отредактируйте модель, сохраните и перезапустите инструмент SoC Builder.

Примечание

Если для модели FPGA задан вариант модели Simulink на основе кадра, то построитель SoC не отображает модель в таблице. Чтобы сделать его видимым в таблице, задайте вариант модели на основе образца и перекомпилируйте конструкцию.

Нажмите кнопку Далее.

На следующей странице SoC Builder представлена информация о карте памяти модели. Чтобы открыть средство сопоставления памяти, нажмите «Просмотр/Редактирование». Просмотрите базовые адреса и смещения и при необходимости отредактируйте их.

Примечание

Этот шаг карты памяти SoC Builder виден только при наличии модели FPGA в верхней модели. Если модель FPGA настроена на моделирование на основе кадров, то модель FPGA не отображается, и поэтому нет доступа к средству сопоставления памяти.

Нажмите кнопку Далее.

Укажите путь к папке проекта, введя путь в текстовом поле «Папка проекта» или перейдя в папку. SoC Builder помещает все созданные файлы, включая отчеты, исполняемые файлы и битовый поток, в указанную папку.

Если в качестве начальной точки для процесса построения выбран параметр «Загрузить существующие двоичные файлы», укажите расположение папки проекта для предыдущих двоичных файлов и отчетов.

Нажмите кнопку Далее.

В разделе Выбрать действие построения выберите одну из следующих опций.

Построить, загрузить и выполнить - выберите этот параметр для генерации кода HDL и C, создания исполняемых файлов программного обеспечения и файла программирования FPGA из модели. После создания SoC Builder загружает сгенерированный код на плату FPGA и выполняет приложение.

Только сборка - выберите этот параметр для генерации кода HDL и C, создания исполняемых файлов программного обеспечения и файла программирования FPGA из модели. SoC Builder сохраняет созданные двоичные файлы в папке, а затем можно продолжить выполнение.

Построить и загрузить для внешнего режима - выберите этот параметр, чтобы построить проект и запустить его во внешнем режиме. Внешний режим позволяет настраивать параметры на FPGA без необходимости перестраивать конструкцию FPGA. Он также позволяет регистрировать данные из FPGA и отображать их на хосте. Дополнительные сведения о внешнем режиме см. в разделе Моделирование внешнего режима для настройки параметров и мониторинга сигналов (Simulink Coder).

Проверьте модель на выбранной плате и создайте отчет. Проверьте отчет, чтобы убедиться, что проект создан так, как ожидалось.

SoC Builder называет отчет <project-folder>/html/ и сохраняет его в папке проекта. Отчет содержит обзорный раздел с информацией о модели, папке проекта и созданных файлах. Отчет также содержит список IP-ядер пользователей и IP-ядер, предоставленных поставщиком, с картой адресов регистров и блоков памяти.modelname_system_report.html

Чтобы создать битовый поток для проекта FPGA и скомпилированный исполняемый файл для программного обеспечения, нажмите кнопку «» Создать «».

При нажатии кнопки Построить (Build) открывается внешняя оболочка и запускаются сторонние инструменты для синтеза и реализации конструкции. Время генерации зависит от сложности модели и главного компьютера. После завершения генерации битовый поток генерируется с именем модели. SoC Builder создает сценарий тестирования JTAG, если в параметрах конфигурации выбрана опция Включить MATLAB как AXI Master (Include MATLAB as AXI Master). Сценарий показывает, как настроить MATLAB как мастер AXI и настроить дизайн FPGA через JTAG. Сценарий можно настроить для создания собственного стенда тестирования. Дополнительные сведения о MATLAB как AXI Master см. в документации по пакету поддержки: SoC Blockset Supported Hardware.

Если tee.exe не установлен на компьютере с ОС Windows. При работе с системными платами Intel может возникнуть ошибка сборки во внешней оболочке. Чтобы устранить ошибку, выполните следующие действия.

Загрузить tee.exe файл для Windows по этой ссылке https://ss64.net/westlake/nt/tee.zip.

Распакуйте и скопируйте EXE-файл в C:\Windows папка.

Добавьте путь к папке на панели Системные переменные в качестве переменных среды Windows.

Щелкните правой кнопкой мыши значок «Компьютер» и выберите «Свойства», либо в панели управления Windows выберите «Система».

Выберите Дополнительные системные параметры.

На вкладке Дополнительно (Advanced) щелкните Переменные среды (Environment Variables).

На панели Системные переменные (System variables) выберите переменную Путь (Path) и нажмите кнопку Изменить (Edit).

На панели Править переменную среды нажмите кнопку Создать, чтобы добавить новый путь к папке.

Запустите инструмент SoC Builder.

Проверьте адрес IPv4, номер порта SSH и учетные данные для входа в систему. При необходимости отредактируйте любое из этих значений. Этот шаг имеет решающее значение при наличии нескольких плат, подключенных к хост-компьютеру, чтобы SoC Builder мог определить правильное подключение к порту. Убедитесь, что отображаемый IP-адрес соответствует IP-адресу платы, которую требуется использовать.

Убедитесь, что плата подключена к хосту с помощью кабеля Ethernet, а затем нажмите Test Connection для проверки физического соединения с платой.

Примечание

Этот шаг в SoC Builder виден только в том случае, если модель верхнего уровня включает модель процессора.

Примечание

Если в топовую модель включена модель FPGA, но модель процессора отсутствует, кнопка отображается как Load.

Убедитесь, что плата подключена к хост-компьютеру.

Если в топовой модели присутствует модель процессора, подключите к плате кабель Ethernet.

Если в топовую модель входит модель FPGA, но модель процессора отсутствует, подключите к плате кабель JTAG.

Щелкните Загрузить (Load) и Выполнить (Run). Это действие загружает сгенерированный поток битов в FPGA, программирует процессор и запускает приложение.

Если на шаге 5 выбрано Настроить параметры и контролировать сигналы во внешнем режиме, это действие загружает поток битов в FPGA и открывает модель во внешнем режиме. Теперь можно выбирать сигналы для регистрации и мониторинга или изменять настраиваемые параметры. На вкладке System on Chip в разделе Run on Hardware можно нажать Monitor and Tune для запуска инструментального приложения на оборудовании. Нажмите кнопку «Подключить», если ранее был построен и загружен проект в FPGA. Это действие соединяет инструментальную модель Simulink с моделью FPGA.