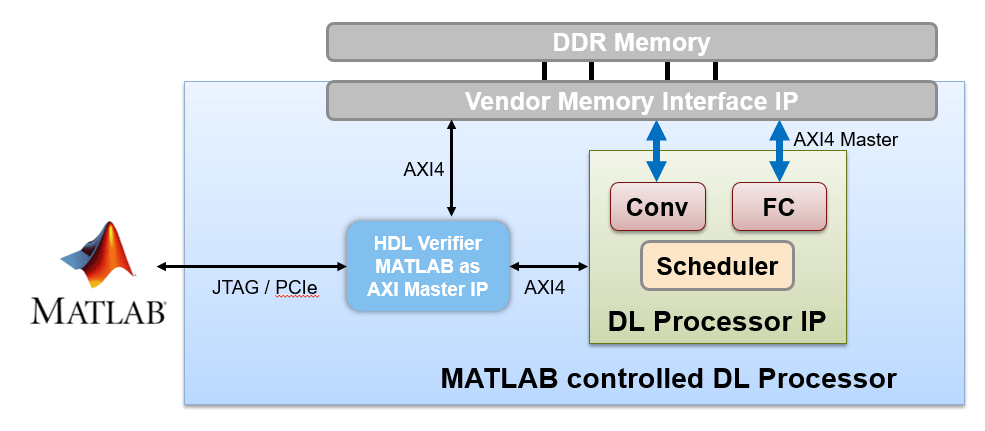

Для быстрого прототипирования нейронных сетей для глубокого обучения на FPGA от MATLAB®, используйте MATLAB управляемый процессор глубокого обучения. Процессор интегрирует типовой процессор глубокого обучения с HDL Verifier™ MATLAB в качестве AXI Master IP. Для получения дополнительной информации о:

Общий IP-адрес процессора глубокого обучения, см. «Приложения процессора глубокого обучения».

MATLAB в качестве AXI Master IP, см. «Настройка для MATLAB AXI Master (HDL Verifier)».

Можно использовать этот процессор для запуска нейронных сетей с различными входами, весами и смещениями на одной платформе FPGA, потому что IP-ядро процессора глубокого обучения может обрабатывать тензоры и формы любых размеров. Прежде чем использовать MATLAB в качестве AXI Master, убедитесь, что для плат FPGA установлены пакеты поддержки HDL Verifier. Этот рисунок показывает управляемую MATLAB архитектуру процессора глубокого обучения.

Для интеграции типового процессора глубокого обучения IP с MATLAB в качестве AXI Master используйте интерфейс AXI4 Slave IP-ядра процессора глубокого обучения. При помощи JTAG или экспресс-интерфейса PCI IP отвечает на чтение или запись команд от MATLAB. Поэтому можно использовать управляемый MATLAB процессор глубокого обучения, чтобы перенести глубокую нейронную сеть на платы FPGA от MATLAB, выполнить операции, заданные сетевой архитектурой, а затем вернуть предсказанные результаты в MATLAB. Следующий пример иллюстрирует развертывание предварительно обученной сети серии AlexNet в Intel® Arria® 10 Комплект для разработки SoC.