Определенные шаблоны или комбинация блоков с регистрами могут улучшить достижимую тактовую частоту и уменьшить использование площади на платах FPGA. Адаптивная оптимизация конвейеризации создает эти шаблоны путем вставки регистров трубопроводов в блоки в проекте. Чтобы определить оптимальное количество регистров конвейера для вставки в ваш проект, оптимизация рассматривает целевое устройство, целевую частоту, размеры слова умножителей и настройки в HDL Block Properties. Используйте адаптивную конвейеризацию с:

Конвейеризация с тактовой частотой для вставки регистров конвейера с более высокой тактовой частотой вместо более медленной скорости передачи данных. С помощью конвейеризации с тактовой частотой можно проектировать DUT с одной скоростью, а затем задавать Oversampling factor.

Совместное использование ресурсов, которое сохраняет область и время, потому что генератор кода делится ресурсами и вставляет адаптивные регистры конвейера.

По умолчанию адаптивная оптимизация конвейеризации отключена в модели. В определенных ситуациях перед генерацией HDL-кода необходимо включить эту оптимизацию. Смотрите Проект Шаблонов, которые требуют адаптивной Конвейеризации.

Для HDL Coder™ вставки адаптивных трубопроводов укажите целевое устройство. Когда ваш проект имеет умножители, задайте целевое устройство и целевую частоту.

Примечание

Если вы используете целевое устройство, которое не характеризуется для адаптивной конвейеризации, оптимизация использует Xilinx® Virtex®-7 при Xilinx Vivado задается как Synthesis Tool и использует Intel® Stratix® V, когда Synthesis Tool Altera Quartus II или Intel Quartus Pro.

Убедитесь, что для подсистемы, для которой вы хотите HDL Coder вставить адаптивные трубопроводы, включена балансировка задержки. Если вы отключаете балансировку задержки, генератор кода не вставляет адаптивные трубопроводы.

Убедитесь, что в проекте нет типов данных с плавающей точкой или операций.

Примечание

В некоторых случаях, когда у вас есть блоки в цикле обратной связи, адаптивная конвейеризация не может вставить необходимое количество регистров трубопровода в выход. В таком случае балансировка задержки может завершиться неуспешно.

Можно задать адаптивную конвейеризацию для всей модели или, для более мелкого управления, можно задать адаптивную конвейеризацию для подсистем в подсистеме DUT верхнего уровня.

По умолчанию адаптивная конвейеризация отключена на уровне модели. Адаптивную конвейеризацию можно включить одним из следующих способов:

В HDL Workflow Advisor, на вкладке <reservedrangesplaceholder4>> <reservedrangesplaceholder3>> <reservedrangesplaceholder2>> <reservedrangesplaceholder1>, избранном Adaptive pipelining.

В диалоговом окне Configuration Parameters на вкладке HDL Code Generation > Optimization > Pipelining выберите Adaptive pipelining и нажмите OK.

В командной строке используйте makehdl или hdlset_param функция для установки Adaptive pipelining равной on.

hdlset_param(gcs, 'AdaptivePipelining', 'on')

По умолчанию подсистемы в модели наследуют настройку адаптивной конвейеризации на уровне модели. Если вы хотите, чтобы HDL Coder выборочно включил адаптивные конвейеры для подсистемы в вашей модели, задайте AdaptivePipelining on для этой подсистемы.

Чтобы узнать, как задать адаптивную конвейеризацию для подсистемы, смотрите «Задать адаптивную конвейеризацию для подсистемы».

Адаптивная конвейеризация поддерживает эти интерполяционные таблицы, умножители, блоки умножения накопления и перехода скорости для автоматической вставки трубопровода.

n-D Lookup Table

Direct Lookup Table (n-D)

Sine HDL Optimized

Cosine HDL Optimized

Downsample

Rate Transition

Product

Gain

Multiply-Add

Multiply-Accumulate

MATLAB Function

Для вставки адаптивных трубопроводов для блоков Rate Transition и Downsample:

Укажите целевое устройство.

Убедитесь, что Downsample блоки имеют Downsample factor больше двух.

При генерации кода HDL Coder вставляет регистр конвейера в выходной порт блока Downsample. Сложение регистра трубопровода может избежать логики регистра обхода, которая сохраняет площадь на целевом ПЛИС.

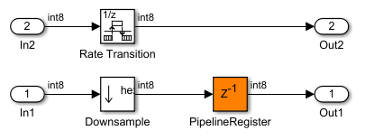

Этот рисунок является сгенерированной моделью для блоков с Xilinx Virtex7 в качестве целевого устройства FPGA.

Чтобы вставить адаптивные трубопроводы для этих блоков:

Укажите целевое устройство.

Задайте целевую частоту, большую нуля.

При генерации кода HDL Coder вставляет регистры во входной и выходной порты блоков. Комбинация умножителей с регистрами может потенциально сопоставляться с модулями DSP на целевом устройстве.

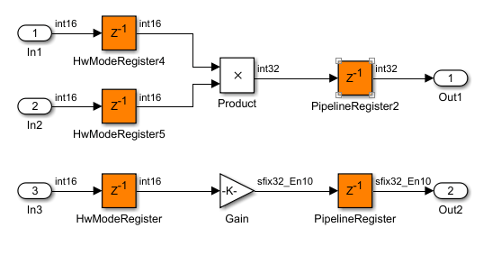

Этот рисунок является сгенерированной моделью для блоков Product, Gain и Multiply-Add с Intel Arria10 в качестве целевого устройства FPGA и целевой частотой 500 МГц. Входы блоков имеют тип int16.

Шаблон и количество регистров конвейера, которые вставляет HDL Coder, могут варьироваться в зависимости от целевого устройства, целевой частоты и размеров слова умножителя.

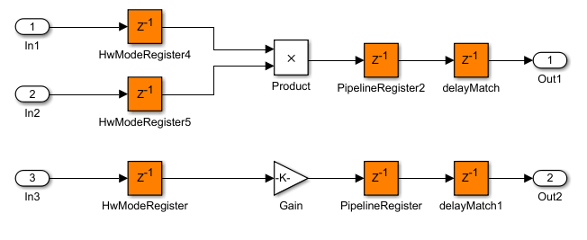

Этот рисунок является сгенерированной моделью для блоков с Xilinx Virtex7 в качестве целевого устройства FPGA и целевой частотой 1500 МГц. Входы имеют тип int8.

Блоки имеют разное количество регистров конвейера в портах выхода. Чтобы соответствовать задержкам, HDL Coder добавляет задержку на выходе блоков Product и Gain.

Чтобы вставить адаптивные трубопроводы для этих блоков:

Укажите целевое устройство.

Задайте целевую частоту, большую нуля.

Используйте Parallel Архитектура HDL для блока Multiply-Accumulate. Вектор входа размера N, эта архитектура использует N

Multiply-Add блоки последовательно, чтобы вычислить результат.

Внимание

Блок Multiply-Add с PipelineDepth в auto или значение, больше нуля, и блок Multiply-Accumulate с HDL- архитектуры задается как Parallel игнорируйте настройку адаптивной конвейеризации. Если вы задаете целевое устройство FPGA и целевую частоту, большую нуля, генератор кода вставляет конвейерные регистры на входах и выходах блока, даже когда адаптивная конвейеризация отключена.

При генерации кода HDL Coder вставляет регистры во входной и выходной порты блоков. Комбинация блоков с регистрами может потенциально сопоставляться с модулями DSP на целевом устройстве.

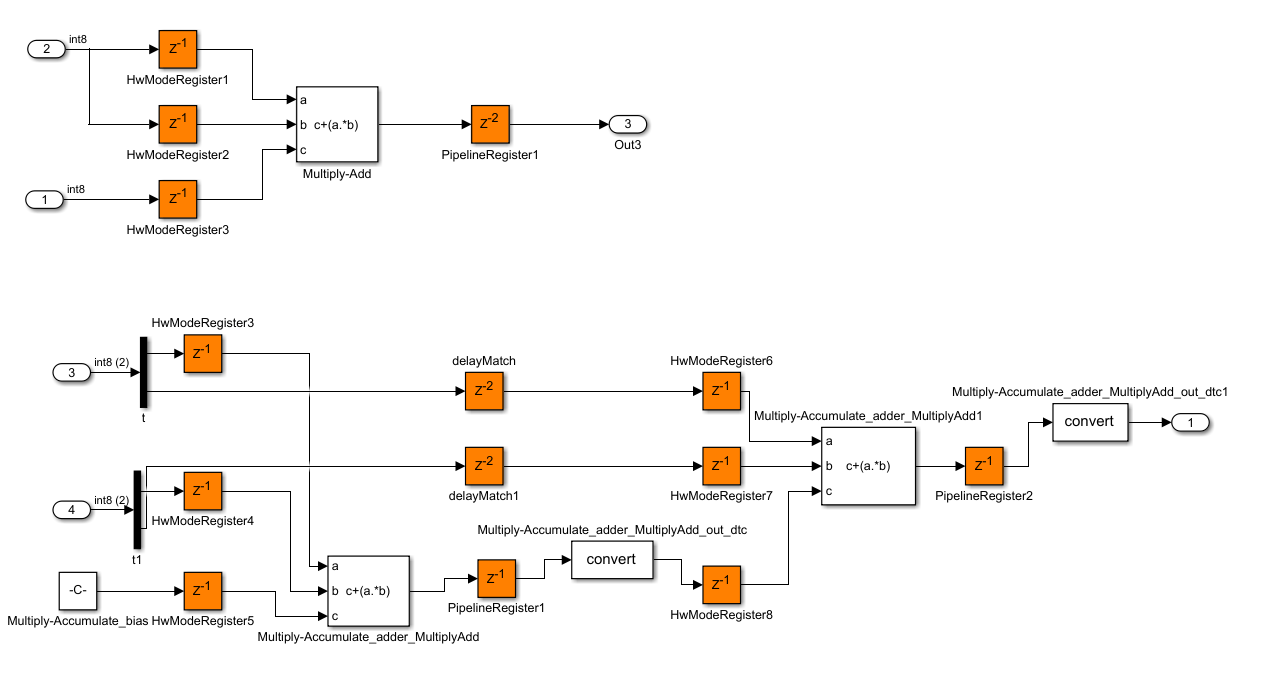

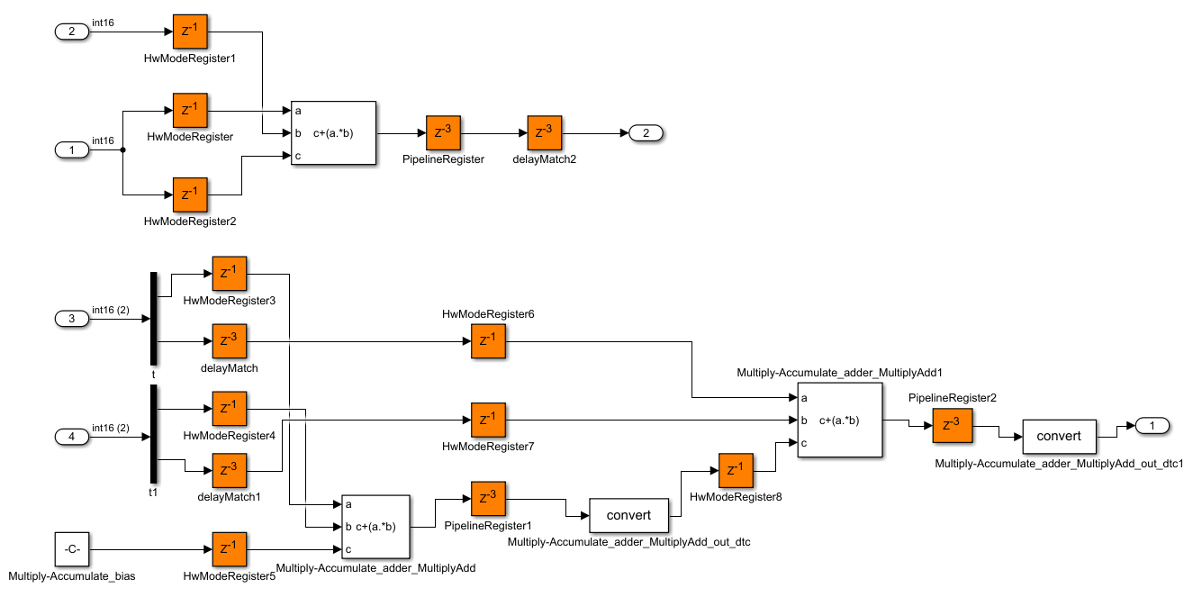

Этот рисунок является сгенерированной моделью для Multiply-Add и Multiply-Accumulate с Intel Arria10 в качестве целевого устройства FPGA и целевой частотой 500 МГц. Входы блоков имеют тип int8.

Шаблон и количество регистров конвейера, которые вставляет HDL Coder, могут варьироваться в зависимости от целевого устройства, целевой частоты и размеров слова умножителя.

Этот рисунок является сгенерированной моделью для блоков с Xilinx Virtex7 в качестве целевого устройства FPGA и целевой частотой 1500 МГц. Входы имеют тип int16.

Для вставки адаптивных трубопроводов для блоков MATLAB Function:

Укажите целевое устройство.

Задайте целевую частоту, большую нуля.

Установите архитектуру HDL для блоков MATLAB Function равной MATLAB Datapath.

HDL Coder обрабатывает блоки MATLAB Function с установленной архитектурой MATLAB Datapath как регулярные Подсистемы. Генератор кода преобразует MATLAB® алгоритм для Simulink® блок. Если в схеме Simulink используются блоки, поддерживаемые адаптивной конвейеризацией, такие как Product или Add. генератор кода вставляет конвейерные регистры во входной и выходной порты блоков. Комбинация умножителей с регистрами может потенциально сопоставляться с модулями DSP на целевом устройстве.

Рассмотрим блок MATLAB Function, который использует MATLAB Datapath архитектура. Этот код является алгоритмом внутри блока MATLAB Function.

function y = fcn(u)

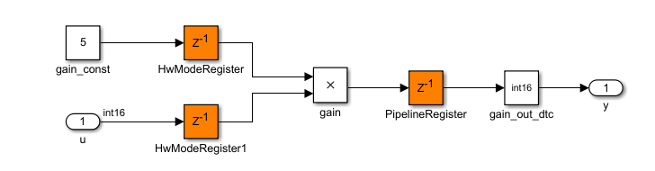

y = u*5;Этот рисунок является сгенерированной моделью для блока MATLAB Function с Intel Arria10 в качестве целевого устройства FPGA и целевой частотой 500 МГц. Входы блоков имеют тип int16. Генератор кода вывел алгоритм как умножение на постоянные и вставленные адаптивные конвейеры на входе и выходе.

Для блока MATLAB function см. раздел «Приложения HDL».

Чтобы просмотреть информацию об адаптивной конвейеризации в отчете, перед генерацией кода для каждой Подсистемы или модели-ссылки включите отчет Генерация кода. Чтобы включить отчет Генерация кода, в диалоговом окне Параметры конфигурации, на панели HDL Code Generation, выберите Generate optimization report.

При генерации кода HDL Coder создает отчет Code Generation. Выберите Adaptive Pipelining раздел отчета Оптимизации.

Отчет Адаптивный трубопровод (Adaptive Pipelining) отображает статус адаптивной оптимизации конвейеризации и вставил ли HDL Coder адаптивные трубопроводы в проект.

Если адаптивная конвейеризация успешна, в отчете отображаются блоки, для которых HDL Coder вставил регистры конвейера, количество вставленных регистров конвейера и любые дополнительные примечания. Щелкните ссылку на блок, чтобы увидеть регистры трубопроводов, вставленные в блоки в проекте.

Если адаптивная конвейеризация не выполняется, в отчете отображаются критерии, которые приводят к ошибке адаптивной конвейеризации.