Программное обеспечение HDL Coder™ предоставляет опции архитектуры, которые расширяют ваш контроль над скоростью и областями компромиссов в реализации созданий фильтра. Чтобы достичь желаемого компромисса для сгенерированного HDL-кода, можно либо указать полностью параллельную архитектуру, либо выбрать одну из нескольких последовательных архитектур. Сконфигурируйте последовательную архитектуру с помощью параметров SerialPartition и ReuseAccum. Можно также выбрать фильтр на основе фрейма для увеличения пропускной способности.

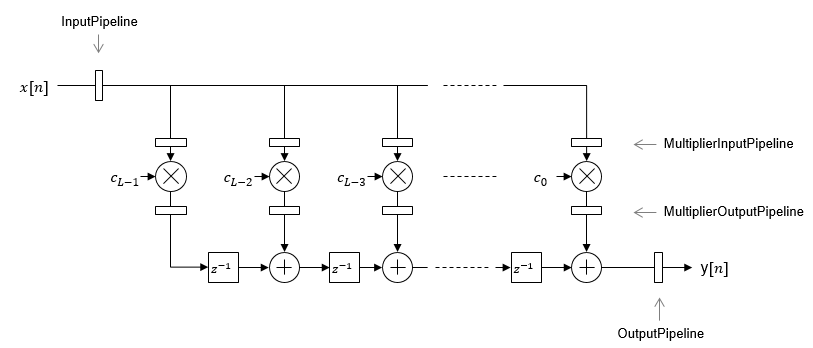

Используйте конвейеризацию параметры, чтобы улучшить эффективность скорости ваших созданий фильтра. Добавьте трубопроводы к логике сумматора вашего фильтра с помощью AddPipelineRegisters для скалярных входных фильтров и AdderTreePipeline для основанных на кадрах фильтров. Задайте этапы трубопровода до и после каждого умножения с помощью MultiplierInputPipeline и MultiplierOutputPipeline. Установите количество ступеней трубопровода до и после фильтра с помощью InputPipeline и OutputPipeline. На схемах архитектуры показаны местоположения различных конфигурируемых этапов трубопровода.

Эта опция является архитектурой по умолчанию. Полностью параллельная архитектура использует выделенный множитель и сумматор для каждого отвода фильтра. Ответвления выполняются параллельно. Полностью параллельная архитектура оптимальна для скорости. Однако он требует больше умножителей и сумматоров, чем последовательная архитектура, и поэтому потребляет больше площади чипа. На схемах показаны архитектуры для прямой формы и для транспонированных структур фильтра с полностью параллельными реализациями и расположение конфигурируемых этапов трубопровода.

По умолчанию блок реализует линейную логику сумматора. Когда вы включаете AddPipelineRegisters, логика сумматора реализована как конвейерное дерево сумматора. В дереве сумматоров используются типы данных с полной точностью. Если вы генерируете модель валидации, необходимо использовать полную точность в исходной модели, чтобы избежать несоответствий валидации.

The AddPipelineRegisters параметр не влияет на реализацию транспонированного фильтра.

Последовательные архитектуры повторно используют аппаратные ресурсы во времени, экономя область чипа. Сконфигурируйте последовательную архитектуру с помощью параметров SerialPartition и ReuseAccum. Доступные опции последовательной архитектуры являются последовательными, частично последовательными и каскадными.

Полностью последовательная архитектура сохраняет область путем повторного использования ресурсов умножения и суммирования последовательно. Для примера в создание фильтра с четырьмя отводами используется один умножитель и сумматор, выполняющий операцию умножения-накопления один раз для каждого отвода. Раздел умножения-накопления проекта запускается с четырехкратной частотой входной/выходной выборки фильтра. Это проект экономит площадь за счет некоторых потерь скорости и более высокого потребления степени.

В полностью последовательной архитектуре системных часов запусков с гораздо большей частотой, чем частота дискретизации фильтра. Таким образом, для заданного создания фильтра максимальная скорость, достижимая с помощью полностью последовательной архитектуры, меньше, чем у параллельной архитектуры.

Частично последовательная архитектура охватывает всюсь область значений компромиссов скорости и площади, которые находятся между полностью параллельной и полностью последовательной архитектурами.

В частичной последовательной архитектуре ответвления фильтра сгруппированы в ряд последовательных разделов. Ответвления внутри каждого раздела выполняются последовательно, но разделы выполняются параллельно друг другу. Выходные выходы секций суммируются на конечном выходе.

Когда вы выбираете частично последовательную архитектуру, вы задаете количество разделов и длину (количество отводов) каждого раздела. Предположим, что вы задаете фильтр с четырьмя касаниями с двумя разделами, каждый из которых имеет два отвода. Системные часы запускаются с удвоенной частотой дискретизации фильтра.

Каскадно-последовательная архитектура тесно напоминает частично последовательную архитектуру. Как и в частичной последовательной архитектуре, отводы фильтра сгруппированы в ряд последовательных разделов, которые выполняются параллельно друг другу. Однако накопленный выход каждой перегородки каскадируется к аккумулятору предыдущей перегородки. Поэтому выход всех перегородок вычисляется в аккумуляторе первого разбиения. Этот метод называется повторным использованием аккумулятора. Конечный сумматор не требуется, что сохраняет область.

Для каскадно-последовательной архитектуры требуется дополнительный цикл системных часов, чтобы завершить окончательное суммирование к выходу. Поэтому частота системных часов должна быть несколько увеличена по сравнению с тактовой частотой, используемой в некаскадной частично последовательной архитектуре.

Чтобы сгенерировать каскадно-последовательную архитектуру, задайте частично последовательную архитектуру с включенным повторным использованием аккумулятора. Если вы не задаете последовательные разделы, HDL Coder автоматически выбирает оптимальное разбиение.

Сериализация фильтра увеличивает общую задержку проекта на один такт. Последовательные архитектуры используют аккумулятор (сумматор с регистром), чтобы добавить продукты последовательно. Дополнительный конечный регистр используется для хранения суммированного результата всех последовательных разделов, требуя дополнительного тактового цикла для операции. Чтобы смоделировать эту задержку, HDL Coder вставляет блок Delay в сгенерированную модель после фильтрующего блока.

При выборе последовательной архитектуры генератор кода использует полную точность в HDL-коде. Поэтому HDL Coder повышает полную точность в сгенерированной модели. Если вы генерируете модель валидации, необходимо использовать полную точность в исходной модели, чтобы избежать несоответствий валидации.

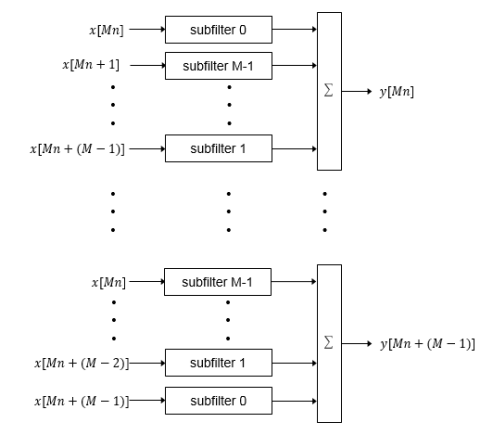

Когда вы выбираете архитектуру на основе фреймов и обеспечиваете входной кадр M-sample, кодер реализует полностью параллельную архитектуру фильтра. Фильтр включает M параллельных подфильтров для каждой входной выборки .

Каждый из подфильтров включает в себя каждый M-й коэффициент. Результаты подфильтра складываются так, что каждая выходная выборка является суммой каждого из коэффициентов, умноженных на одну входную выборку.

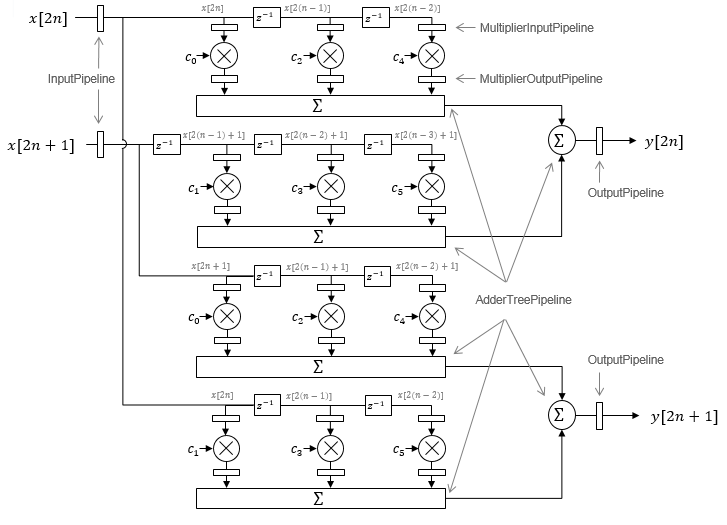

Схема показывает архитектуру фильтра для формата кадра из двух выборок (M = 2) и длину фильтра из шести коэффициентов. Вход является вектором с двумя значениями, представляющими выборки во времени. Входные выборки, x[2n] и x[2n+1], представляют n-ю входную пару. Каждая вторая выборка из каждого потока подаётся на два параллельных подфильтра. Результаты четырех подфильтров складываются вместе, чтобы создать две выходные выборки. Таким образом, каждый выход выборка является суммой каждого из коэффициентов, умноженных на одну из входа выборок.

Суммы реализованы как конвейерное дерево сумматоров. Установите AdderTreePipeline, чтобы задать количество ступеней трубопровода между уровнями дерева сумматоров. Чтобы улучшить тактовую частоту, рекомендуется задать этот параметр равным 2. Чтобы подогнать умножители в блоки DSP на вашем FPGA, добавьте этапы трубопровода до и после умножителей с помощью MultiplierInposePipeline и MultiplierOutputPipeline.

Для симметричных или антисимметричных коэффициентов архитектура фильтра повторно использует умножители коэффициентов и добавляет проектную задержку между этапами умножения и суммирования по мере необходимости.