Stateflow® временные логические операторы (такие как after, before, или every) являются логическими операторами, которые работают с счетчиками повторений событий Stateflow. Временные логические операторы могут появляться только в условиях на переходах, которые происходят из состояний, и в состояниях активности. Хотя временная логика не вводит новые события в модель Stateflow, полезно думать об изменении значения временного логического условия как о событии. Можно использовать временные логические операторы во многих случаях, когда требуется счетчик. Распространенным вариантом использования было бы использование временной логики для реализации счетчика тайм-аута.

Для получения дополнительной информации смотрите Управление выполнением диаграммы с использованием временной логики (Stateflow).

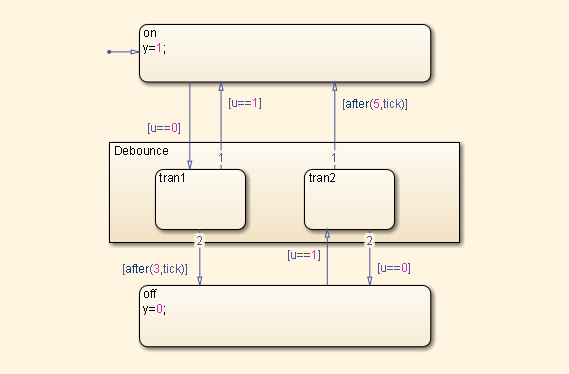

В графике, показанной на следующем рисунке, используется временная логика в проекте для debouncer. Вместо мгновенного переключения между состояниями включения и выключения, график использует два промежуточных состояния и временную логику, чтобы игнорировать переходные процессы. Переход фиксируется на основе тайм-аута.

По умолчанию состояния в Chart Stateflow упорядочены по алфавиту. Упорядоченное расположение состояний в HDL-коде может изменяться, если в HDL-коде включена генерация выходного порта активного состояния. Чтобы включить эту настройку, откройте свойства Chart и установите флажок Create output port for monitoring. Смотрите также Упрощение диаграмм Stateflow путем включения активных Выходов состояния (Stateflow).

Когда вы генерируете VHDL® код, недавно добавленное состояние выбирается как OTHERS состояние в HDL-коде. В следующем фрагменте кода показан VHDL-код, сгенерированный этим Chart.

Chart_1_output : PROCESS (is_Chart, u, temporalCounter_i1, y_reg)

VARIABLE temporalCounter_i1_temp : unsigned(7 DOWNTO 0);

BEGIN

temporalCounter_i1_temp := temporalCounter_i1;

is_Chart_next <= is_Chart;

y_reg_next <= y_reg;

IF temporalCounter_i1 < 7 THEN

temporalCounter_i1_temp := temporalCounter_i1 + 1;

END IF;

CASE is_Chart IS

WHEN IN_tran1 =>

IF u = 1.0 THEN

is_Chart_next <= IN_on;

y_reg_next <= 1.0;

ELSIF temporalCounter_i1_temp >= 3 THEN

is_Chart_next <= IN_off;

y_reg_next <= 0.0;

END IF;

WHEN IN_tran2 =>

IF temporalCounter_i1_temp >= 5 THEN

is_Chart_next <= IN_on;

y_reg_next <= 1.0;

ELSIF u = 0.0 THEN

is_Chart_next <= IN_off;

y_reg_next <= 0.0;

END IF;

WHEN IN_off =>

IF u = 1.0 THEN

is_Chart_next <= IN_tran2;

temporalCounter_i1_temp := to_unsigned(0, 8);

END IF;

WHEN OTHERS =>

IF u = 0.0 THEN

is_Chart_next <= IN_tran1;

temporalCounter_i1_temp := to_unsigned(0, 8);

END IF;

END CASE;

temporalCounter_i1_next <= temporalCounter_i1_temp;

END PROCESS Chart_1_output;Графическая функция является функцией, заданной графически блок-схемой. Графические функции находятся на графике вместе со схемами, которые их вызывают. Как MATLAB® функции и функции C, графические функции могут принимать аргументы и возвращать результаты. Графические функции могут вызываться в переходном и состоянии.

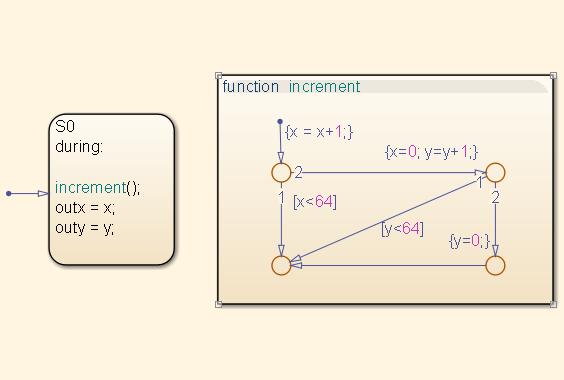

Следующий рисунок показывает графическую функцию, которая реализует счетчик 64 на 64.

В следующем фрагменте кода показан VHDL-код, сгенерированный для этой графической функции.

x64_counter_sf : PROCESS (x, y, outx_reg, outy_reg)

-- local variables

VARIABLE x_temp : unsigned(7 DOWNTO 0);

VARIABLE y_temp : unsigned(7 DOWNTO 0);

BEGIN

outx_reg_next <= outx_reg;

outy_reg_next <= outy_reg;

x_temp := x;

y_temp := y;

x_temp := tmw_to_unsigned(tmw_to_unsigned(tmw_to_unsigned(x_temp, 9), 10)

+ tmw_to_unsigned(to_unsigned(1, 9), 10), 8);

IF x_temp < to_unsigned(64, 8) THEN

NULL;

ELSE

x_temp := to_unsigned(0, 8);

y_temp := tmw_to_unsigned(tmw_to_unsigned(tmw_to_unsigned(y_temp, 9), 10)

+ tmw_to_unsigned(to_unsigned(1, 9), 10), 8);

IF y_temp < to_unsigned(64, 8) THEN

NULL;

ELSE

y_temp := to_unsigned(0, 8);

END IF;

END IF;

outx_reg_next <= x_temp;

outy_reg_next <= y_temp;

x_next <= x_temp;

y_next <= y_temp;

END PROCESS x64_counter_sf;Диаграммы Stateflow поддерживают как иерархию (состояния, содержащие другие состояния), так и параллелизм (несколько состояний, которые могут быть активны одновременно).

В семантике Stateflow параллелизм не является синонимом параллелизма. Параллельные состояния могут быть активны одновременно, но они выполняются последовательно согласно их порядку выполнения. (Порядок выполнения отображается в правом верхнем углу параллельного состояния).

Для получения подробной информации об иерархии и параллелизме смотрите Иерархию объектов Stateflow (Stateflow) и Порядок выполнения для параллельных состояний (Stateflow).

Для генерации HDL-кода весь график преобразуется в один выходной процесс расчета. В рамках выходного процесса расчета:

Выполнение параллельных состояний протекает последовательно.

Вложенные иерархические состояния сопоставлены с вложенными CASE операторы в сгенерированном HDL-коде.

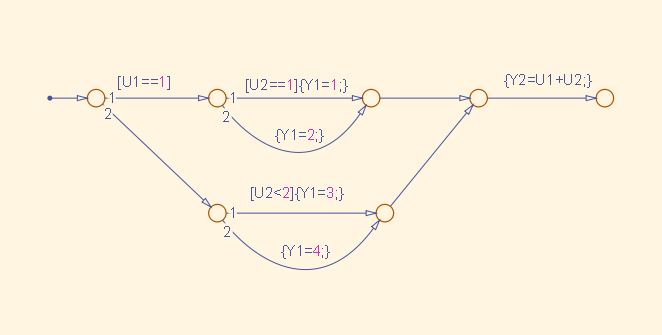

Графики, состоящие из чистых блок-схем (то есть графиков без состояний), полезны при захвате if-then-else конструкции, используемые в процедурных языках, таких как C.

В качестве примера рассмотрим следующую логику, выраженную в C-подобном псевдокоде.

if(U1==1) {

if(U2==1) {

Y = 1;

}else{

Y = 2;

}

}else{

if(U2<2) {

Y = 3;

}else{

Y = 4;

}

}

Следующий рисунок показывает блок-схему, которая реализует if-then-else логика.

Следующий сгенерированный фрагмент кода VHDL показывает вложенные операторы IF-ELSE, полученные из блок-схемы.

Chart : PROCESS (Y1_reg, Y2_reg, U1, U2)

-- local variables

BEGIN

Y1_reg_next <= Y1_reg;

Y2_reg_next <= Y2_reg;

IF unsigned(U1) = to_unsigned(1, 8) THEN

IF unsigned(U2) = to_unsigned(1, 8) THEN

Y1_reg_next <= to_unsigned(1, 8);

ELSE

Y1_reg_next <= to_unsigned(2, 8);

END IF;

ELSIF unsigned(U2) < to_unsigned(2, 8) THEN

Y1_reg_next <= to_unsigned(3, 8);

ELSE

Y1_reg_next <= to_unsigned(4, 8);

END IF;

Y2_reg_next <= tmw_to_unsigned(tmw_to_unsigned(tmw_to_unsigned(unsigned(U1), 9),10)

+ tmw_to_unsigned(tmw_to_unsigned(unsigned(U2), 9), 10), 8);

END PROCESS Chart;HDL Coder™ поддерживает генерацию HDL-кода для:

Таблица истинности функционирует в рамках диаграммы Stateflow

Truth Table (Stateflow) блоки в Simulink® модели

В этом разделе рассматривается функция Таблицы истинности на графике и VHDL- кода, сгенерированный для диаграммы.

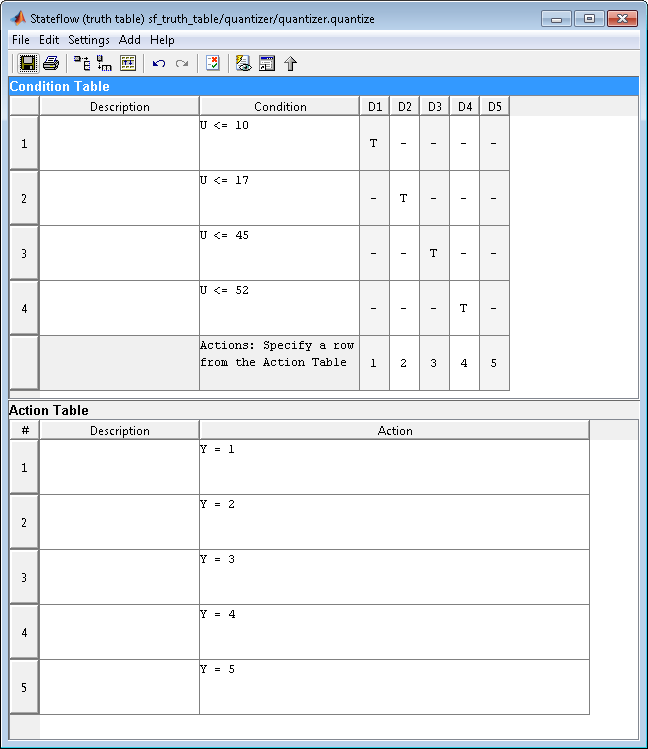

Таблицы истинности хорошо подходят для реализации компактной комбинаторной логики. Типичным приложением для таблиц истинности является реализация нелинейного квантования или пороговой логики. Примите во внимание следующую логику:

Y = 1 when 0 <= U <= 10 Y = 2 when 10 < U <= 17 Y = 3 when 17 < U <= 45 Y = 4 when 45 < U <= 52 Y = 5 when 52 < U

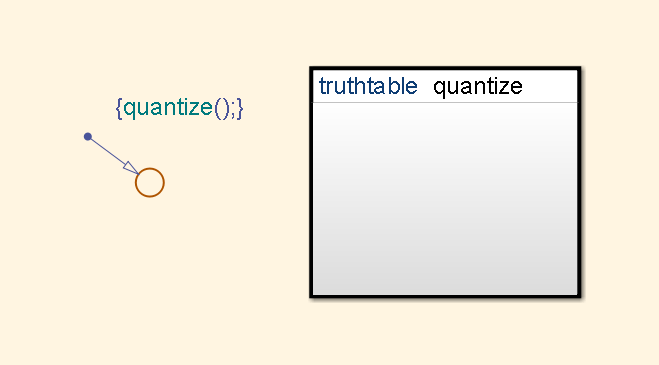

График без статуса с одним вызовом функции Truth Table может представлять эту логику кратко.

Следующий рисунок показывает quantizer график, содержащая Truth Table.

Следующий рисунок показывает пороговую логику, отображаемую в редакторе таблиц истинности.

В следующем фрагменте кода показан VHDL-код, сгенерированный для quantizer график.

quantizer : PROCESS (Y_reg, U)

-- local variables

VARIABLE aVarTruthTableCondition_1 : std_logic;

VARIABLE aVarTruthTableCondition_2 : std_logic;

VARIABLE aVarTruthTableCondition_3 : std_logic;

VARIABLE aVarTruthTableCondition_4 : std_logic;

BEGIN

Y_reg_next <= Y_reg;

-- Condition #1

aVarTruthTableCondition_1 := tmw_to_stdlogic(unsigned(U) <= to_unsigned(10, 8));

-- Condition #2

aVarTruthTableCondition_2 := tmw_to_stdlogic(unsigned(U) <= to_unsigned(17, 8));

-- Condition #3

aVarTruthTableCondition_3 := tmw_to_stdlogic(unsigned(U) <= to_unsigned(45, 8));

-- Condition #4

aVarTruthTableCondition_4 := tmw_to_stdlogic(unsigned(U) <= to_unsigned(52, 8));

IF tmw_to_boolean(aVarTruthTableCondition_1) THEN

-- D1

-- Action 1

Y_reg_next <= to_unsigned(1, 8);

ELSIF tmw_to_boolean(aVarTruthTableCondition_2) THEN

-- D2

-- Action 2

Y_reg_next <= to_unsigned(2, 8);

ELSIF tmw_to_boolean(aVarTruthTableCondition_3) THEN

-- D3

-- Action 3

Y_reg_next <= to_unsigned(3, 8);

ELSIF tmw_to_boolean(aVarTruthTableCondition_4) THEN

-- D4

-- Action 4

Y_reg_next <= to_unsigned(4, 8);

ELSE

-- Default

-- Action 5

Y_reg_next <= to_unsigned(5, 8);

END IF;

END PROCESS quantizer;Примечание

При генерации кода для блока Truth Table (Stateflow) в модели Simulink HDL Coder записывает отдельный файл сущности/архитектуры для кода Truth Table. Файл имеет имя Truth_Table.vhd (для VHDL) или Truth_Table.v (для Verilog®).

Sequence Viewer (Stateflow) | State Transition Table (Stateflow) | Truth Table (Stateflow)