HDL Workflow Advisor проведёт вас через этапы генерации HDL-кода для Simulink® подсистема и процесс проекта FPGA, такие как:

Проверка модели на совместимость генерации HDL-кода и автоматическое исправление несовместимых настроек.

Генерация HDL-кода, испытательного стенда и скриптов для создания и запуска кода и испытательного стенда.

Генерация косимуляции или испытательных стендов DPI SystemVerilog и покрытия кода (требует HDL Verifier™).

Синтез и анализ времени путем интегрирования с сторонними инструментами синтеза.

Обратная аннотация модели с информацией о критическом пути и другой информацией, полученной во время синтеза.

Полные автоматизированные рабочие процессы для выбранных целевых устройств разработки FPGA, включая симуляцию FPGA в цикле (требует HDL Verifier) и рабочий процесс ввода-вывода Simulink Real-Time™ FPGA.

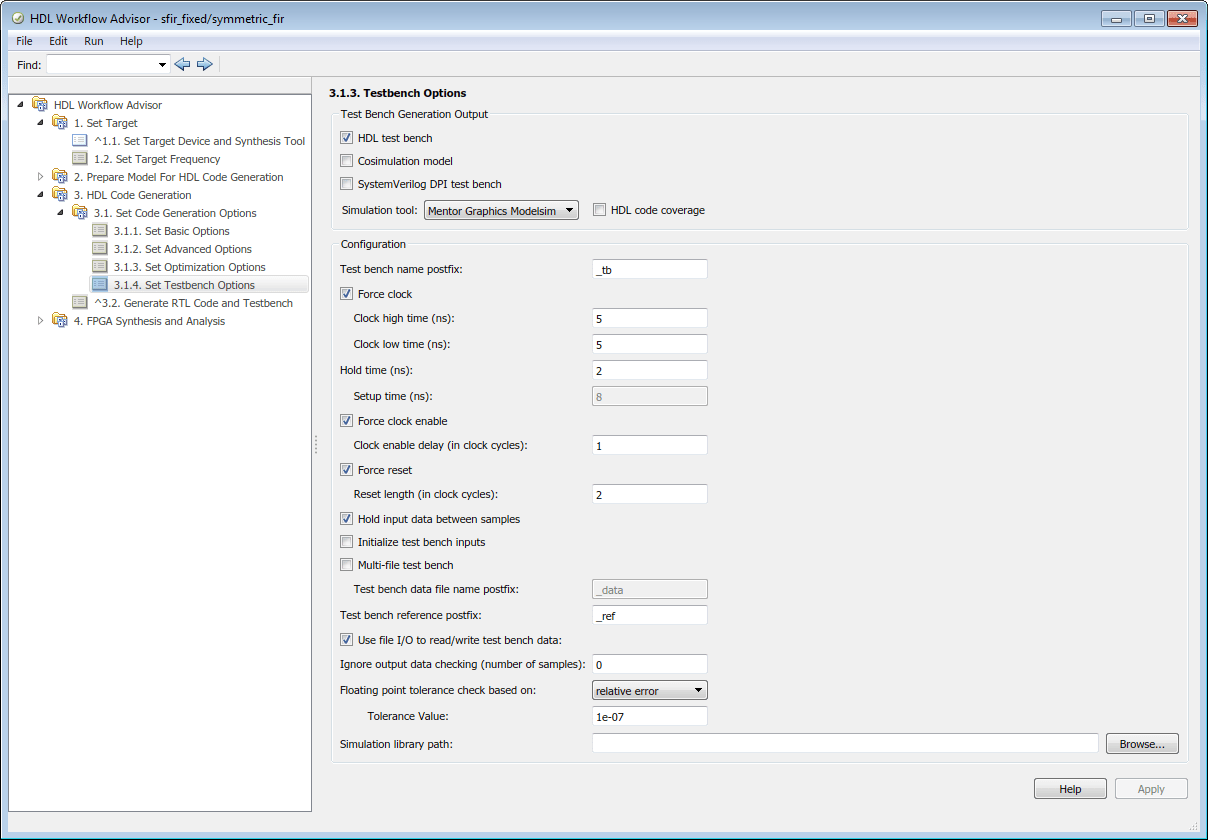

Чтобы выбрать испытательный стенд и опции покрытия кода для генерации HDL-кода из модели Simulink с помощью HDL Workflow Advisor:

Выполните шаги настройки в генерации HDL-кода и синтезе FPGA из модели Simulink.

На шаге 3.1.4 HDL Workflow Advisor, Set Testbench Options, выберите испытательный стенд и опции покрытия кода из Test Bench Generation Output раздела. Кодер генерирует скрипт build-and-run для вашего испытательного стенда и заданного вами Simulation tool. Если вы выбираете несколько испытательный стенд опций, кодер генерирует один испытательный стенд и скрипт для каждого выбранного типа испытательного стенда. Если вы выбираете HDL code coverage, скрипты испытательного стенда включают покрытие кода для вашего сгенерированного HDL-кода. Дополнительные сведения о различных видах испытательных стендов см. в разделе Выбор Испытательном стенде для сгенерированного HDL-кода. Выбрав опции испытательного стенда, нажмите Apply.

На шаге 3.2, Generate RTL Code and Testbench, выберите Generate test bench. Нажмите Apply, а затем нажмите Run This Task. Кодер генерирует HDL-код для вашей подсистемы, а также испытательные стенды и скрипты, выбранные вами на шаге 3.1.3.

Если вы выбрали Cosimulation model, то шаг 3.3, Verify with HDL Cosimulation, появится в HDL Workflow Advisor. Этот шаг автоматически запускает сгенерированную модель косимуляции. Модель сравнивает результат выполнения HDL-кода в вашем Симуляторе HDL с выходом подсистемы Simulink.

Если вы выбрали HDL test bench, кодер генерирует скрипт компиляции, subsystemname_tb_compile, и запуск скрипт, subsystemname_tb_simhdl_prj/hdlsrc/<reservedrangesplaceholder0 >

do symmetric_fir_compile.do do symmetric_fir_tb_compile.do do symmetric_fir_tb_sim.do

Если вы выбрали SystemVerilog DPI test bench, кодер генерирует файл скрипта, subsystemname_dpi_tbhdl_prj/hdlsrc/<reservedrangesplaceholder0 >

do symmetric_fir_dpi_tb.do

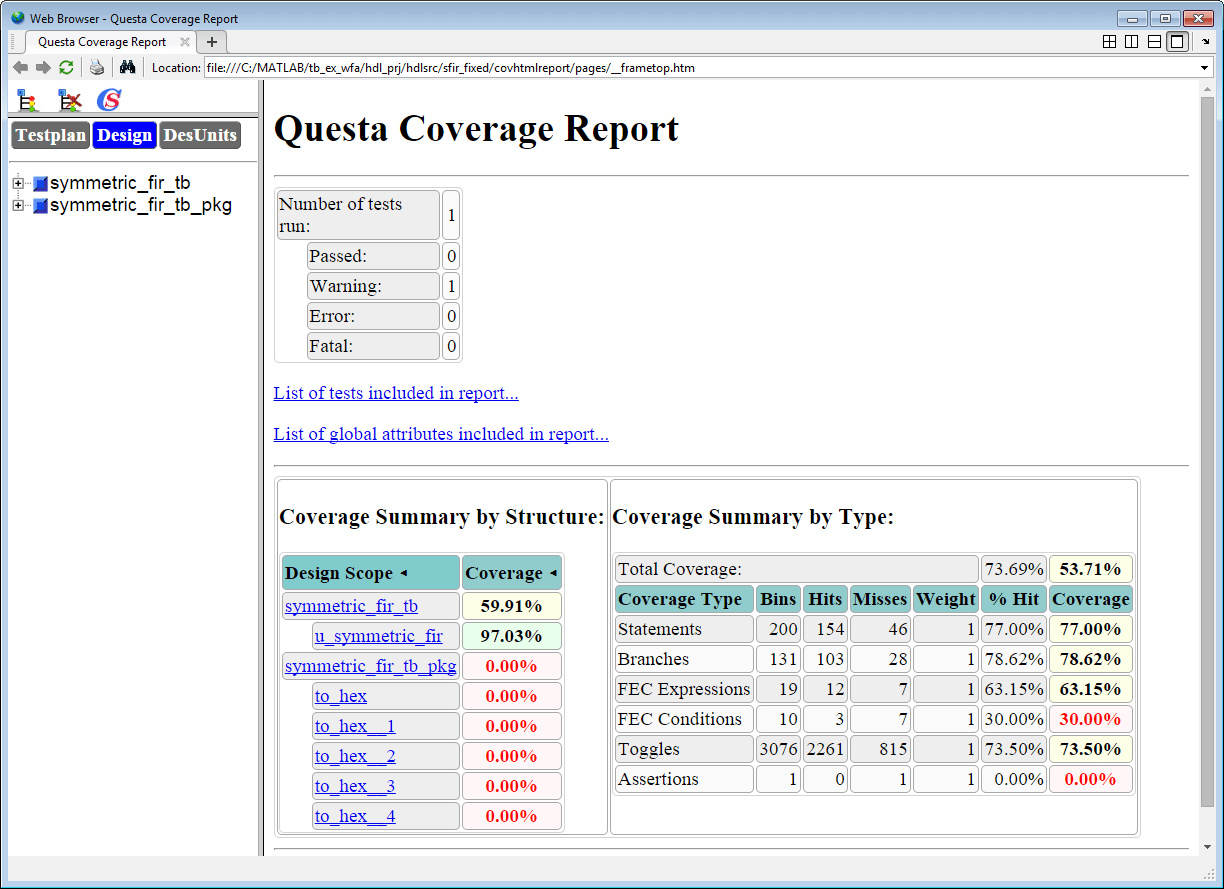

Если вы выбрали HDL code coverage, отчет о покрытии кода от выполнения любого испытательного стенда, включая модель косимуляции, сохранен в hdl_prj\hdlsrc\<reservedrangesplaceholder0 >\ covhtmlreport