Во многих проектах DUT не является автономным. Например, рассмотрим DUT, который является частью большей системы, которая подает сигналы синхронизации на свои компоненты под управлением глобального синхроимпульса. Глобальные часы обычно работают с более высокой частотой, чем некоторые из управляемых ими компонентов. Путем определения такого global oversampling clock можно интегрировать DUT в большую систему, не используя блоки Upsample или Downsample.

Чтобы сгенерировать глобальную логику синхроимпульса, вы задаете oversampling factor. Коэффициент избыточной дискретизации выражает желаемую скорость часов глобальной избыточной дискретизации как произведение базовой скорости вашей модели.

Когда вы задаете коэффициент избыточной дискретизации, HDL Coder™ генерирует часы глобальной избыточной дискретизации и выводит необходимые сигналы синхронизации из синхросигнала. Генерация глобального синхроимпульса избыточной дискретизации влияет только на сгенерированный HDL-код. Часы не влияют на поведение симуляции вашей модели.

Когда вы задаете коэффициент избыточной дискретизации для глобального синхроимпульса избыточной дискретизации, обратите внимание на следующие требования:

Коэффициент избыточной дискретизации должен быть целым числом, большим или равным 1.

Значение по умолчанию является 1. В случае по умолчанию HDL Coder не генерирует часы глобальной избыточной дискретизации.

Некоторые DUT требуют нескольких частот дискретизации для своих внутренних операций. В таких случаях другие ставки в ДУТ должны разделяться равномерно на глобальные коэффициенты сверхчастоты дискретизации. Для получения дополнительной информации см. Раздел «Разрешение конфликтов перебоев сверхчастоты дискретизации».

Коэффициент избыточной дискретизации для глобального синхроимпульса можно задать из графический интерфейс пользователя следующим образом:

Выберите панель HDL Code Generation > Global Settings в диалоговом окне Параметры конфигурации.

Для Oversampling factor в Clock settings разделе введите требуемый коэффициент избыточной дискретизации. На следующем рисунке Oversampling factor задает часы глобальной избыточной дискретизации, которые запускаются с десятикратной базовой скоростью модели.

Щелкните Generate на панели HDL Code Generation, чтобы инициировать генерацию кода.

HDL Coder сообщает тактовую частоту избыточной дискретизации:

### Begin VHDL Code Generation ### MESSAGE: The design requires 10 times faster clock with respect to the base rate = 1. ### Working on symmetric_fir_tc as hdlsrc\symmetric_fir_tc.vhd ### Working on sfir_fixed/symmetric_fir as hdlsrc\symmetric_fir.vhd ### HDL Code Generation Complete.

Можно задать коэффициент передискретизации для глобальных часов из командной строки, установив Oversampling свойство с hdlset_param или makehdl. Следующий пример задает коэффициент избыточной дискретизации 7:

makehdl(gcb,'Oversampling', 7)### Generating HDL for 'sfir_fixed/symmetric_fir' ### Starting HDL Check. ### HDL Check Complete with 0 errors, 0 warnings and 0 messages. ### Begin VHDL Code Generation ### MESSAGE: The design requires 7 times faster clock with respect to the base rate = 1. ### Working on symmetric_fir_tc as hdlsrc\symmetric_fir_tc.vhd ### Working on sfir_fixed/symmetric_fir as hdlsrc\symmetric_fir.vhd ### HDL Code Generation Complete.

Реализация некоторых проектов в HDL по своей сути многократна, хотя оригинальный Simulink® модель является односкоростной. В качестве примера рассмотрим simplevectorsum_cascade модель.

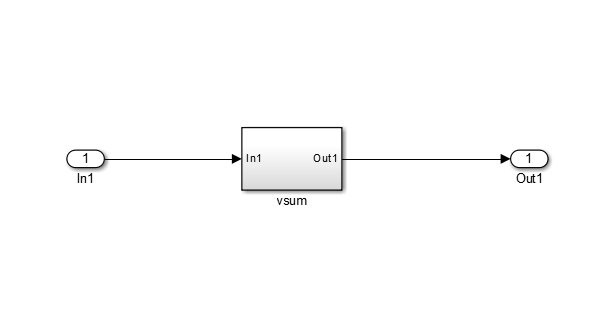

Эта модель состоит из подсистемы, vsum, управляемый входом вектор ширины 10 с выходом скаляра. Следующий рисунок показывает корневой уровень модели.

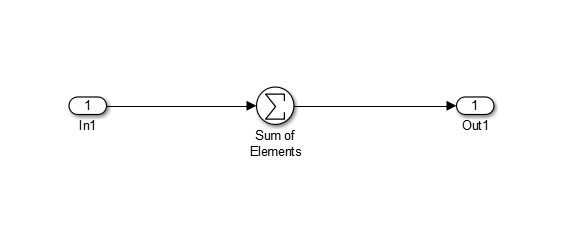

Тестируемое устройство является vsum подсистема, показанная на следующем рисунке. Подсистема содержит блок Sum, настроенный для суммирования векторов.

The simplevectorsum_cascade модель задает каскадную реализацию (SumCascadeHDLEmission) для блока Sum. Сгенерированный HDL-код для реализации блока каскадного вектора Sum запускается с двумя эффективными скоростями: более высокой (избыточная дискретизация) частотой для внутренних расчетов и более низкой частотой для ввода/вывода. HDL Coder сообщает, что неотъемлемая скорость сверхчастоты дискретизации для DUT в пять раз превышает базовую:

dut = 'simplevectorsum_cascade/vsum';

makehdl(dut);

### Generating HDL for 'simplevectorsum_cascade/vsum'

### Starting HDL Check.

### HDL Check Complete with 0 errors, 0 warnings and 0 messages.

### The code generation and optimization options you have chosen have introduced

additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for

compensation.

### The DUT requires an initial pipeline setup latency. Each output port

experiences these additional delays

### Output port 0: 1 cycles

### Begin VHDL Code Generation

### MESSAGE: The design requires 5 times faster clock with respect to the

base rate = 1.

...

В некоторых случаях требования к тактовым сигналам для такого DUT конфликтуют с глобальной частотой сверхчастоты дискретизации. Чтобы избежать конфликтов частот сверхчастоты дискретизации, проверьте, что субрейты в модели делятся равномерно на глобальную частоту сверхчастоты дискретизации.

Для примера, если вы запрашиваете глобальную скорость сверхчастоты дискретизации 8 для simplevectorsum_cascade модель, кодер отображает предупреждение и игнорирует запрошенный коэффициент избыточной дискретизации. Кодер вместо этого уважает коэффициент избыточной дискретизации, который запрашивает DUT:

dut = 'simplevectorsum_cascade/vsum'; makehdl(dut,'Oversampling',8);

### Generating HDL for 'simplevectorsum/vsum'

### Starting HDL Check.

### HDL Check Complete with 0 errors, 0 warnings and 0 messages.

### The code generation and optimization options you have chosen have introduced

additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for

compensation.

### The DUT requires an initial pipeline setup latency. Each output port

experiences these additional delays

### Output port 0: 1 cycles

### Begin VHDL Code Generation

### WARNING: The design requires 5 times faster clock with respect to

the base rate = 1, which is incompatible with the oversampling

value (8). Oversampling value is ignored.

...Коэффициент избыточной дискретизации 10 работает в этом случае:

dut = 'simplevectorsum_cascade/vsum'; makehdl(dut,'Oversampling',10);

### Generating HDL for 'simplevectorsum_cascade/vsum'

### Starting HDL Check.

### HDL Check Complete with 0 errors, 0 warnings and 0 messages.

### The code generation and optimization options you have chosen have introduced

additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for

compensation.

### The DUT requires an initial pipeline setup latency. Each output port

experiences these additional delays

### Output port 0: 1 cycles

### Begin VHDL Code Generation

### MESSAGE: The design requires 10 times faster clock with respect to

the base rate = 1.

...