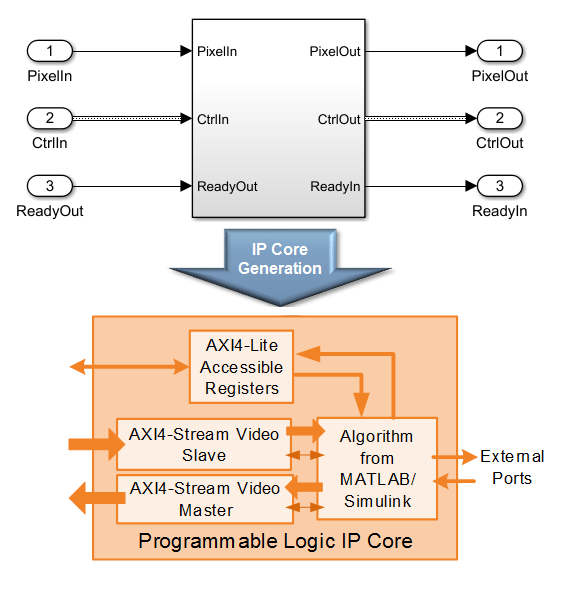

С помощью программного обеспечения HDL Coder™ можно реализовать в модели упрощенный, потоковый пиксельный протокол. Программное обеспечение генерирует IP-ядро HDL с AXI4-Stream Video интерфейсами.

Для отображения AXI4-Stream интерфейса можно использовать протокол потокового пикселя. Видео алгоритмы обрабатывают данные последовательно и генерируют видеоданные как последовательный поток пиксельных данных и управляющих сигналов. Чтобы узнать о протоколе потокового пикселя, смотрите Streaming Pixel Interface (Vision HDL Toolbox).

Чтобы сгенерировать IP-ядро с AXI4-Stream Video интерфейсами, в интерфейсе DUT реализуйте следующие сигналы:

Пиксельные данные

Пиксельная шина управления

Pixel Control Bus является шиной, которая имеет следующие сигналы:

hStart

hEnd

vStart

vEnd

valid

Сигналы hStart и hEnd представляют начало активной линии и конец активной линии соответственно. Сигналы vStart и vEnd представляют начало системы координат и конец системы координат.

Вы можете опционально смоделировать сигнал противодавления, Ready, и сопоставить его с интерфейсом AXI4-Stream Video.

Этот рисунок представляет собой изображение 2 на 3 пикселя. Активной областью изображения является прямоугольник с штриховой линией вокруг него и неактивные пиксели, которые окружают его. Пиксели маркируются своими значениями в градациях серого.

![]()

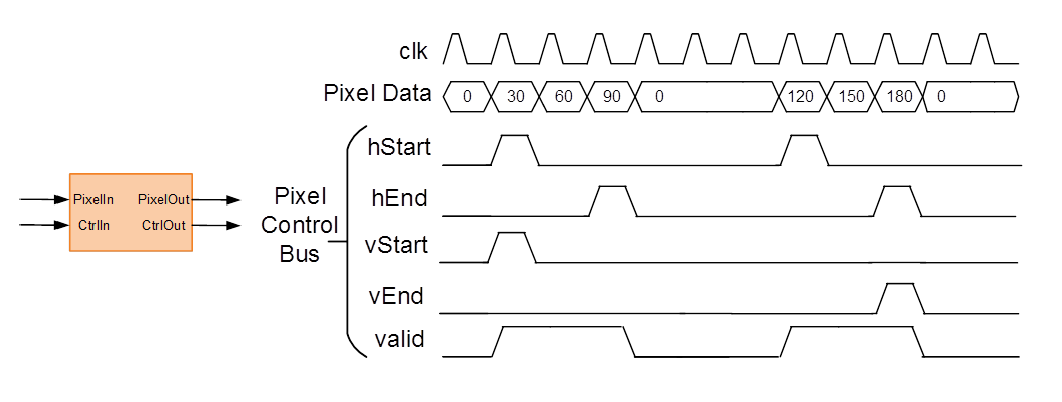

Этот рисунок показывает временную схему для сигналов Pixel Data и Pixel Control Bus, которые вы моделируете в интерфейсе DUT.

Сигнал Pixel Data является основным видеосигналом, который передается через интерфейс AXI4-Stream Video. Когда сигнал Pixel Data действителен, утверждается действительный сигнал.

Сигнал hStart становится высоким в начале активных линий. Сигнал hEnd становится высоким в конце активных линий.

Сигнал vStart становится высоким в начале активной системы координат во второй линии. Сигнал vEnd становится высоким в конце активной системы координат в третьей линии.

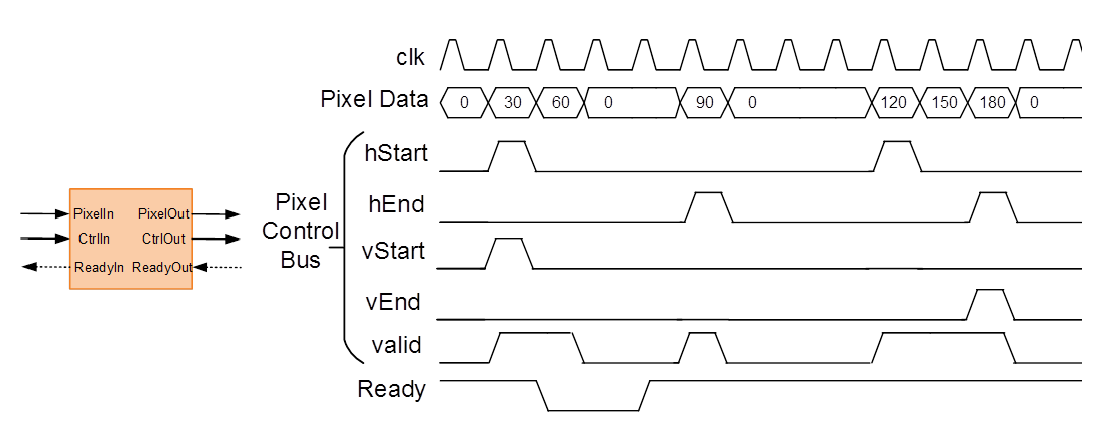

Этот рисунок показывает временную схему для Пиксельных Данных, Шины Управления Пикселей и сигнала Готовности, который вы моделируете в интерфейсе DUT.

Когда вы сопоставляете порты DUT с AXI4-Stream Video интерфейсом, можно опционально смоделировать сигнал противодавления, Ready, и сопоставить его с AXI4-Stream Video интерфейсом.

В интерфейсе Slave с сигналом Ready можно применить обратное давление. В интерфейсе Master с сигналом Ready можно ответить на задние давления.

Если вы моделируете сигнал Ready в интерфейсах AXI4-Stream Video, ваш интерфейс Master должен отключить его действительный сигнал через один цикл после отключения сигнала Ready.

Если вы не моделируете сигнал Ready, HDL Coder генерирует связанную логику противодавления.

Можно смоделировать алгоритм видео с сигналами Pixel Data и Pixel Control Bus в портах DUT и сопоставить сигналы с AXI4-Stream Video интерфейсами. Вы можете опционально смоделировать сигнал противодавления, Ready, и сопоставить его с интерфейсом AXI4-Stream Video.

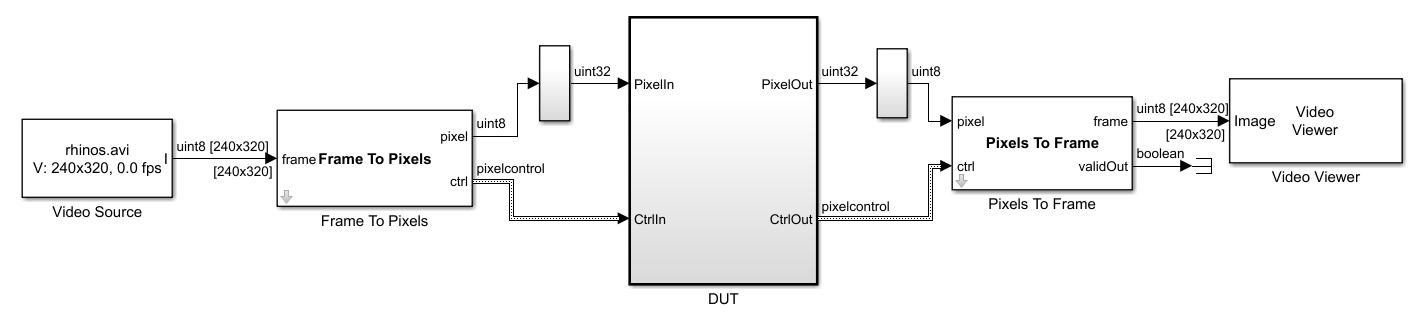

Этот рисунок показывает пример Simulink верхнего уровня® модель с входным Video Source.

Блоки Frame To Pixels и Pixels To Frame выполняют преобразование между видеокадрами и шиной Данные и Pixel Control в интерфейсе DUT. Для использования этих блоков необходимо установить Vision HDL Toolbox™.

См. также Frame To Pixels (Vision HDL Toolbox) и Pixels To Frame (Vision HDL Toolbox).

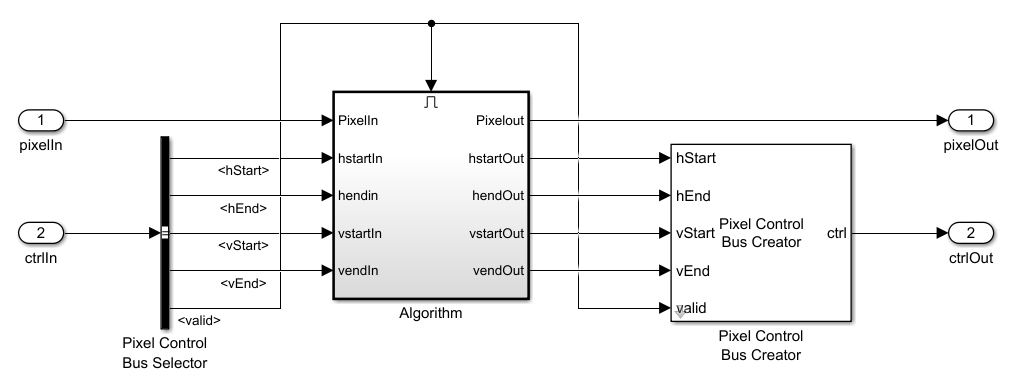

Этот рисунок показывает, как смоделировать сигналы Pixel Data и Pixel Control Bus внутри подсистемы DUT.

Можно непосредственно подключить действительный сигнал от шины управления пикселями к порту Enable. Если у вас нет программного обеспечения Vision HDL Toolbox, замените блоки Pixel Control Bus Selector и Pixel Control Bus Creator блоками Bus Selector и Bus Creator соответственно.

Интерфейсы AXI4-Stream Video в DUT могут опционально включать сигнал Ready.

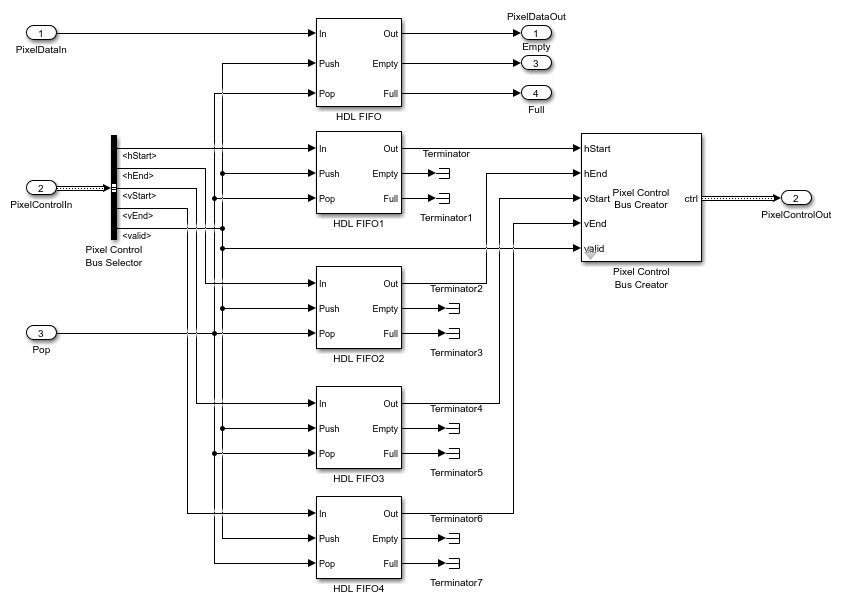

Для примера, вы можете иметь FIFO в DUT, чтобы хранить некоторые видео данных перед обработкой сигналов. Используйте Подсистему FIFO, которая содержит HDL FIFO блоков для хранения Пиксельных Данных и сигналов Шины Управления Пикселей. Чтобы применить противодавление к компоненту в восходящем направлении, моделируйте сигнал Ready на основе сигнала FIFO Full.

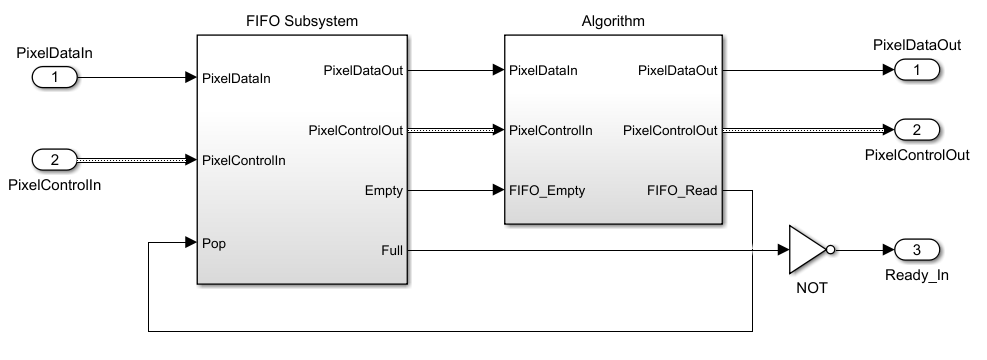

Этот рисунок показывает, как смоделировать сигнал Ready внутри подсистемы DUT.

Блок FIFO Subsystem использует HDL FIFO блоков для Пиксельных Данных и для сигналов Шины Управления Пикселей.

Отключите балансировку задержки для пути сигнала Ready. Если вы включите балансировку задержки, кодер может вставить одну или несколько задержек на сигнал Ready.

Когда вы запускаете IP Core Generation рабочий процесс, можно сопоставить несколько портов DUT с AXI4-Stream Video Master и AXI4-Stream Video Slave каналами. Порты DUT, сопоставленные с несколькими интерфейсными каналами, должны использовать скалярный тип данных. Когда вы используете векторные порты, можно сопоставить порты не более чем с одним AXI4-Stream Video Master каналом и одним AXI4-Stream Video Slave каналом.

Для получения дополнительной информации см. раздел «Генерация IP-ядра HDL с несколькими AXI4-Stream и AXI4 главными интерфейсами».

Программное обеспечение HDL Coder поддерживает проекты с несколькими скоростями дискретизации, когда вы запускаете рабочий процесс генерации ядра IP. Когда вы сопоставляете порты интерфейса с AXI4-Stream Video Master или AXI4-Stream Video Slave интерфейсами, чтобы использовать несколько частот дискретизации, убедитесь, что порты DUT, которые сопоставлены с этими AXI4 интерфейсами, работают с самой быстрой скоростью проекта после генерации HDL-кода.

Для получения дополнительной информации смотрите Multirate IP Core Generation.

Системы видеосъемки сканируют видеосигналы слева направо и сверху вниз. Когда эти системы сканируются, они генерируют неактивные интервалы между линиями и системами координат активного видео. Этот неактивный интервал называется видеоповоротом. Горизонтальное крыльцо состоит из неактивных циклов между концом одной линии и началом следующей линии. Вертикальное крыльцо состоит из неактивных циклов между конечной активной линией одной системы координат и стартовой активной линией следующей системы координат.

Этот рисунок показывает видеокадр с горизонтальным крыльцом, разделенным на переднюю и заднюю крыльца.

![]()

Интерфейс AXI4-Stream Video не требует видео-крыльца, но алгоритмы Vision HDL Toolbox требуют крыльца для обработки видеопотоков. Если входящий поток пикселей не имеет достаточного крыльца, HDL Coder вставляет необходимое количество крыльца в поток пикселей. При помощи регистров AXI4-Lite в сгенерированном IP-ядре можно настроить эти параметры крыльца для каждого видеокадра:

Активные пиксели на линию (По умолчанию: 1920)

Активные линии видео: (По умолчанию: 1080)

Горизонтальная длина крыльца (по умолчанию: 280)

Вертикальная длина крыльца (по умолчанию: 45)

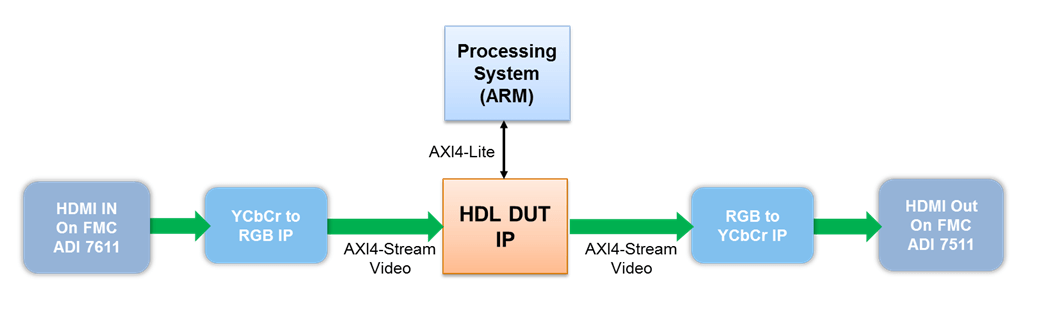

Можно интегрировать сгенерированное IP-ядро HDL с AXI4-Stream Video интерфейсами в Default video system исходный проект.

Этот рисунок является блоком Default video system исходный проект.

Вы можете использовать эту Default video system исходный проект с этими целевыми платформами:

Xilinx Zynq ZC702 evaluation kit

Xilinx Zynq ZC706 evaluation kit

ZedBoard

Как использовать Default video system Исходный проект необходимо установить пакет поддержки Computer Vision Toolbox™ для Xilinx® Zynq®-Основанное оборудование.

Когда вы сопоставляете порты DUT с AXI4-Stream Video интерфейсами:

Порт DUT, сопоставленный с сигналом Pixel Data, должен использовать скалярный тип данных.

Xilinx Zynq-7000 должна быть вашей целевой платформой.

Вы должны использовать Xilinx Vivado® как ваш инструмент синтеза.

Processor/FPGA synchronization должны быть Free running.