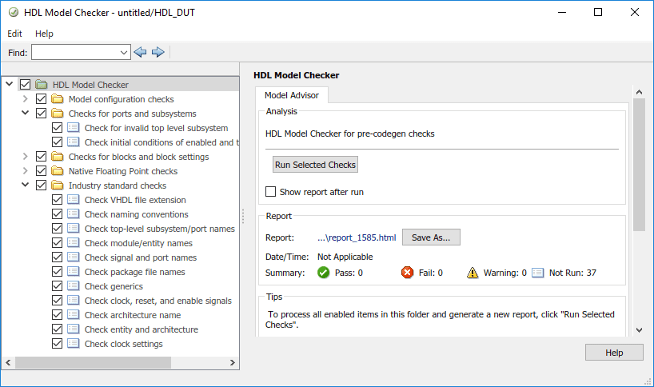

HDL-код Advisor и Model Advisor проверяют в HDL, Coder™ проверить и обновить Simulink® модель или подсистема для совместимости с генерацией HDL-кода. Code Advisor проверяет:

Моделируйте настройки конфигурации

Порты и настройки подсистемы

Блоки и настройки блоков

Собственная поддержка с плавающей точкой

Отраслевые стандартные инструкции

При запуске проверки Code Advisor отображает результат как пропуск или отказ. Можно исправить предупреждения или отказы с помощью рекомендуемых настроек Model Advisor.

Используйте проверки в этой папке, чтобы подготовить модель к совместимости с генерацией HDL-кода. Эта папка содержит проверки, которые проверяют, являются ли параметры модели HDL-совместимыми, содержит ли ваш проект алгебраические циклы и так далее.

| Имя проверки | Описание |

|---|---|

Проверьте параметры модели, подходящие для генерации HDL-кода | Проверьте параметры модели, настроенные для генерации HDL-кода. |

| Проверьте модель на наличие иностранных символов | Поиск в модели неразрешенных библиотечных ссылок, где указанный библиотечный блок не может быть найден. |

| Проверьте глобальную настройку сброса для устройств Xilinx и Altera | Проверьте настройку асинхронного сброса для Altera® устройства и установка синхронного сброса для Xilinx® устройств. |

| Проверьте настройку встроенных строений | Проверьте, есть ли у вас InlineConfigurations включен. |

| Проверяйте алгебраические циклы | Проверьте модель на алгебраические циклы. |

| Проверьте настройки визуализации | Проверьте модель на отображение настройки: типы данных портов и шага расчета расцветки. |

| Проверяйте настройку балансировки задержки | Проверка задержек сальдо включена. |

Примечание

Если вы используете Model Advisor, то увидите модель Check for foreign characters в папке Simulink.

Эта папка содержит проверки, которые проверяют, имеют ли порты и подсистемы в вашей модели настройки, совместимые с генерацией HDL-кода. Проверки включают в себя наличие действительной Подсистемы DUT верхнего уровня и определение начальных условий для блоков Enabled Subsystem и Triggered Subsystem.

| Имя проверки | Описание |

|---|---|

| Проверьте наличие недопустимой подсистемы верхнего уровня | Проверьте наличие подсистем, которые не могут быть на верхнем уровне для генерации HDL-кода. |

| Проверяйте начальные условия Enabled и Triggered подсистем | Проверяйте начальное условие Enabled и Triggered подсистем. |

Эти проверки проверяют, поддерживаются ли блоки в вашей модели для генерации HDL-кода, и имеют ли поддерживаемые блоки HDL-совместимые настройки. Проверки включают в себя, имеют ли исходные блоки в вашей модели непрерывный шаг расчета и имеет ли Stateflow® Графики и блоки MATLAB Function имеют HDL-совместимые настройки и так далее.

| Имя проверки | Описание |

|---|---|

| Проверяйте наличие бесконечных и непрерывных источников шага расчета | Проверяйте исходные блоки с непрерывным шагом расчета. |

| Проверяйте на неподдерживаемые блоки | Проверьте неподдерживаемые блоки для генерации HDL-кода. |

| Проверяйте на большие матричные операции | Проверяйте на большие матричные операции. |

| Идентифицируйте несвязанные линии, входные порты и выходные порты | Проверьте наличие несвязанных линий или портов. |

| Идентифицируйте отключенные библиотечные ссылки | Модель поиска отключенных библиотечных ссылок. |

| Идентифицируйте неразрешенные библиотечные ссылки | Поиск в модели неразрешенных библиотечных ссылок, где указанный библиотечный блок не может быть найден. |

| Проверьте настройки блока MATLAB Function | Проверьте параметры, совместимые с HDL, для блоков MATLAB Function. |

| Проверьте настройки диаграммы Stateflow | Проверьте параметры, совместимые с HDL, для блоков Stateflow Chart. |

| Проверяйте задержку, Unit Delay и блоки удержания нулевого порядка для перехода скорости | Идентифицируйте Delay, Unit Delay или Zero-Order Hold блоки, которые используются для перехода скорости. Замените эти блоки фактическими блоками Rate Transition. |

| Проверяйте блоки, которые имеют ненулевую выходную задержку | Проверяйте блоки, которые имеют ненулевую выходную задержку с фиксированной точкой и собственной плавающей точкой. |

| Проверьте неподдерживаемый класс памяти для сигнальных объектов | Проверяйте, является ли класс памяти объекта сигнала 'ExportedGlobal' или 'ImportedExtern' или 'ImportedExternPointer' |

Примечание

Если вы используете Model Advisor, то увидите Идентифицируете несвязанные линии, входные порты и выходные порты, Идентифицируете отключенные библиотечные ссылки, Идентифицируете неразрешенные библиотечные ссылки и Проверяйте задержку, Unit Delay и блоки нулевого порядка для перехода скорости в папке Simulink.

Эти проверки проверяют, совместима ли модель для генерации HDL-кода в Native Floating Point режим. Проверки включают в себя, поддерживаются ли блоки в вашей модели Simulink для генерации HDL-кода с Native Floating Point, и использует ли модель отдельные типы данных, и так далее. Нативная поддержка с плавающей точкой в HDL Coder генерирует независимый от цели HDL-код из вашей модели с одной точностью с плавающей точностью. Для получения дополнительной информации смотрите Сгенерировать независимый от цели HDL-код с собственной плавающей точкой.

| Имя проверки | Описание |

|---|---|

| Проверяйте наличие одиночных типов данных в модели | Проверяйте на single типы данных в модели. |

| Проверяйте на двойные типы данных в модели с собственной плавающей точкой | Проверяйте на double типы данных в модели. |

| Проверяйте блоки преобразования типов данных с несовместимыми настройками | Проверяйте режим преобразования блоков Data Type Conversion. |

| Проверяйте на использование HDL Returcal блоков | Проверяйте, HDL Reciprocal блоки не используют типы с плавающей точкой. |

| Проверяйте на использование блока реляционного оператора | Проверяйте, Relational Operator блоки, которые используют типы с плавающей точкой, имеют логические выходы. |

| Проверяйте неподдерживаемые блоки с собственной плавающей точкой | Проверьте неподдерживаемые блоки с собственной плавающей точкой. |

| Проверяйте блоки с ненулевой ошибкой ulp | Проверяйте блоки, которые имеют ненулевую ошибку ulp с собственной плавающей точкой. |

Эти проверки проверяют, соответствует ли ваша модель Simulink правилам отраслевого стандарта. отраслевые стандартные правила рекомендуют использовать некоторые HDL-руководства по кодированию. При генерации кода HDL Coder отображает отчет по стандарту HDL-кодирования, который показывает, насколько хорошо сгенерированный код соответствует отраслевым стандартам.

| Имя проверки | Описание |

|---|---|

| Проверьте расширение файла | Проверьте расширения файлов VHDL, содержащих сущности. |

| Проверяйте соглашения об именовании | Проверьте стандартные ключевые слова, используемые инструментами EDA. |

| Проверяйте имена подсистем/портов верхнего уровня | Проверяйте имена модулей/объектов верхнего уровня и портов. |

| Проверяйте имена модулей/объектов | Проверяйте имена модулей/объектов. |

| Проверяйте имена сигналов и портов | Проверяйте длину сигнала и имя порта. |

| Проверяйте имена файлов пакетов | Проверьте имя файла, содержащего пакеты. |

| Проверяйте дженерики | Проверьте дженерики в подсистеме верхнего уровня. |

| Проверяйте часы, сбрасывайте и активируйте сигналы | Проверьте соответствие имен для синхроимпульсов, сбросов и разрешающих сигналов. |

| Проверьте имя архитектуры | Проверьте имя архитектуры VHDL в сгенерированном HDL-коде. |

| Проверяйте сущность и архитектуру | Проверьте, описаны ли сущность и архитектура VHDL в одном файле. |

| Проверяйте настройки синхроимпульса | Проверяйте ограничения на синхросигналах. |

Для получения дополнительной информации смотрите: