Поведенческая модель интегральной схемы таймера

Simscape/Электрический/Интегральные схемы

Блок Timer является поведенческой моделью интегральной схемы таймера, такой как NE555.

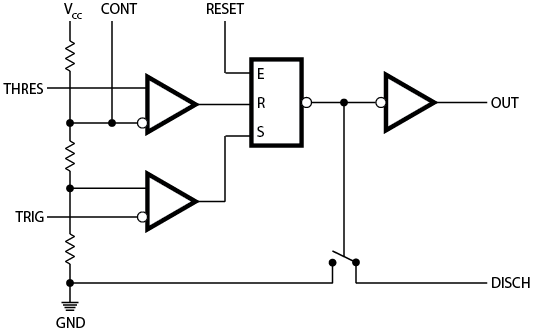

Следующий рисунок показывает структуру реализации.

В Potential divider component resistance наборов параметров значения трех резисторов, создающих делитель потенциала. Два входов компаратора имеют бесконечное входное сопротивление и нулевую входную емкость. Блок S-R Latch обеспечивает функциональность защелки сброса набора. Он включает выход конденсатор и резистор со значениями, установленными для соответствия Propagation delay значения параметров. Блок моделирует инвертор выходного каскада с помощью блока CMOS NOT. Вы задаете выходное сопротивление, низкоуровневое выходное напряжение и высокоуровневое выходное напряжение для ключа CMOS в диалоговом окне Timer блока. Разрядный переключатель аппроксимирует NPN биполярный транзистор на реальном таймере как переключатель с заданными значениями сопротивления включения и выключения.

Поведение абстрагировано. Результаты не так точны, как модель уровня транзистора.

Задержка в ответ на изменение входов зависит исключительно от постоянной времени RC сети резистор-конденсатор на выходе защелки. На практике задержка имеет более сложную зависимость от структуры устройства. Установите это значение на основе увеличения и времен спада выходного импульса.

Падение выхода напряжения является линейной функцией выхода тока. На практике, отношение является отношением двухполюсного транзистора push-pull пары.

Управляемое устройство переключателя, используемое блоком, является приближением устройства с открытым коллектором.

Источник степени соединяется внутри компонента, и блок принимает, что контакт GND заземлен.