Если вы симулируете модель с помощью кнопки Run, Simulink® Coverage™ создает отчет о покрытии модели для заданной модели с именем model_name_cov.html

Для доступа к sldemo_fuelsys модель, выполните следующие команды в MATLAB® командное окно:

addpath([matlabroot,'\examples\simulink_automotive\main']); open_system('sldemo_fuelsys');

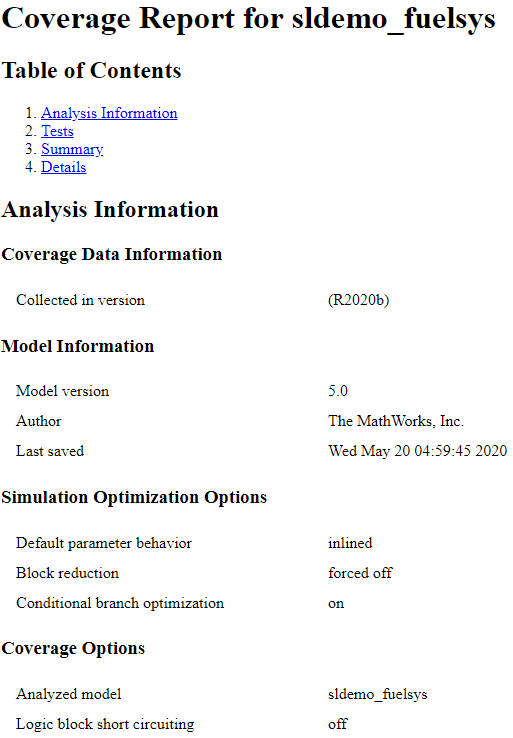

Раздел информации анализа содержит базовую информацию об анализируемой модели:

Coverage Data Information

Model Information

Harness Information (появляется, если вы записываете покрытие из Test™ обвязки Simulink)

Simulation Optimization Options

Coverage Options

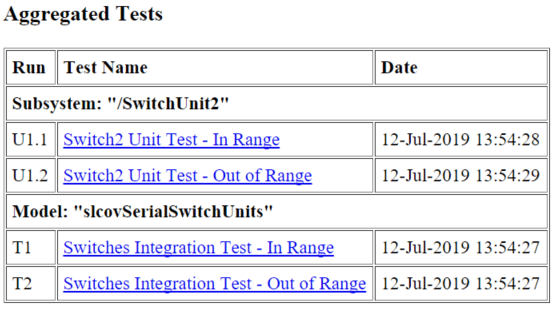

Раздел агрегированных тестов появляется, если вы:

Запишите агрегированные результаты покрытия как минимум для двух тестов через Simulink Test Manager и составьте отчет о покрытии для агрегированных результатов, или

Составьте отчет о покрытии для совокупных результатов покрытия в проводнике результатов.

Если вы запускаете тестовые случаи через Simulink Test Manager, раздел агрегированных тестов связывается со связанными тестовыми случаями в Simulink Test Manager.

Если вы агрегируете результаты тестовых примеров через проводник результатов, раздел агрегированных тестов связывается с соответствующим узлом cvdata в проводнике результатов.

Для каждого запуска в разделе агрегированных тестов существует ссылка на соответствующие результаты в Simulink Test Manager или Results Explorer.

Если вы записываете покрытие для одних или нескольких обвязок подсистемы, в разделе «Агрегированные тесты» перечисляется каждый модульный тестовый запуск.

Каждый тестируемый блок получает порядковый номер n, и каждый тест для тестируемого модуля получает порядковый номер, m в стиле Un. m.

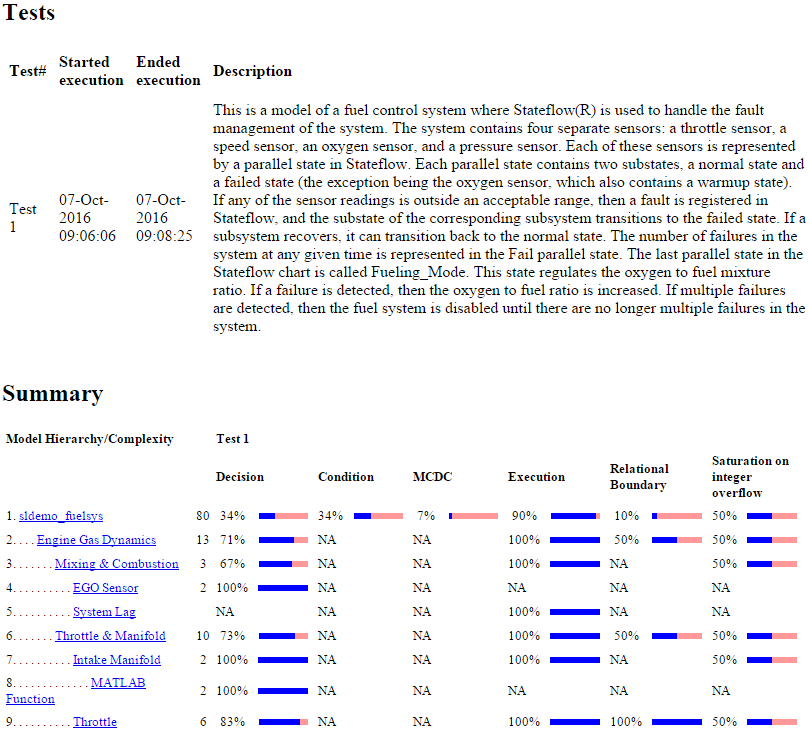

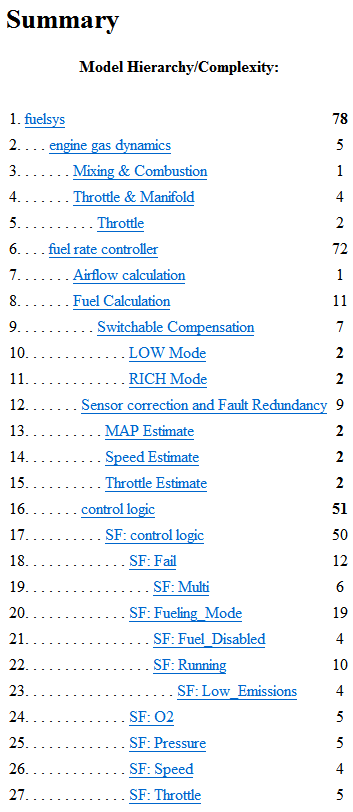

Сводные данные охвата состоят из двух подразделов:

Тесты - время начала и остановки симуляции каждого тестового примера и любые команды настройки, которые предшествовали симуляции. Заголовок для каждого теста включает любую метку теста, заданную с помощью cvtest команда. В этом разделе показано только, когда отчет не содержит раздел «Агрегированные тесты».

Сводные данные - Сводные данные результатов подсистемы. Чтобы просмотреть подробные результаты для определенной подсистемы, в подразделе «Сводка» щелкните имя подсистемы.

В разделе Details представлены подробные результаты покрытия модели. В каждом разделе подробного отчета результирующие результаты для метрик, которые тестируют каждый объект в модели:

Вы также можете получить доступ к подразделу Детали элемента модели следующим образом:

Щелкните правой кнопкой мыши элемент Simulink.

В контекстном меню выберите Coverage > Report.

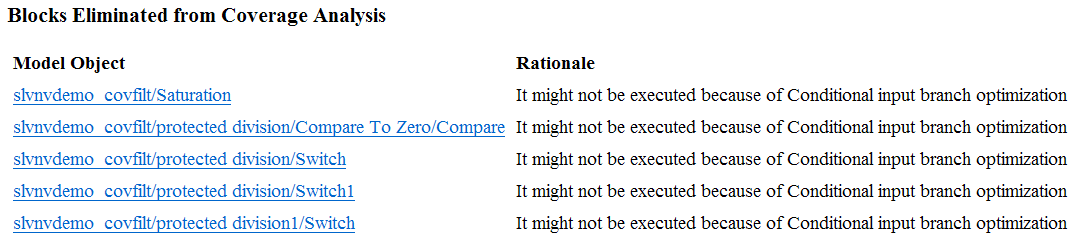

В разделе Filtered Objects перечислены все объекты модели, которые были отфильтрованы от записи покрытия, и обоснование, заданное для фильтрации этих объектов. Если правило фильтра задает, что все блоки определенного типа должны быть отфильтрованы, все эти блоки перечислены здесь.

На следующем графике было отфильтровано несколько блоков, подсистем и переходов. Два блока, связанных с библиотекой, защищенное деление и защищенное деление1, были отфильтрованы, поскольку их библиотека блоков была отфильтрована.

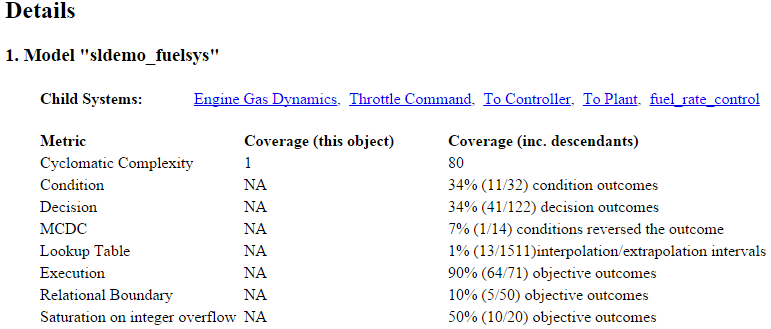

Раздел Details содержит сводные данные результатов для модели в целом, а затем список элементов. Щелкните имя элемента модели, чтобы увидеть результаты покрытия.

На следующем рисунке показан раздел Details для sldemo_fuelsys пример модели.

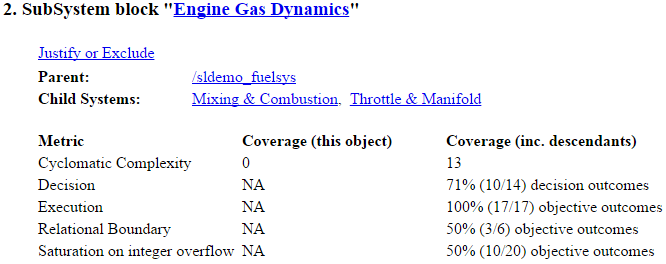

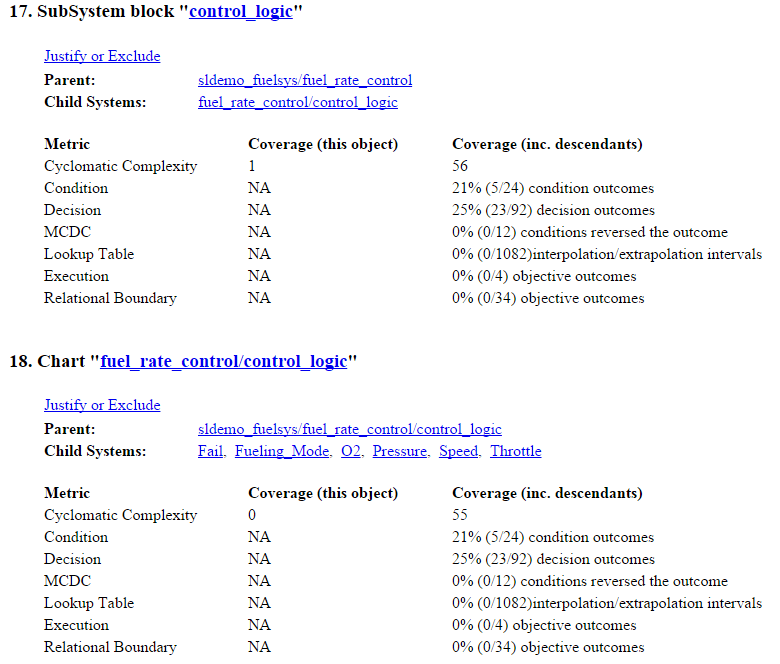

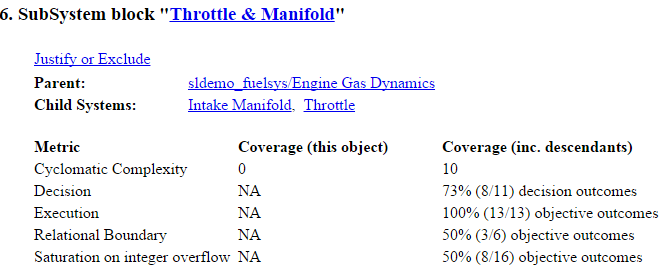

Каждый раздел Subsystem Details содержит сводные данные тестовых результатов покрытия для подсистемы и список содержащихся в ней подсистем. Далее приводятся разделы для блоков, графиков и функций MATLAB, по одному для каждого объекта, содержащего точку принятия решения в подсистеме.

Следующий рисунок показов результаты покрытия для Подсистемы Динамики Газа Двигателя в sldemo_fuelsys пример модели.

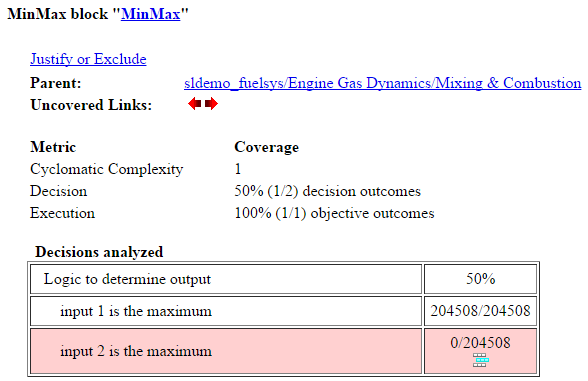

Следующий рисунок показывает результаты Decision Coverage для блока MinMax в Подсистеме Смешивания и Сгорания Подсистемы Динамики Газа Двигателя в sldemo_fuelsys пример модели.

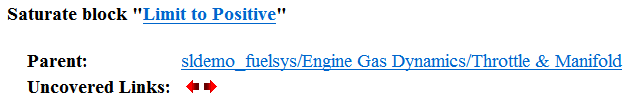

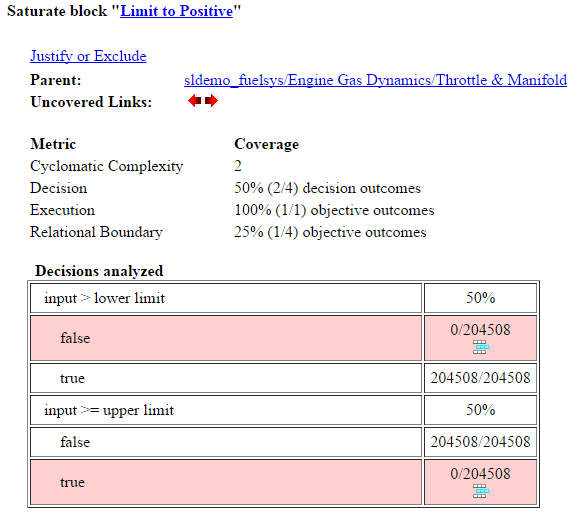

Элемент Uncovered Links впервые появляется в разделе Block Details первого блока иерархии модели, который не достигает 100% покрытия. Первый элемент Uncovered Links имеет стрелу, которая связывается с разделом Block Details в отчете следующего блока, который не достигает 100% покрытия.

Последующие блоки, которые не достигают 100% покрытия, имеют ссылки на разделы Block Details в отчете предыдущего и следующего блоков, которые не достигают 100% покрытия.

Следующий рисунок показывает результаты покрытия для Stateflow® график control_logic в sldemo_fuelsys пример модели.

Для получения дополнительной информации об отчетах о покрытии модели для диаграмм Stateflow и их объектов, смотрите Покрытие модели для диаграмм Stateflow.

По умолчанию Simulink Coverage записывает покрытие для всех функций MATLAB в модели. Функции MATLAB находятся в блоках MATLAB Function, диаграммах Stateflow или внешних файлах MATLAB.

Примечание

Подробный пример отчетов о покрытии для внешних файлов MATLAB см. в Отчете о покрытии внешних файлов MATLAB.

Чтобы записать покрытие Simulink Design Verifier™ для sldv.* функции, вызываемые функциями MATLAB, и любые блоки Simulink Design Verifier, выбирают Objectives and Constraints на панели Coverage диалогового окна Параметров конфигурации.

В следующем примере показаны детали покрытия для функции MATLAB, hFcnsInExternalEML, который вызывает четыре функции Simulink Design Verifier. В этом примере код для hFcnsInExternalEML находится во внешнем файле.

В этом примере также показаны детали покрытия Simulink Design Verifier для следующих функций:

sldv.assume (Simulink Design Verifier)

sldv.condition (Simulink Design Verifier)

sldv.prove (Simulink Design Verifier)

sldv.test (Simulink Design Verifier)

В результатах покрытия код, который достигает 100% покрытия, зеленый. Код, который достигает покрытия менее 100%, красен.

Покрытие для hFcnsInExternalEML функции и sldv.* вызовы:

Линия 1, объявление функции для hFcnsInExternalEMLзеленый, потому что симуляция выполняет эту функцию по крайней мере один раз. fcn вызывает hFcnsInExternalEML 11 раз во время симуляции.

Линия 4, sldv.assume(u1 > u2), достигает 0% покрытия, потому что u1 > u2 никогда не оценивает как true.

Линия 5, sldv.condition(u1 == 0), достигает 100% покрытия, потому что u1 == 0 вычисляет значение true по крайней мере для одного временного шага.

Линия 6, switch u1, достигает 25% охвата, потому что только один из четырех результатов в switch оператор (case 0) происходит во время симуляции.

Линия 17, sldv.test(y > u1); sldv.test (y == 4) достигает 50% покрытия. Первый sldv.test вызов достигает 100% переадресации, но второй sldv.test вызов достигает 0% переадресации.

Для получения дополнительной информации о покрытии функций MATLAB, смотрите Покрытие модели для функций MATLAB.

Для получения дополнительной информации о покрытии функций Simulink Design Verifier, смотрите Цели и Ограничения Покрытия.

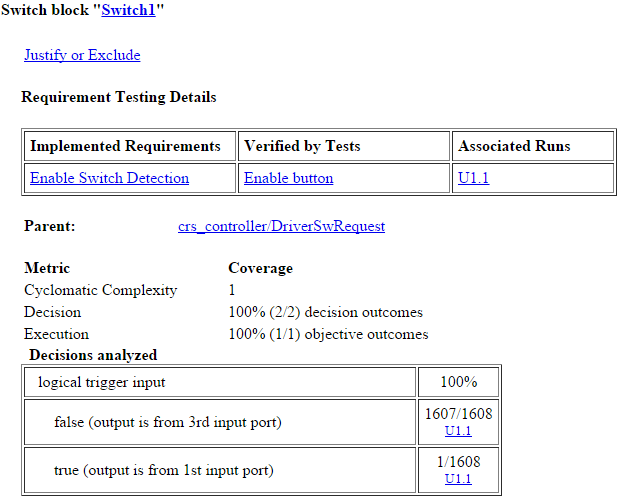

Если вы запускаете по крайней мере два тестов в Simulink Test, которые связаны с требованиями в Simulink Requirements™, в сводном отчете о покрытии подробно описываются ссылки между элементами модели, тестами и связанными требованиями.

Раздел Requirement Testing Details включает в себя:

Implemented Requirements - Какие требования связаны с элементом модели.

Verified by Tests - Какие тесты проверяют требование.

Associated Runs - Какие запуски связаны с каждым проверочным тестом.

Пример того, как проследить результаты покрытия до требований в отчете о покрытии, см. в разделе «Проследить результаты покрытия к требованиям» при помощи Simulink Test и Simulink Requirements.

Можно задать, что отчет о покрытии модели включает цикломатические номера сложности в двух местоположениях в отчете:

Раздел «Сводка» содержит цикломатические номера сложности для каждого объекта в иерархии модели. Для подсистемы или диаграммы Stateflow это число включает номера цикломатической сложности для всех их потомков.

В разделах Details для каждого объекта перечислены цикломатические номера сложности для всех отдельных объектов.

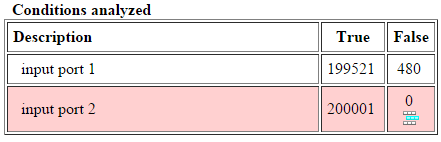

В таблице Проанализированные решения перечислены возможные результаты для решения и количество раз, когда результат произошел в каждой симуляции теста. Результаты, которые не произошли, находятся в красных подсвеченных строках таблицы.

Следующий рисунок показов анализируемую таблицу Decisions для блока Saturate в подсистеме Throttle & Manifold Подсистемы Динамики Газа Двигателя в sldemo_fuelsys пример модели.

Чтобы отобразить и выделить рассматриваемый блок, щелкните имя блока в верхней части раздела, содержащего анализируемую таблицу решений блока.

В таблице Conditions analysed перечислено количество вхождений true и false условий на каждом входном порте соответствующего блока.

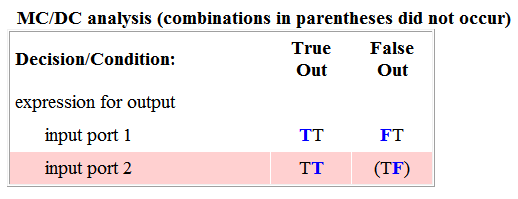

В таблице анализа MCDC перечислены случаи MCDC входа условия, представленные соответствующим блоком, и степень охвата тестов случаев условия.

Каждая строка таблицы анализа MCDC представляет случай условия для конкретного входа в блок. Пример условия для входных n блока является комбинацией входа значений. Входные n называется определяющим входом случая условия. Изменение значения входа n только изменяет значение выхода блока.

Таблица анализа MCDC показывает выражение случая условия, чтобы представлять случай условия. Условие выражения случая является символьной строкой, где:

Положение символа в строке соответствует входу номеру порта.

Символ в позиции представляет значение входа. (T означает true; F означает false).

Жирный символ соответствует значению решающего входа.

Для примера, FTF представляет случай условия для блока с тремя входами, где второй вход является определяющим входом.

Столбец «Решение/Условие» задает определяющий вход для входного случая условия. Столбец True Out задает решающее входное значение, которое заставляет блок выводить true значение для случая условия. В записи True Out используется выражение случая условия, например FF, чтобы выразить значения всех входов в блок со значением решающей переменной полужирным шрифтом.

Круглые скобки вокруг выражения указывают, что указанная комбинация входов не произошла во время первого (или только) теста, включенного в этот отчет. Другими словами, тест не охватила соответствующее условие случай. Столбец False Out задает решающее входное значение, которое заставляет блок выводить ложное значение и действительно ли это значение произошло во время первого (или только) теста, включенного в отчет.

Некоторые элементы модели достигают меньшего охвата MCDC в зависимости от определения MCDC, используемого во время анализа. Для получения дополнительной информации о том, как определение MCDC, используемое во время анализа, влияет на результаты покрытия, смотрите Определения измененного условия и Decision Coverage (MCDC) в Simulink Coverage.

Если вы выбираете Treat Simulink Logic blocks as short-circuited на панели Coverage в диалоговом окне Параметры конфигурации (Configuration Parameters), анализ покрытия MCDC не проверяет, действительно ли имеют место короткозамкнутые входы. Таблица анализа MCDC использует x в выражении условия (для примера, TFxxx) для указания короткозамкнутых входов, которые не были проанализированы инструментом.

Если вы отключите эту функцию, и блоки Logic не будут коротко замкнуты во время сбора покрытия модели, вы, возможно, не сможете достичь 100% покрытия для этого блока.

Выберите опцию Treat Simulink Logic blocks as short-circuited для того, где анализ покрытия MCDC должен аппроксимировать степень покрытия, которого вы тесты достичь для сгенерированного кода (большинство высокоуровневых языков короткой схемы логических выражений).

После того, как вы записываете последующие результаты покрытия, можно Получить доступ, Управление и Накопить Результаты покрытия, Используя Обозреватель результатов из Обозревателя результатов покрытия. По умолчанию результаты каждой симуляции сохраняются и записываются в отчете совокупно.

Если вы выбираете Show cumulative progress report в разделе Результаты параметров конфигурации, результаты, расположенные в самой правой области во всех таблицах совокупного отчета о покрытии, отражают текущее общее значение. Отчет организован таким образом, чтобы можно было легко сравнить дополнительное покрытие из последнего запуска с покрытием из всех предыдущих запусков в сеансе.

Совокупный отчет о покрытии содержит информацию о:

Текущий запуск - результаты покрытия только что завершенной симуляции.

Дельта - процент покрытия, добавленного к совокупному покрытию, достигнутому с только что завершенной симуляцией. Если совокупное покрытие предыдущей симуляции и текущее покрытие ненулевые, дельта может составлять 0, если новое покрытие не добавляет к совокупному покрытию.

Совокупный - общий охват, собранный для модели до, и включая, только что завершенную симуляцию.

После выполнения трёх тестов сводный отчет показывает, сколько дополнительного покрытия достигли третий тест и совокупного покрытия достигли для первых двух тестов.

Анализируемая таблица Decisions для совокупного покрытия содержит три столбца данных о результатах решения, которые представляют текущий запуск, дельту с момента последнего запуска и совокупные данные, соответственно.

Таблица Conditions analysed использует заголовки столбцов # n T и # n F, чтобы указать результаты для отдельных тестов. Таблица использует Tot T и Tot F для совокупных результатов. Можно идентифицировать истинные и ложные условия на каждом входном порте соответствующего блока для каждого теста.

В столбцах MCDC analysis # n True Out и # n False Out показаны случаи условия для каждого теста. В столбцах Total Out T и Total Out F показаны совокупные результаты.

Примечание

Вычислить совокупный охват для переиспользуемых подсистем и конструкций Stateflow можно в командной строке. Для получения дополнительной информации смотрите Получение совокупного покрытия для переиспользуемых подсистем и конструкций Stateflow ®.

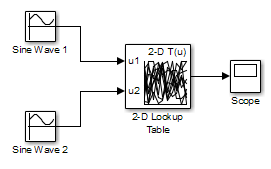

Следующий интерактивный график суммирует степень доступа к элементам массива интерполяционной таблицы. В этом примере два блока Sine Wave генерируют индексы x и y, которые получают доступ к блоку двумерная интерполяционная таблица из элементов 10 на 10, заполненных случайными значениями.

В этой модели индексы интерполяционной таблицы равны 1, 2,..., 10 в каждом направлении. Блок Sine Wave 2 находится вне фазы с блоком Sine Wave 1 на pi/2 радиана. Это генерирует числа x и y для ребра круга, которые вы видите, когда исследуете результат покрытия интерполяционных таблиц.

Отчет содержит двумерную таблицу, представляющую элементы интерполяционной таблицы. Индексы элемента представлены граничными линиями сетки камер, число которых 10 в каждой размерности. Области, где интерполируется интерполяция интерполяционной таблицы между значениями таблицы, представлены областями камер. Области экстраполяции слева от элемента 1 и справа от элемента 10 представлены камерам на ребра таблицы, которые не имеют внешней границы.

Количество значений, интерполированных (или экстраполированных) для каждой камеры (счетчики выполнения) во время проверки, представлено оттенком зеленого цвета, назначенным камере. Каждый из шести уровней зеленого затенения и представленных областей значений выполнения отображаются на одной стороне таблицы.

При клике по отдельной камере таблицы появляется диалоговое окно, в котором отображается расположение индекса камеры и точное количество счетчиков выполнения, сгенерированных для нее во время проверки. В следующем примере показано содержимое затененной цветом камеры на правом ребре окружности.

Выбранная камера обозначена красным цветом. Можно также кликнуть камеры на краю таблицы.

Жирная линия сетки указывает, что, по крайней мере, один вход блока, равный его точному значению индекса, произошел во время симуляции. Щелкните границу, чтобы отобразить точное количество попаданий для этого значения индекса.

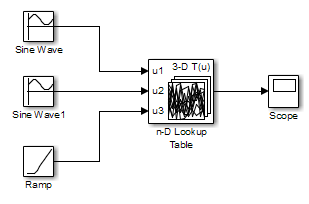

Следующая модель примера использует n-D блок Интерполяционной таблицы элементов 10 на 10 на 5, заполненных случайными значениями.

Оба X и Y таблицы осей иметь индексы 1, 2,..., 10. Ось z имеет индексы 10, 20,..., 50. К значениям интерполяционной таблицы обращаются индексы x и y, которые сгенерированы двумя блоками Sine Wave в предыдущем примере, и индекс z, который генерирует блок Ramp.

После симуляции вы увидите следующий отчет интерполяционной таблицы.

Вместо двумерной таблицы ссылка Force Map Generation отображает следующие таблицы:

Покрытие интерполяционных таблиц для трехмерного блока интерполяционной таблицы сообщается как набор двумерных таблиц.

Вертикальные планки представляют точные значения индекса: 10, 20, 30, 40, 50. Если вертикальная полоса полужирная, это указывает, что, по крайней мере, один вход блока был равен точному значению индекса, которое он представляет во время симуляции. Щелкните на панели, чтобы получить отчет о переадресации для точного значения индекса, который представляет полоса.

Вы можете сообщить о покрытии интерполяционных таблиц для интерполяционных таблиц любой размерности. Покрытие для четырехмерных таблиц сообщается как наборы трехмерных наборов, таких как в предыдущем примере. Пятимерные таблицы сообщаются как наборы наборов трехмерных наборов и так далее.

Все отчеты о покрытии модели указывают состояние параметра Simulink Block reduction в начале отчета. В следующем примере вы задаете Force block reduction off.

В следующем примере вы включили параметр Block reduction Simulink, и вы не установили Force block reduction off.

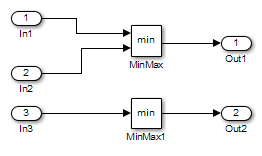

Рассмотрим следующую модель, где симуляция не выполняет блок MinMax1, потому что существует только один вход - In3.

Если вы задаете Force block reduction off, отчет не содержит данных о покрытии для этого блока, потому что минимальный вход в блок MinMax1 всегда 1.

Если вы не устанавливаете Force block reduction off, отчет не содержит данных покрытия для сокращенных блоков.

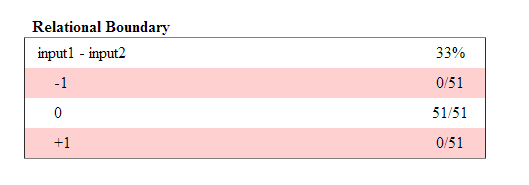

На панели покрытия диалогового окна Параметров конфигурации, если вы выбираете Relational Boundary метрику покрытия, программное обеспечение создает таблицу Relational Boundary в отчете о покрытии модели для каждого объекта модели, который поддерживается для этого покрытия. Таблица применяется к явной или неявной реляционной операции, участвующей в объекте модели. Для получения дополнительной информации смотрите:

Столбец Relational Boundary в разделе Объекты модели, которые получают покрытие.

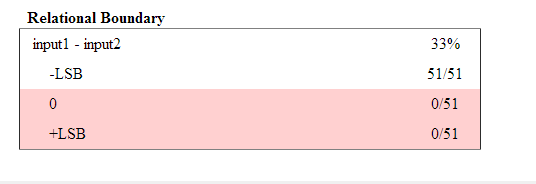

В таблицах ниже показан отчет о реляционном граничном покрытии для отношения input1 <= input2. Внешний вид таблиц зависит от типа данных операнда.

Если оба операнда являются целыми числами (или если один операнд является целым числом, а другой - булевым), таблица появляется следующим образом.

Для реляционной операции, такой как operand_1 <= operand_2

Первая строка утверждает эти два операнда в форме operand_1 - operand_2

Вторая строка указывает количество раз во время симуляции, которое operand_1 - operand_2

Третья строка указывает количество раз во время симуляции, которое operand_1operand_2

Четвертая строка указывает количество раз во время симуляции, которое operand_1 - operand_2

Если один из операндов имеет тип с фиксированной точкой, а другой операнд является либо фиксированной точкой, либо целым числом, таблица появляется следующим образом. LSB представляет значение наименее значимого бита. Для получения дополнительной информации см. раздел «Точность» (Fixed-Point Designer). Если эти два операнда имеют разную точность, используется меньшее значение точности.

Для реляционной операции, такой как operand_1 <= operand_2

Первая строка утверждает эти два операнда в форме operand_1 - operand_2

Вторая строка указывает количество раз во время симуляции, которое operand_1 - operand_2-LSB.

Третья строка указывает количество раз во время симуляции, которое operand_1operand_2

Четвертая строка указывает количество раз во время симуляции, которое operand_1 - operand_2LSB.

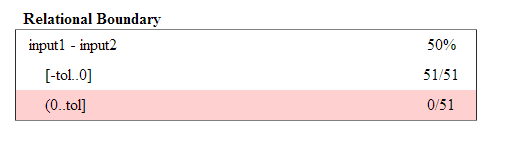

Если один из операндов имеет тип с плавающей точкой, таблица появляется следующим образом. tol представляет значение, вычисленное с использованием заданных входных значений и допуска. Если вы не задаете допуск, используются значения по умолчанию. Для получения дополнительной информации см. Раздел «Реляционное граничное покрытие».

Для реляционной операции, такой как operand_1 <= operand_2

Первая строка утверждает эти два операнда в форме operand_1 - operand_2

Вторая строка указывает количество раз во время симуляции, которое operand_1 - operand_2[-tol..0].

Третья строка указывает количество раз во время симуляции, которое operand_1 - operand_2(0..tol] во время симуляции.

Внешний вид этой таблицы изменяется согласно реляционному оператору в блоке. В зависимости от реляционного оператора, значение operand_1 - operand_2

Исключено из реляционного краевого покрытия.

Входит в область выше реляционного контура.

Входит в область ниже реляционного контура.

| Реляционный оператор | Формат отчета | Объяснение |

|---|---|---|

== | [-tol..0) | 0 исключено. |

(0..tol] | ||

!= | [-tol..0) | 0 исключено. |

(0..tol] | ||

<= | [-tol..0] | 0 включено в область ниже реляционного контура. |

(0..tol] | ||

< | [-tol..0) | 0 включено в область, расположенную выше реляционного контура. |

[0..tol] | ||

>= | [-tol..0) | 0 включено в область, расположенную выше реляционного контура. |

[0..tol] | ||

> | [-tol..0] | 0 включено в область ниже реляционного контура. |

(0..tol] |

0 включено ниже реляционного контура для <= но выше реляционного контура для <. Это правило соответствует Decision Coverage. Для образца:

Для уравнения input1 <= input2, решение верно, если input1 меньше или равно input2. < и = сгруппированы вместе. Поэтому 0 лежит в области ниже реляционного контура.

Для уравнения input1 < input2, решение верно только, если input1 меньше input2. > и = сгруппированы вместе. Поэтому 0 лежит в области над реляционным контуром.

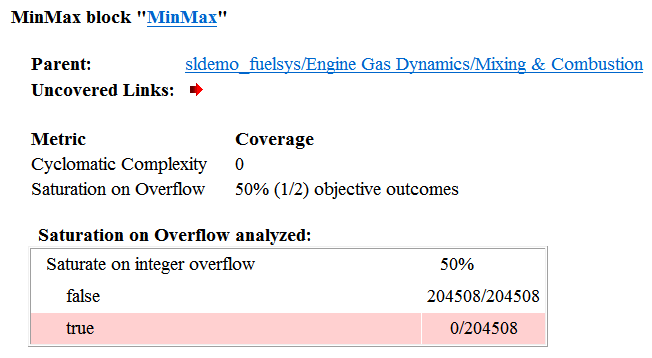

На панели покрытия диалогового окна Параметров конфигурации, если вы выбираете Saturate on integer overflow метрику покрытия, программное обеспечение создает Насыщение анализируемой таблице Переполнения отчете о покрытии модели. Программа создает таблицу для каждого блока с выбранным параметром Saturate on integer overflow.

В анализируемой таблице Насыщение при переполнении перечислено количество раз, когда блок насыщается при целочисленном переполнении, что указывает на истинное решение. Если блок не насыщается при целочисленном переполнении, таблица указывает на ложное решение. Результаты, которые не происходят, находятся в красных подсвеченных строках таблицы.

Следующий рисунок показывает таблицу Анализ насыщения по переполнению для блока MinMax в Подсистеме Смешивания и Сгорания Подсистемы Динамики Газа Двигателя в sldemo_fuelsys пример модели.

Чтобы отобразить и выделить рассматриваемый блок, щелкните имя блока в верхней части раздела, содержащего анализируемую таблицу Насыщение при переполнении блока.

![]()

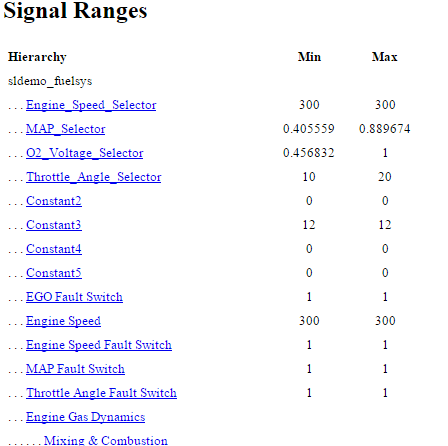

Если вы выбираете Signal Range метрику покрытия, программное обеспечение создает раздел Диапазона сигнала Analysis в нижней части отчета о покрытии модели. В этом разделе перечислены максимальное и минимальное значения сигналов для каждого выходного сигнала в модели, измеренных во время симуляции.

Быстрый доступ к отчету Диапазона сигнала Analysis с Диапазонами сигнала ссылки в области без прокатки в верхней части отчета о покрытии модели, как показано ниже в sldemo_fuelsys пример отчета модели.

Каждый блок сообщается иерархически; дочерние блоки появляются непосредственно под родительскими блоками. Каждое имя блока в отчете Диапазоны Сигнала является ссылкой. Для примера выберите EGO sensor ссылка для отображения этого блока, подсвеченного в его собственной схеме.

Если вы выбираете Signal Size, программное обеспечение создает раздел Переменные ширины сигнала после данных Диапазонов сигнала в отчете о покрытии модели. В этом разделе перечислены максимальный и минимальный размеры сигналов для всех выходных портов в модели, которые имеют сигналы переменного размера. Он также приводит память, которую Simulink выделил для этого сигнала, как измерено во время симуляции. Этот список не включает сигналы, размер которых не изменяется во время симуляции.

В следующем примере показан раздел Переменные ширины сигнала в отчете о покрытии. В этом примере размер сигнала блока Abs изменялся от 2 до 5 с выделением 5.

Каждый блок сообщается иерархически; дочерние блоки появляются непосредственно под родительскими блоками. Каждое имя блока в списке Переменные ширины сигнала является ссылкой. При нажатии на ссылку подсвечивается соответствующий блок в редакторе Simulink. После анализа сигналы переменного размера имеют более широкий проект линии.

Если вы выбираете Objectives and Constraints, анализ собирает данные о покрытии для всех блоков Simulink Design Verifier в вашей модели.

Для примера того, как это работает, откройте sldvdemo_debounce_testobjblks модель.

Эта модель содержит два блока Цели тестирования:

Блок True задает свойство, что сигнал имеет значение 2.

Ребро, внутри Подсистемы Маскированных Целей, описывает свойство, где выход блока AND в Подсистеме Маскированных Целей изменяется от 2 на 1.

Программное обеспечение Simulink Design Verifier анализирует эту модель и создает модель тестовой обвязки, которая содержит тесты, которые достигают определенных целей тестирования. Чтобы увидеть, достигает ли исходная модель этих целей, моделируйте модель тестовой обвязки и собирайте данные о покрытии модели. Этот инструмент model coverage анализирует любые точки принятия решений или значения в пределах интервала, который вы задаете в блоке Test Object.

В этом примере отчет о покрытии показывает, что вы достигли 100% покрытия блока True, потому что значение сигналов было 2 по крайней мере один раз. Было значение сигналов 2 в 6 из 14 временных шагов.

Входной сигнал к блоку Edge достиг значения True один раз из 14 временных шагов.