С Simulink® Проектируйте Verifier™, можно сгенерировать тесты для покрытия модели и пользовательских целей. Можно также измерить охват существующих основанных на требованиях тестов и расширить эти тесты, чтобы увеличить охват или достичь полного охвата.

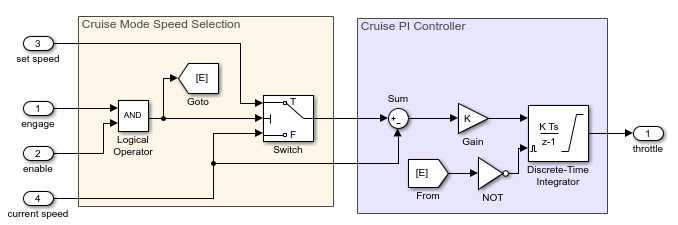

Это руководство объясняет упрощенную модель круиз-контроля, которая управляет скоростью дросселя. Вы генерируете тесты, которые удовлетворяют условию и целям покрытия модели принятия решений, а затем моделируете эти тесты, чтобы сгенерировать покрытие модели отчет.

Рассмотрим упрощенную модель круиз-контроля, которая регулирует дроссель, чтобы поддерживать устойчивую скорость, заданную установленной скоростью.

Эта модель круиз-контроля соответствует следующим требованиям:

Система управления активируется, когда engage и enable сигналы true. Это условие определяется блоком AND.

Когда система активирована, блок Switch проходит set speed на ПИ-контроллер. Система ПИ-контроллера вычисляет throttle путем интегрирования термина ошибки, заданного различием set speed - current speed.

Throttle продолжает увеличиваться или уменьшаться до тех пор, пока set speed выше или ниже current speed.

Когда система не активирована, Discrete-Time Integrator блок сбрасывается. Термин ошибки zero, что означает throttle находится в положении сброса.

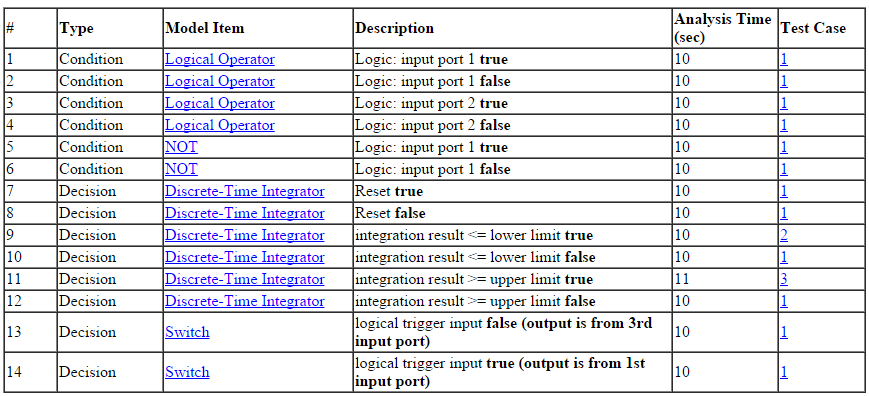

Когда вы выполняете анализ генерации тестов, Simulink Design Verifier генерирует контрольные примеры для целей покрытия модели, связанных с каждым элементом модели в модели. В таблице перечислены условия и цели Decision Coverage для связанных блоков модели. Для получения дополнительной информации о целях покрытия модели, смотрите Цели покрытия модели для Генерации тестов и Объектов модели, которые получают покрытие ( Simulink Coverage).

| Блок | Покрытие модели цели | Сгенерированный тест Описание |

|---|---|---|

| AND | Состояние | Каждое входное значение устанавливается на true или false независимо. |

| NOT | Состояние | Вход устанавливается на true или false независимо. |

| Switch | Решение | Тест демонстрирует, что Switch передает оба входных сигналов в выход. |

| Discrete-Time Integrator | Решение |

|

Результаты анализа дают подробное описание целей покрытия для каждого элемента модели и сгенерированные тесты для всех удовлетворенных целей. Вы моделируете сгенерированные тесты, чтобы измерить покрытие модели.

Откройте модель sldvexSimpleCruiseControl.

На вкладке Design Verifier, в разделе Mode, выберите Test Generation.

Чтобы сгенерировать тесты, нажмите Generate Tests.

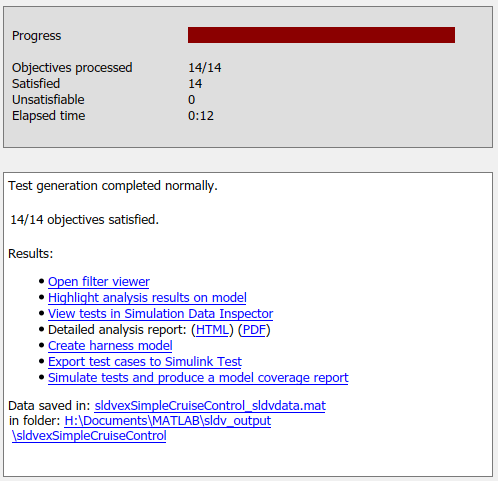

В окне Сводка результатов (Results Summary) отображаются результаты. Результат указывает, что все 14 цели satisfied.

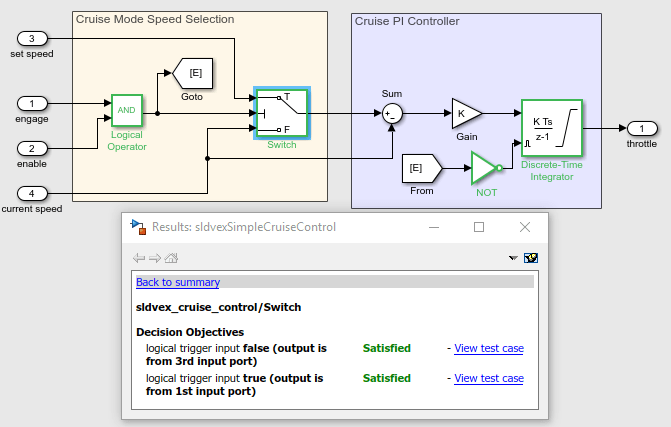

На вкладке Design Verifier, в галерее Review Results, нажмите Highlight in Model. Цели модели, которые было установлено, что программное обеспечение удовлетворено, подсвечены зеленым цветом.

Щелкните на блоке Switch. В окне Result Inspector отображаются сводные данные удовлетворенных целей принятия решений.

Эти сводные данные показывают, что все цели блока Switch удовлетворены.

Чтобы просмотреть HTML, в коллекции Review Results нажмите HTML Report.

Раздел статуса цели тестирования включает подробное описание удовлетворенных целей для каждого элемента модели и сгенерированных тестов.

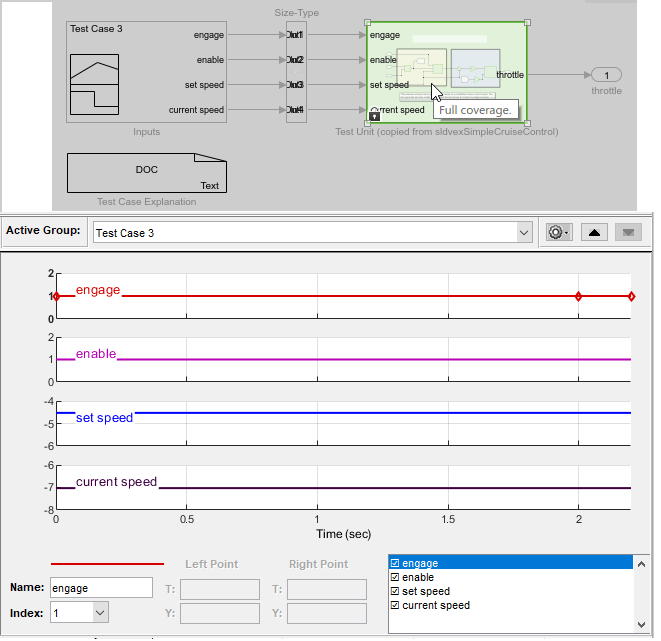

Чтобы просмотреть тест для цели покрытия модели, в окне Результата Inspector, нажмите View test case. Откроются модель тестовой обвязки и Signal Builder блок.

Чтобы симулировать тест, в блоке Signal Builder, нажмите![]() кнопку.

кнопку.

Программа моделирует тест и подсвечивает модель тестовой обвязки. Чтобы просмотреть покрытие элементов модели, наведите курсор на каждый объект модели в модели тестовой обвязки.

Проект Design Verifier: Генерация тестов | Цели Главы состояния