Определите истинную длительность на входе и создайте выходную истинную длительность на основе типа выхода

Simulink Design Verifier

True duration сигнала - последовательные временные шаги, в течение которых сигнал верен

Length истинной длительности сигнала - количество временных шагов, которые составляют истинную длительность

Input detection фаза - фаза, которая завершается на конечном временном шаге ожидаемой длины входа истинной длительности

Output construction фаза - фаза, когда блок создает истинную длительность на выходе на основе типа вывода блока

Delay duration - Количество временных шагов задержки после обнаружения входа, после чего выход сигнал равен true

Входы и выходы блока Detector имеют логический тип.

При входе обнаружении Detector блок создает сигнал выхода на основе одного из двух типов выхода, которые вы задаете:

Delayed Fixed Duration- После завершения входа и после опциональной задержки выходной сигнал становится true для фиксированного количества временных шагов. Истинная длительность выхода не зависит от входа.

Synchronized- На последнем временном шаге обнаружения входного сигнала выход становится true и остается true пока входной сигнал продолжает быть true. Истинная длительность выхода изменяется и синхронизируется с истинной длительностью входного сигнала.

Укажите, можно ли сбросить блок в начало входного обнаружения внешним логическим сигналом сброса.

Выберите Delayed Fixed Duration (по умолчанию), чтобы задать фиксированную истинную длительность для выхода после необязательной задержки. Выберите Synchronized чтобы синхронизировать выход истинную длительность с длительностью входа.

Длина истинной длительности для обнаружения входа (минимум 1).

Для Delayed Fixed Duration, опционально задайте длительность задержки, после чего выход становится true.

Для Delayed Fixed Duration, задайте длину выхода истинной длительности (minimum is 1).

В следующих примерах используйте шаг расчета 1 второе.

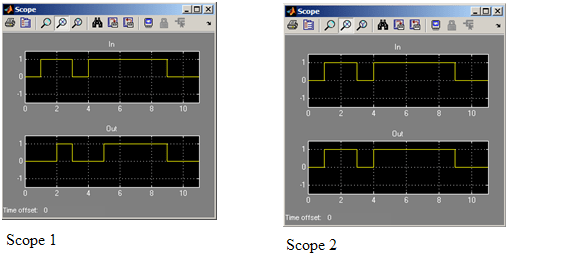

В этом примере с Output type установленным значением Delayed Fixed Durationфаза обнаружения входа не продолжается во время конструкции сигнала выхода. Следующие параметры блоков для блока Detector устанавливаются следующим образом:

Time steps for input detection = 2

Time steps for delay (optional) = 1

Time steps for output duration = 2

Осциллограф 1 показывает сценарий, где второй true длительность не обнаружена, потому что некоторые из true временные шаги происходят во время выходаконструкции.

Однако второй true длительность в возможностях 2 обнаружена, потому что оставшиеся true длительность после выходаконструкции удовлетворяет количеству шагов, требуемых для обнаружения входного сигнала.

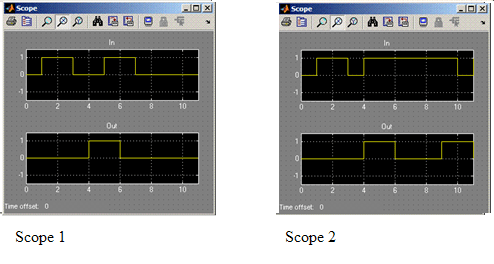

В этом примере с Output type, установленной на Synchronized и Time steps for input detection установлено на 2, выход становится true на заключительном этапе обнаружения входа. Выход продолжает оставаться верным, пока входной сигнал true.

Осциллограф 1 показывает, что выход становится истинным во втором временном шаге, который является конечным временным шагом фазы обнаружения входа. Когда количество временных шагов для обнаружения входа установлено в 1, выход идентичен входу, как вы видите в Возможностях 2.