Simulink® Design Verifier™ поддерживает поиск ошибок проектирования, генерацию тестов и проверку свойств для моделей экспорта функций. Программа создает планировщики, которые активируют модели экспорта функций, а затем выполняет анализ на модели планировщика. Можно анализировать модели экспортов функций с периодическими и апериодическими группами вызовов функций. Планировщик вызывает вызовы функции на основе шагов расчета и приоритетов, установленных в верхней модели. Для получения дополнительной информации смотрите Обзор моделей экспорта функций.

Когда вы вызываете анализ Simulink Design Verifier на модели, которая состоит из моделей экспорта функций, программное обеспечение создает модель планировщика, а затем выполняет анализ. По умолчанию модель планировщика, которую создает программное обеспечение, сохранена в этом месте <current_folder>\sldv_output\<model_name>\<model_name>_SldvScheduler.slx

В этом примере показано, как проанализировать модель примера AUTOSAR sldvExportFunction_autosar_multirunnables который состоит из периодических подсистем вызова функций.

Добавьте папку с примером в путь поиска файлов.

addpath(fullfile(docroot,'toolbox','sldv','examples'));

Откройте sldvExportFunction_autosar_multirunnables модель.

open_system('sldvExportFunction_autosar_multirunnables');Чтобы запустить анализ генерации тестов, на вкладке Design Verifier нажмите Generate Tests.

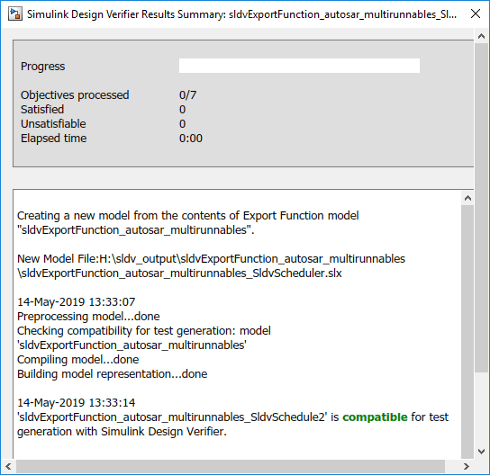

Окно Сводные Данные указывает, что модель планировщика sldvExportFunction_autosar_multirunnables_SldvScheduler.slx был создан. Можно также сгенерировать модель планировщика при помощи sldvextract.

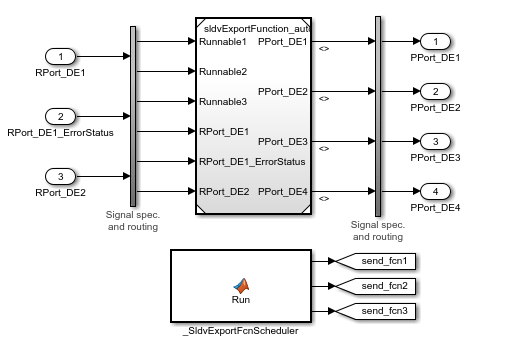

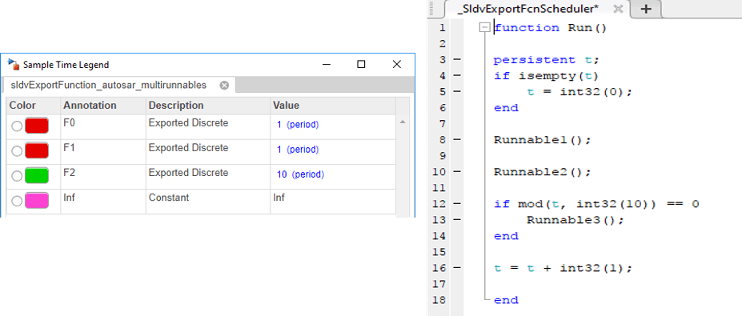

Модель планировщика состоит из блока MATLAB function _SldvExportFcnScheduler. Вызовы функций вызываются периодически, поскольку модель состоит из периодической подсистемы вызова функций.

Код MATLAB определяет порядок выполнения периодического вызова функции. The Runnable1 и Runnable2 выполняется первым, потому что период времени 1 для них обоих. После 10 временные шаги, Runnable3 выполняет.

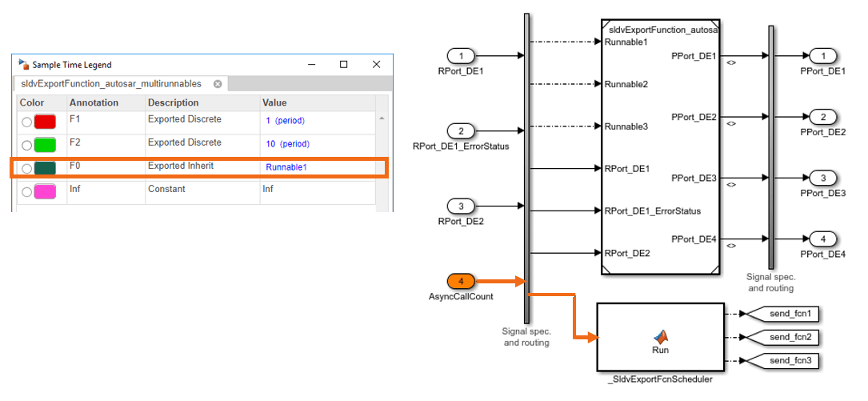

Если модель состоит из апериодических подсистем вызова функций, планировщик состоит из дополнительного порта AsyncCallCount. Значение AsyncCallCount указывает, следует ли вызывать вызов функции или нет во временном шаге.

Для примера, если Runnable1 является апериодической подсистемой вызова функций, планировщик состоит из AsyncCallCount

inport для вызова планировщика. Шаг расчета Legend и модель планировщика для апериодического вызова функции показаны на графике.

После анализа генерации тестов в сводном окне отображаются результаты, которые 7/7 цели Satisfied.

Чтобы сгенерировать отчет о покрытии путем моделирования тестов, в окне Сводных данных результатов нажмите Simulate tests and produce a model coverage report.

Программа моделирует все тесты, собирает информацию о покрытии модели и отображает отчет о покрытии.

Чтобы просмотреть детальный анализ отчет, щелкните HTML в окне Сводных данных результатов.

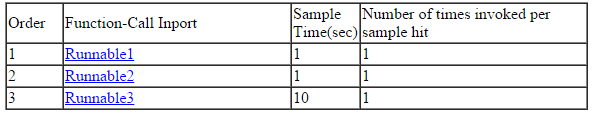

В разделе Schedule for Экспорт функций Analysis в главе Analysis Information приведено расписание для вызова экспортов функций.

Расписание для анализа экспорта функций

Анализ Simulink Design Verifier не поддерживает модель, которая состоит из экспортов функций с несколькими инициаторами вызова функции.

Маскированный блок модели, который экспортирует блок Simulink Function, не поддерживается.