Сокращение блока достигает более быстрого выполнения во время симуляции модели и в сгенерированном коде. Когда включено сокращение блоков, определенные группы блоков могут быть свернуты в один блок или даже полностью удалены.

С Simulink® Проектируйте Verifier™, сокращение блоков происходит автоматически, и блоки в неиспользованных путях кода исключаются из модели. Результаты Simulink Design Verifier не включают цели тестирования для блоков, которые были сокращены.

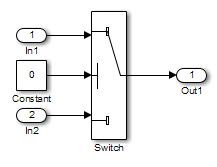

Рассмотрим Switch блок в следующей модели.

Для этого блока Switch вход управления всегда 0. Если Criteria for passing first input параметров блоков u2 ~= 0Блок Switch всегда передает третий вход в порт выхода. Когда вы анализируете эту модель, Simulink Design Verifier удаляет блок Switch из модели и не сообщает о каких-либо целях тестирования для блока Switch.

Для получения дополнительной информации о сокращении блоков смотрите описание параметра Block reduction.