Прежде чем вы симулируете модель, используйте обнаружение мертвой логики, чтобы проанализировать модель на мертвую логику. В Simulink® Design- Verifier™, поиск ошибок проектирования для мертвой логики состоит из двух опций анализа:

Мертвая логика (частичная): Если вы выбираете эту опцию, Simulink Design Verifier анализирует вашу модель, не делая никаких приближений, таких как рациональное приближение для плавающих точек или приближение цикла. Для получения дополнительной информации см. «Приближения». С помощью этой опции Simulink Design Verifier не сообщает об активной логике или неопределенных целях и может не идентифицировать какую-либо мертвую логику в вашей модели.

Эта опция доступна в:

Model Advisor. Смотрите Проверку на ошибки проектирования с использованием Model Advisor.

Диалоговое окно «Параметры конфигурации» на панели Design Verifier > Поиск Ошибок Проектирования.

Выполните исчерпывающий анализ: С помощью этой опции Simulink Design Verifier сообщает об активной логике в дополнение к мертвой логике, а также неопределенным целям. Эта опция может в некоторых случаях идентифицировать или найти дополнительную мертвую логику. Анализ может использовать приближения и сообщаться соответственно.

Эта опция доступна в диалоговом окне Параметры конфигурации (Configuration Parameters) на панели Design Verifier > Поиск Ошибок Проектирования.

Если вы не используете Model Advisor, чтобы обнаружить мертвую логику:

На вкладке Design Verifier, в разделе Mode, выберите Design Error Detection.

Нажмите Error Detection Settings.

В диалоговом окне «Параметры конфигурации» на панели Design Verifier > Поиск Ошибок Проектирования:

Включите опцию мертвая логика (частичный).

Очистить Запуск исчерпывающая опция анализа, если он выбран.

Чтобы применить эти настройки, нажмите OK и закройте диалоговое окно Параметров конфигурации.

Нажмите Detect Design Errors.

На вкладке Design Verifier, в разделе Mode, выберите Design Error Detection.

Нажмите Error Detection Settings.

В диалоговом окне Configuration Parameters на панели Проекта Verifier > Поиск ошибок проектирования включите Мертвую логику (частичный) и Запуск исчерпывающие опции анализа.

Чтобы применить эти настройки, нажмите OK и закройте диалоговое окно Параметров конфигурации.

Нажмите Detect Design Errors.

В этом примере показано, как обнаружить мертвую логику в sldvSlicerdemo_dead_logic пример модели. Обнаружение мертвой логики находит недостижимые цели в модели, которые заставляют элемент модели оставаться неактивным.

Откройте sldvSlicerdemo_dead_logic модель.

open_system('sldvSlicerdemo_dead_logic');На вкладке Design Verifier, в разделе Mode, выберите Design Error Detection.

Нажмите Error Detection Settings.

В диалоговом окне Configuration Parameters на панели Проекта Verifier > Поиск ошибок проектирования включите Мертвую логику (частичные) опции и очистите Запуск исчерпывающие опции анализа.

Нажмите Detect Design Errors.

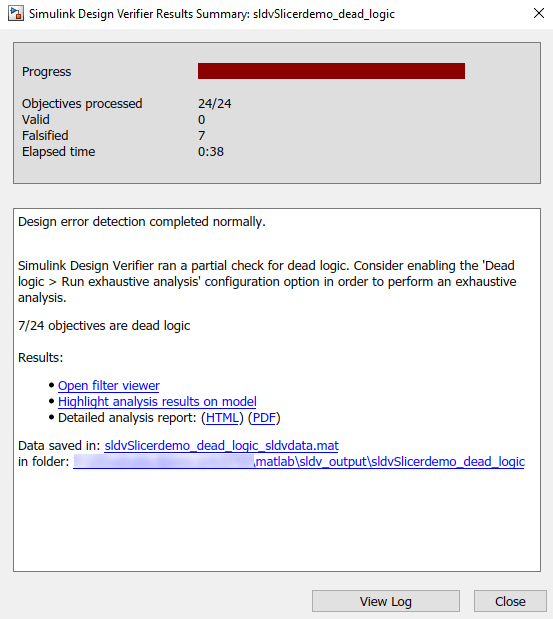

Программа анализирует модель на наличие мертвой логики и отображает результаты в окне Сводных данных результатов. Результат указывает, что семь из 24 цели были признаны мертвой логикой.

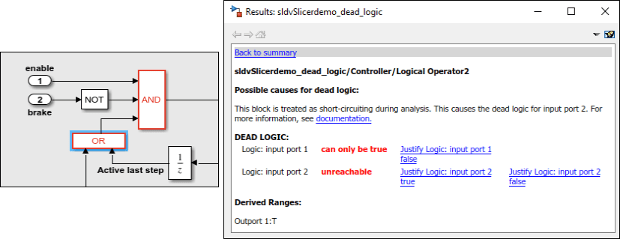

Нажмите Highlight analysis results on model. Элементы модели мертвой логики подсвечены красным цветом.

Откройте Controller

subsystem и щелкните OR блок, выделенный красным цветом. Result Inspector отображает сводные данные мертвой логики.

The set вход равен 1, так что input port 1 блока OR can only be true. Состояние подразумевает, что input port 1 ложное условие - мертвая логика. Точно так же input port 2 является unreachable, так как цель никогда не выполняется и является мертвой логикой.

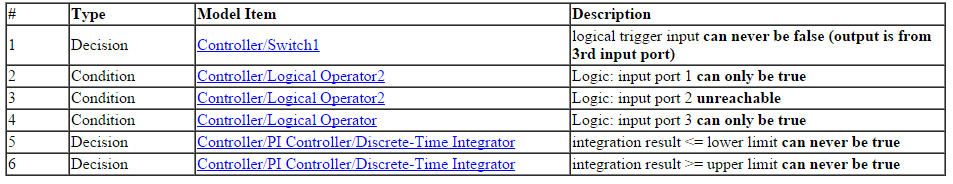

Чтобы просмотреть детальный анализ отчет, в окне Сводных данных результатов нажмите HTML.

Отчет отображает сводные данные всех результатов, которые являются мертвой логикой в модели.

Мертвая логика

Программное обеспечение сохраняет результаты детального анализа в DeadLogic field в файлах данных Simulink Design Verifier. Можно использовать файл данных для последующего анализа результатов.