В следующих разделах описывается, как анализировать sldvdemo_cruise_control_fxp_fixed модель для целочисленного переполнения и ошибок деления на нули.

Откройте и проверьте модель на целочисленное переполнение и деление на нули ошибок:

Откройте sldvdemo_cruise_control_fxp_fixed модель.

На вкладке Design Verifier, в разделе Prepare, в раскрывающемся меню настроек режима нажмите Settings.

В диалоговом окне Параметров конфигурации выберите Design Verifier > Design Error Detection.

На панели Design Error Detection выберите:

Integer overflow

Division by zero

В диалоговом окне Configuration Parameters, на Diagnostics> Data Validity панель, набор Signals> Wrap on overflow, Signals> Saturate on overflow и Parameters> Detect overflow к error.

Нажмите кнопку OK, чтобы сохранить эти настройки и закрыть диалоговое окно Параметров конфигурации.

В Mode разделе выберите Design Error Detection.

Нажмите Detect Design Errors.

Когда анализ будет завершен:

Программа подсвечивает модель с результатами анализа.

Simulink® Design Verifier™ диалоговое окно Результаты (Results), в котором отображаются сводные данные анализа.

Выведенные области значений могут помочь вам понять источник ошибки, определив возможные значения сигналов, как вы можете увидеть, выполнив следующие шаги:

На верхнем уровне sldvdemo_cruise_control_fxp_fixed щелкните Подсистему Контроллера с Фиксированной Точкой.

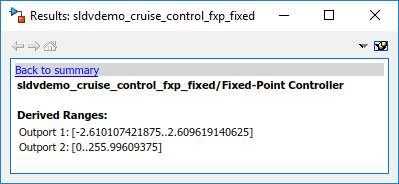

В Результаты окне Simulink Design Verifier отображается производная область значений возможных значений сигналов для Outports, рассчитанная анализом:

Значения Outport 1 (throt) варьируются от –2.6101 на 2.6096.

Значения Outport 2 (цель) варьируются от 0 на 255.9960.

Щелкните Блоки Outport sldvdemo_cruise_control_fxp_fixed модель, чтобы увидеть те же значения, связанные с сигналом.

Откройте подсистему контроллера с фиксированной точкой.

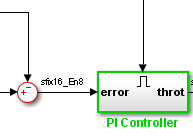

Два объекта в этой подсистеме обозначены красным цветом. Подсистема ПИ-контроллера обозначена зеленым цветом.

Щелкните блок Sum, обозначенный красным цветом, который обеспечивает вход ошибки в подсистему ПИ-контроллер.

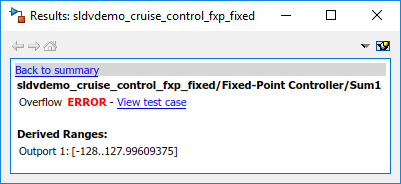

Этот блок Sum может привести к ошибке переполнения. Анализ обнаружил тест, которая может привести к расчету, где выход блока Sum превышает область значений [-128.. 127,9960].

Чтобы более полно понять эту ошибку, щелкните два блока, которые предоставляют входы блоку Sum. В окне Simulink Design Verifier Results просмотрите их производные области значений:

Третий блок Outport из Bus имеет область значений [0.. 256].

Блок Outport from the Switch имеет область значений [0.. 256].

Можно увидеть, что операция суммирования для этих диапазонов сигнала может вычислить значение, которое превышает область значений [-128.. 128] для Outport блока Sum.

Анализ сообщает об ошибке переполнения блока Sum. Анализ не распространяет эту ошибку и принимает, что выход Sum блока находится в допустимой области значений для любых последующих расчетов.

Щелкните подсистему ПИ-контроллер, обозначенную зеленым цветом. Ни один из блоков в подсистеме ПИ-контроллера не может привести к переполнению или делению на нули ошибок. Когда программа анализирует подсистему ПИ-контроллер, она игнорирует ошибку переполнения из блока Sum и принимает, что входы в подсистему действительны.

Сохраните sldvdemo_cruise_control_fxp_fixed модель открыта. В следующем разделе вы создаете модель тестовой обвязки, чтобы увидеть тест, которая генерирует Sum ошибку переполнения блока.

Чтобы увидеть тесты, которые демонстрируют ошибки, сгенерируйте модель тестовой обвязки из окна Simulink Design Verifier Results:

В sldvdemo_cruise_control_fxp_fixed моделируйте, откройте подсистему Контроллер.

Щелкните на блоке Sum, обозначенном красным цветом, который обеспечивает вход ошибки в подсистему ПИ-контроллера.

В окне Simulink Design Verifier Results отображается информация об ошибке переполнения.

В окне Simulink Design Verifier Results нажмите View test case.

Программа создает модель тестовой обвязки, содержащий тест со значениями сигналов, которые вызывают эту ошибку переполнения.

В модели тестовой обвязки откроется диалоговое окно Signal Builder с отображением теста 2.

Нажмите кнопку Start simulation, чтобы симулировать модель с этим тестом.

Как ожидалось, симуляция прекращает работать из-за ошибки переполнения блока Sum в подсистеме контроллера с фиксированной точкой.

Для получения дополнительной информации см. Simulink Design Verifier Моделей тестовой обвязки.

Просмотр отчета HTML, содержащего подробную информацию об отчете об анализе для sldvdemo_cruise_control_fxp_fixed модель:

В окне Simulink Design Verifier Results, чтобы повторно отобразить сводные данные результатов, нажмите Back to summary.

Нажмите Generate detailed analysis report.

Программа генерирует отчет о детальном анализе, который открывается в браузере.

Для sldvdemo_cruise_control_fxp_fixed модель, в Design Error Detection Objectives Status главе доклада приводятся подробные результаты по двум категориям:

Objectives Proven Valid - Объекты модели, которые не произвели ошибок

Objectives Falsified with Test Cases - Моделируйте объекты, для которых тесты генерировали ошибки

Для получения дополнительной информации см. раздел «Отчеты Simulink Design Verifier».