Simulink® Design Verifier™ рассматривает логические операции и логические выражения как короткое замыкание при анализе на мертвую логику и при генерации тестов. Для получения дополнительной информации смотрите «Короткое замыкание логических выражений для MCDC» в Анализе MCDC для каскадных логических блоков ( Simulink Coverage).

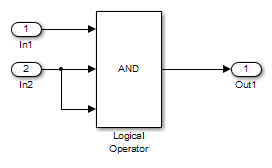

Рассмотрим следующую модель примера с Model coverage objectives набора параметров для Condition Decision. В этом случае, когда предыдущий вход сам по себе определяет выход блока, анализ игнорирует любой оставшийся блок входов. Если первый вход в блок Логического Оператора, чей параметр Operator задает AND является ложным, анализ игнорирует значения других входов.

Когда Simulink Design Verifier анализирует эту модель для покрытия Condition Decision, анализ может удовлетворить только пять из шести целей для блочных входов Логического оператора. Программное обеспечение не может сгенерировать теста, когда третий вход в блок Логического оператора является ложным. Если второй вход ложен, третий вход ложен, но программное обеспечение игнорирует третий вход из-за короткого замыкания. Если второй вход равен true, третий вход никогда не является ложным.