Отправка прерывания на процессор с оборудования

SoC Blockset/Память

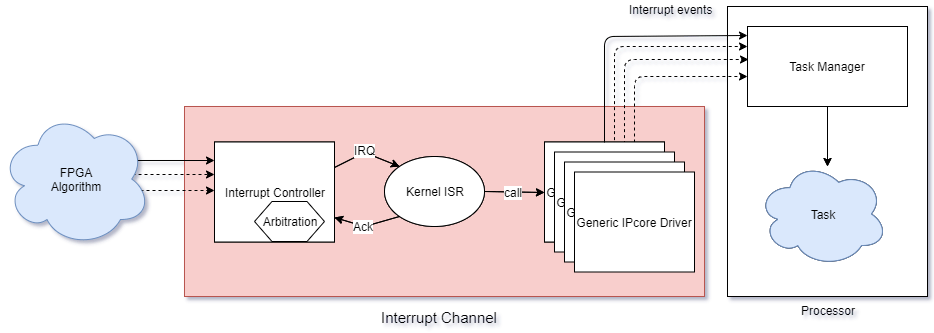

Блок Interrupt Channel получает запросы на прерывание от логики FPGA или блока Memory Channel, арбитрирует запросы и запускает управляемую событиями программную задачу к блоку Task Manager. Вы можете подключить до 16 устройств к контроллеру прерывания с одним прерыванием на устройство. Блок состоит из этих трех частей:

Контроллер прерывания - эта часть принимает запросы прерывания (IRQs) и арбитрирует их в соответствии с заданным пользователем приоритетом. Когда существуют параллельные запросы к контроллеру прерывания, запросы с более высоким приоритетом обрабатываются перед запросами с более низким приоритетом.

Ядро Interrupt Service Routine (ISR) - Эта часть получает запрос перерыва от Контроллера Перерыва, служит перерыву и посылает признать сигнал назад в Контроллер Перерыва, так, чтобы это могло обработать следующий IRQ.

Драйвер IPCore (по одному на прерывание) - Эта часть получает запрос от Kernel ISR и запускает событийно-управляемую задачу в процессоре.

Даже при том, что канал прерывания может иметь более одного выходы прерывания в сторону процессора, он отправляет процессору не более одного активного события прерывания в любой данный момент времени.

Это изображение показывает концептуальное представление блока Interrupt Channel, который принимает запросы на прерывание от алгоритма FPGA. После арбитража ядро обслуживает запрос и запускает событие в алгоритм процессора.