Используйте шаблон Stream from FPGA to Processor, чтобы создать модель SoC- Blockset™ для разработки приложения данных от оборудования (FPGA) к программному обеспечению (Processor). Чтобы создать проект с использованием шаблона «Поток на процессор», выполните шаги, чтобы Создать модель SoC с использованием шаблона SoC Blockset.

Для обработки на основе образцов дополнительные продукты не требуются.

Для обработки на основе фреймов требуется DSP System Toolbox™.

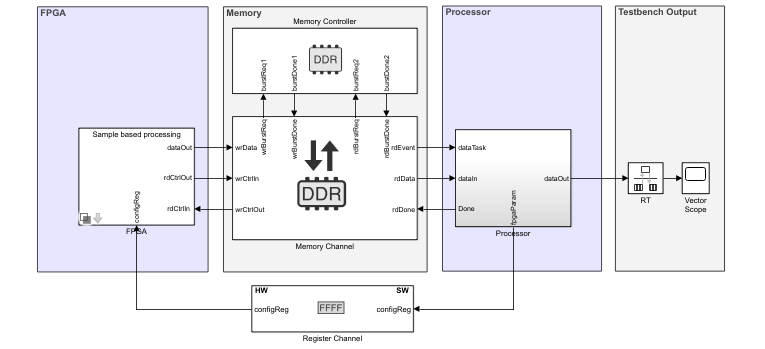

Этот шаблон моделирует счетчик как источник тестовых данных и минимальную логику для алгоритмов FPGA и процессора. Используйте этот шаблон в качестве руководства и замените алгоритм FPGA и алгоритм Processor на свои собственные функциональные возможности. Алгоритм FPGA является простым умножением, выполняемым на входных данных от источника тестирования и от параметра configReg. Процессор запишет configReg. Этот параметр моделируется с помощью блока Register Channel. Данные из алгоритма FPGA передаются в процессор через блок Memory Channel. Параметр Channel Type памяти установлен в AXI4-Stream to Software via DMA, который моделирует передачу данных DMA через общую внешнюю память.

Процессор считывает вычисленные данные из памяти и выполняет дополнительные вычисления, которые реализованы в шаблоне как сквозной провод. Вы можете просмотреть результаты симуляции, дважды кликнув по блоку Vector Scope в приемнике тестовых данных.

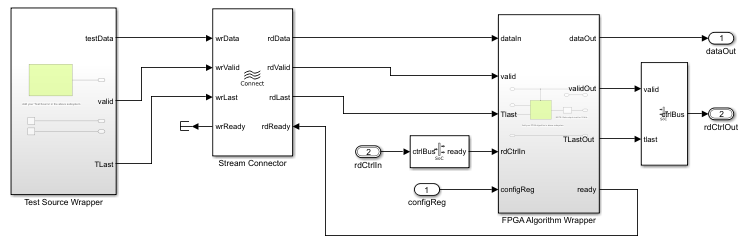

В MATLAB® панель инструментов, на вкладке Project Shortcuts , нажмите Open FPGA sample model, чтобы открыть модель FPGA. В модели две области подсвечены зеленым цветом, который представляет пользовательский код: одна в блоке FPGA Algorithm Wrapper и одна в блоке Test Source Wrapper.

FPGA Algorithm Wrapper - Дважды кликните, чтобы открыть модель. Обертка алгоритма содержит подсвеченную зеленым цветом подсистему с именем FPGA Algorithm. Этот блок имеет два входа и один выход и реализован как умножитель. Замените этот блок на свой собственный алгоритм FPGA. Добавьте входы и выходы по мере необходимости.

Test Source Wrapper - Этот блок включает источник теста и предназначен для генерации стимула в качестве входов для алгоритма FPGA. Этот блок реализован как счетчик в этом шаблоне. Измените источник теста в соответствии с вашими потребностями или замените его альтернативным исходным блоком.

Совет

Когда ваша модель FPGA включает более одного IP, необходимо задать каждый IP как подсистему и соединить подсистемы с помощью Stream Connector или Video Stream Connector блока. Для получения дополнительной информации смотрите Факторы по нескольким IP в модели FPGA.

Чтобы включить последовательное поведение симуляции, щелкните Open FPGA frame model на вкладке Project Shortcuts и повторите этот шаг. Для моделирования обработки на основе фрейма необходимо иметь лицензию DSP System Toolbox.

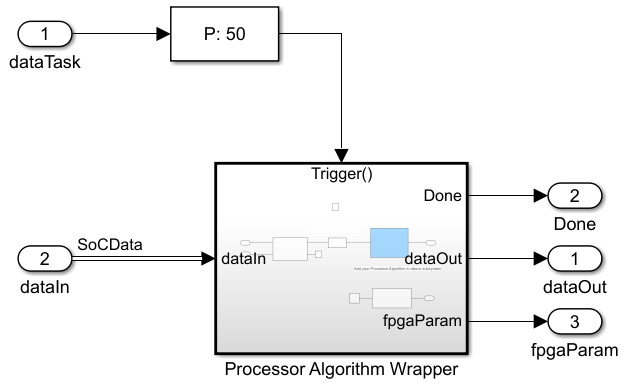

На панели инструментов MATLAB, на вкладке Project Shortcuts , нажмите Open Processor model. Оболочка процессора содержит синюю подсвеченную подсистему, представляющую пользовательский код для алгоритма процессора. Откройте оболочку Processor Algorithm и замените блок Processor Algorithm на требуемый алгоритм.

Верхняя модель шаблона также включает канал регистра для связи между процессором и моделью FPGA. Используйте канал регистра, чтобы сконфигурировать модель FPGA, или чтобы считать и проверить регистры состояния. Блок Register Channel в шаблоне включает один регистр. Чтобы добавить дополнительные регистры, вы должны изменить параметры блоков канала регистра, алгоритм FPGA и алгоритм процессора:

Добавьте регистры в канал регистра - Дважды кликните блок Register Channel, чтобы открыть маску блока и добавить дополнительные регистры по мере необходимости. Добавление регистров создает дополнительные порты на блоке Register Channel. Для получения дополнительной информации см. раздел Register Channel.

Добавьте порты к модели процессора - Перемещайтесь к модели Processor Algorithm Wrapper. Чтобы перейти к модели процессора, нажмите Open Processor model на вкладке Project Shortcuts. Дважды кликните Processor Algorithm Wrapper, чтобы изменить его.

Для регистров записи добавьте выходной порт к модулю и добавьте логику, чтобы привести значение к дополнительному выходу. Для регистров чтения добавьте порт входа и логику для обработки информации, возвращенной из регистра чтения. Из верхней модели проводите порт к блоку Register Channel.

Добавьте порты к модели FPGA - перейдите к модели FPGA Algorithm Wrapper. Чтобы перейти к модели обработки на основе FPGA/Frame, нажмите Open FPGA sample model на вкладке Project Shortcuts. Дважды кликните FPGA Algorithm Wrapper, чтобы изменить его.

Для регистров записи добавьте порт входа к модулю и логику для обработки информации, возвращенной из регистра чтения. Для регистров чтения добавьте порт выхода и логику, чтобы привести значение к добавленному порту выхода.

Для эквивалентного поведения при использовании Simulink® вариант на основе выборки, повторите этот шаг для модели обработки на основе выборки в обертке FPGA.

Из верхней модели проводите новый порт к блоку Register Channel.