Используйте шаблон Stream from Processor to FPGA, чтобы создать модель SoC- Blockset™ для разработки datapath от программного обеспечения (Processor) к оборудованию (FPGA). Чтобы создать проект с использованием шаблона Stream from Processor to FPGA, выполните шаги в разделе Создание модели SoC с использованием шаблона SoC Blockset. Затем добавьте алгоритм FPGA в подсистему FPGA и алгоритм процессора в Подсистему процессора.

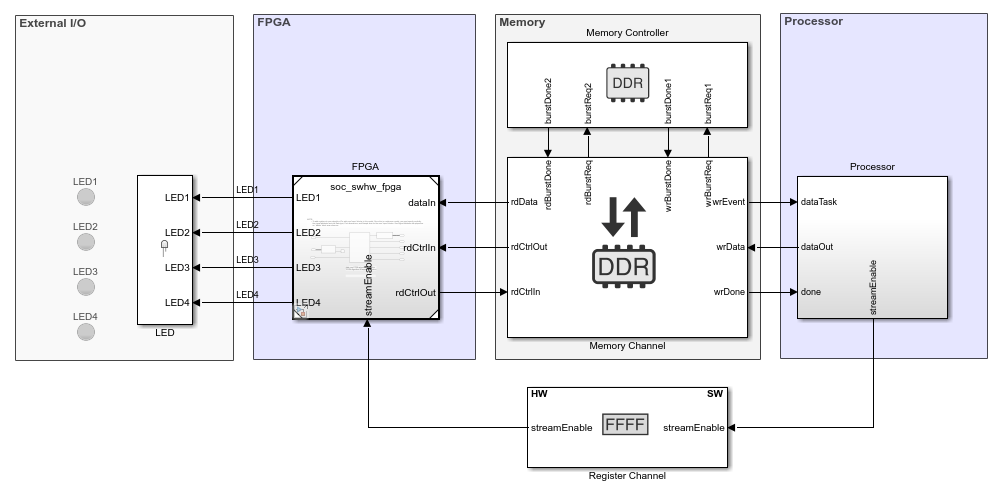

Шаблон Stream from Processor to FPGA состоит из трех моделей: модель Top, модель FPGA и модель Processor. Этот шаблон моделирует счетчик как источник тестовых данных и минимальную логику для алгоритмов FPGA и процессора. Используйте этот шаблон в качестве руководства, заменив алгоритм FPGA и алгоритм процессора на собственные функциональные возможности.

Процессор управляет сигналом выхода ready в подсистеме FPGA Algorithm Wrapper при помощи порта streamEnable. Процессор передает данные в FPGA через блок Memory Channel. Параметр Channel Type в блоке Memory Channel установлен в Software to AXI4-Stream via DMA для моделирования прямой передачи данных доступа к памяти (DMA) через общую внешнюю память.

Процессор генерирует тестовые данные и выполняет дополнительные вычисления. Дополнительные расчеты реализуются в шаблоне как сквозной провод. Затем процессор записывает вычисленные данные в память.

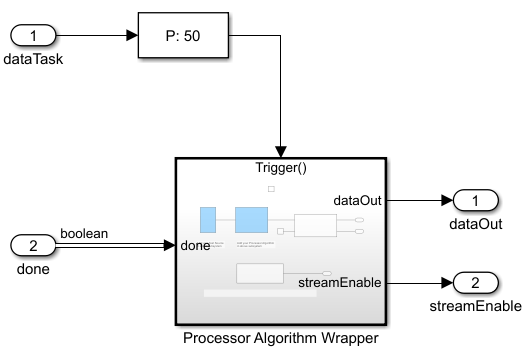

В MATLAB® Панель инструментов, на вкладке Project Shortcuts , нажмите Open Processor model, чтобы открыть модель процессора. В подсистеме Processor Algorithm Wrapper две области подсвечены синим цветом (который представляет пользовательский код), как показано на этом рисунке. Одна подсвеченная область появляется в блоке Processor Algorithm, а другая подсвеченная область - в блоке Test Source.

Блок Processor Algorithm - Замените внутренний блок Processor Algorithm (выделен синим цветом) своим желаемым алгоритмом.

Тестовый Исходный блок - Этот блок генерирует сигнал наклона. Измените источник теста в соответствии с вашими потребностями или замените его альтернативным исходным блоком.

Stream Enable for DUT block - Этот блок содержит логику управления, чтобы убедиться, что память заполнена до начала непрерывной потоковой передачи. В логике управления сигнал streamEnable устанавливается высоким только после того, как доступные буферы в канале памяти заполнены полностью.

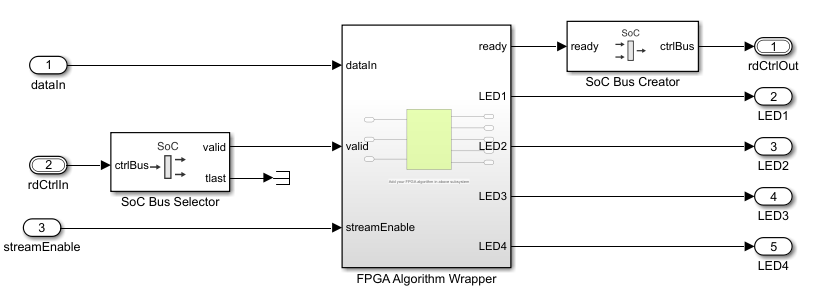

На панели инструментов MATLAB, на вкладке Project Shortcuts , нажмите Open FPGA model, чтобы открыть модель FPGA. В подсистеме FPGA Algorithm Wrapper FPGA Algorithm блок подсвечивается зеленым цветом (который представляет пользовательский код).

Дважды кликните подсистему FPGA Algorithm Wrapper, чтобы открыть модель. Алгоритм FPGA извлекает четыре бита из входных данных, чтобы управлять светодиодами на оборудовании. Состояние этих светодиодных индикаторов указывает, что процессор записывает потоковые данные в FPGA. Замените этот блок на свой собственный алгоритм FPGA. Добавьте входы и выходы по мере необходимости.

Совет

Когда ваша модель FPGA включает более одного IP, задайте каждый IP как подсистему и соедините подсистемы с помощью Stream Connector или Video Stream Connector блока. Для получения дополнительной информации смотрите Факторы по нескольким IP в модели FPGA.

Чтобы включить последовательное поведение симуляции, на вкладке Project Shortcuts нажмите Open FPGA model вкладку и повторите этот шаг.

Верхняя модель шаблона включает канал регистра для связи между процессором и моделью FPGA. Используйте канал регистра, чтобы сконфигурировать модель FPGA или считать и проверить регистры состояния. Блок Register Channel в шаблоне включает один регистр. Чтобы добавить дополнительные регистры, измените параметры блоков Register Channel, алгоритм FPGA и алгоритм процессора, выполнив эти шаги.

Добавьте регистры в канал регистра - Дважды кликните блок Register Channel, чтобы открыть маску блока и добавить дополнительные регистры по мере необходимости. Добавление регистров создает дополнительные порты на блоке Register Channel. Для получения дополнительной информации см. Register Channel блок.

Добавьте порты к модели процессора - перейдите к подсистеме Processor Algorithm Wrapper. Чтобы перейти к модели Processor, нажмите Open Processor model на вкладке Project Shortcuts. Дважды кликните подсистему Processor Algorithm Wrapper, чтобы изменить ее.

Для регистров записи добавьте порт выхода и логику, чтобы привести значение к добавленному порту выхода. Для регистров чтения добавьте порт входа и логику для обработки информации, возвращенной из регистра чтения. Из верхней модели проводите порт к блоку Register Channel.

Добавьте порты к модели FPGA - перейдите к подсистеме FPGA Algorithm Wrapper. Чтобы перейти к модели FPGA, нажмите Open FPGA model на вкладке Project Shortcuts. Дважды кликните FPGA Algorithm Wrapper подсистему, чтобы изменить ее.

Для регистров записи добавьте порт входа и логику для обработки информации, возвращенной из регистра чтения. Для регистров чтения добавьте порт выхода и логику, чтобы привести значение к добавленному порту выхода.

Из верхней модели проводите новый порт к блоку Register Channel .

Используйте шаблон для создания модели SoC