Сверхдискретизируйте, отфильтруйте и проредите входной сигнал, и генерирует оптимизированный HDL-код

Поддержка HDL DSP System Toolbox / фильтрация

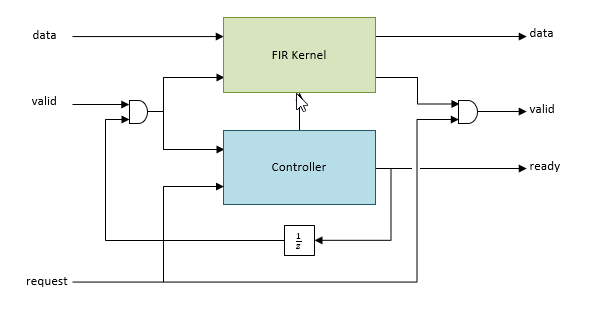

Блок FIR Rate Conversion HDL Optimized сверхдискретизировал, фильтрует и прореживает входные сигналы. Это оптимизировано для генерации HDL-кода и работает с одной выборкой каждого канала за один раз. Блок реализует многофазную архитектуру, чтобы избежать ненужных арифметических операций и высоких промежуточных частот дискретизации.

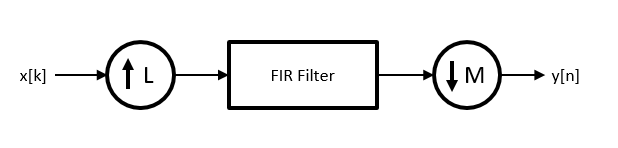

Блок сверхдискретизировал входной сигнал целочисленным коэффициентом L, применяет его к КИХ-фильтру и прореживает входной сигнал целочисленным коэффициентом M.

Можно использовать порты управления ввода и вывода для следования по потоку выборок. В настройке по умолчанию блок использует ввод и вывод управляющие сигналы valid. Для дополнительного управления потоками можно включить выходной сигнал ready и входной сигнал request.

Выходной порт ready указывает, что блок может принять новую выборку входных данных на следующем временном шаге. Когда L ≥ M, можно использовать сигнал ready достигнуть непрерывных выборок выходных данных. Если вы применяете новую входную выборку после каждого раза, когда блок возвращает сигнал ready как 1, блок возвращает выборку вывода данных с набором сигнала выхода valid к 1 на каждом временном шаге.

Когда вы отключаете порт ready, можно применить допустимую выборку данных только каждый ceil(L/M) временные шаги. Например, если:

L/M = 4/5, затем можно применить новую входную выборку на каждый временной шаг.

L/M = 3/2, затем можно применить новую входную выборку на любой временной шаг.

Когда вы включаете входной порт request, блок возвращает следующую выходную выборку, когда сигналом therequest является 1 и допустимая выходная выборка доступна. Когда вы отключаете порт request, блок возвращает выходные выборки, когда они доступны. Когда нет новых данных доступно, блок устанавливает сигнал выхода valid на 0.

Можно соединить входной порт request с выходным портом ready нисходящего блока.