Блокируйтесь параметры реализации позволяют вам управлять деталями кода, сгенерированного для определенных реализаций блока. См. Модель HDL Набора и Представления и Параметры блоков, чтобы изучить, как выбрать реализации блока и параметры в графический интерфейсе пользователя или командной строке.

Имена свойства заданы как векторы символов. Тип данных значения свойства характерен для свойства. В этом разделе описываются синтаксис каждого параметра реализации блока и как параметр влияет на сгенерированный код.

Свойства блока HDL библиотечных блоков обработаны похожие на параметры маски. Когда вы инстанцируете библиотечных блоков в своей модели, текущие свойства блока HDL того библиотечного блока копируются в экземпляры того блока в вашей модели. Свойства блока HDL этих экземпляров не синхронизируются со свойствами блока HDL библиотечного блока. Таким образом, если вы изменяете свойство блока HDL библиотечного блока, изменение не становится распространенным к экземплярам библиотечного блока, который вы уже добавили в свой Simulink® модель. Если вы хотите, чтобы свойства блока HDL библиотечного блока синхронизировались с его экземплярами в модели, создали Subsystem и затем поместили этот блок в том Subsystem. Свойства блока HDL блоков, которые находятся в библиотечном блоке, синхронизируются с соответствующими экземплярами в вашей модели.

Предположим, что библиотека содержит блок Subsystem с набором архитектуры HDL к Module. Когда вы инстанцируете этого блока в своей модели, экземпляр блока использует Module как архитектура HDL. Если вы изменяете архитектуру HDL блока Subsystem в библиотеке к BlackBox, существующие экземпляры того блока Subsystem в вашей модели все еще используют Module как архитектура HDL. Если вы теперь добавляете экземпляры блока Subsystem из библиотеки в вашей модели, новые экземпляры блока получают копию текущих свойств блока HDL, и поэтому используют BlackBox как архитектура HDL. Если вы хотите, чтобы архитектура HDL блока Subsystem в библиотеке синхронизировалась с ее экземплярами в модели, создаете подсистему обертки с архитектурой HDL, которую вы хотите в этом Subsystem.

AdaptivePipelining параметр подсистемы позволяет вам установить адаптивную конвейеризацию на подсистеме в модели.

| Адаптивная установка конвейеризации | Описание |

|---|---|

'inherit' (значение по умолчанию) | Используйте адаптивную установку конвейеризации родительской подсистемы. Если эта подсистема является подсистемой высшего уровня, используйте адаптивную установку конвейеризации для модели. |

'on' | Вставьте адаптивные трубопроводы для этой подсистемы. |

'off' | Не вставляйте адаптивные трубопроводы для этой подсистемы, даже если родительская подсистема имеет адаптивную включенную конвейеризацию. |

Чтобы отключить адаптивную конвейеризацию для подсистемы в модели, установите адаптивный параметр конвейеризации, AdaptivePipelining, к 'off' для той подсистемы.

Чтобы изучить, как установить уровень модели адаптивная конвейеризация, смотрите Адаптивную конвейеризацию.

Установить адаптивную конвейеризацию для подсистемы от диалогового окна HDL Block Properties:

Щелкните правой кнопкой по подсистеме и выберите HDL Code> HDL Block Properties.

Для AdaptivePipelining выберите inherit, on или off.

Чтобы установить адаптивную конвейеризацию для подсистемы из командной строки, использовать hdlset_param. Например, чтобы выключить адаптивную конвейеризацию для подсистемы, my_dut:

hdlset_param('my_dut', 'AdaptivePipelining', 'off')

hdlset_param.BalanceDelays параметр подсистемы позволяет вам установить задержку, балансирующуюся на подсистеме в модели.

| Установка BalanceDelays | Описание |

|---|---|

'inherit' (значение по умолчанию) | Используйте установку балансировки задержки родительской подсистемы. Если эта подсистема является подсистемой высшего уровня, используйте установку балансировки задержки для модели. |

'on' | Сбалансируйте задержки этой подсистемы. |

'off' | Не балансируйте задержки этой подсистемы, даже если родительская подсистема имеет включенную балансировку задержки. |

Чтобы отключить задержку, балансирующуюся для любой подсистемы в модели, необходимо установить параметр балансировки задержки уровня модели, BalanceDelays, к 'off'. Когда балансировка задержки включена на модели, установка балансировки задержки на отдельных подсистемах проигнорирована.

Чтобы изучить, как установить балансировку задержки уровня модели, смотрите задержки Баланса.

Установить задержку, балансирующуюся для подсистемы с помощью диалогового окна HDL Block Properties:

Щелкните правой кнопкой по подсистеме.

Выберите HDL Code> HDL Block Properties.

Для BalanceDelays выберите inherit, on или off.

Чтобы установить задержку, балансирующуюся для подсистемы из командной строки, использовать hdlset_param. Например, к задержке при выключении, балансирующейся для подсистемы, my_dut:

hdlset_param('my_dut', 'BalanceDelays', 'off')

hdlset_param.ClockRatePipelining параметр подсистемы позволяет вам установить конвейеризацию тактовой частоты на подсистеме в модели.

| Установка конвейеризации тактовой частоты | Описание |

|---|---|

'inherit' (значение по умолчанию) | Используйте установку конвейеризации тактовой частоты родительской подсистемы. Если эта подсистема является подсистемой высшего уровня, используйте установку конвейеризации тактовой частоты для модели. |

'on' | Вставьте трубопроводы тактовой частоты для этой подсистемы. |

'off' | Не вставляйте трубопроводы тактовой частоты для этой подсистемы, даже если родительская подсистема имеет включенную конвейеризацию тактовой частоты. |

Чтобы отключить конвейеризацию тактовой частоты для подсистемы в модели, установите параметр конвейеризации тактовой частоты, ClockRatePipelining, к 'off' для той подсистемы.

Чтобы изучить, как установить конвейеризацию тактовой частоты уровня модели, смотрите, что Тактовая частота конвейерно обрабатывает.

Установить конвейеризацию тактовой частоты для подсистемы с помощью диалогового окна HDL Block Properties:

Щелкните правой кнопкой по подсистеме.

Выберите HDL Code> HDL Block Properties.

Для ClockRatePipelining выберите inherit, on или off.

Чтобы установить конвейеризацию тактовой частоты для подсистемы из командной строки, использовать hdlset_param. Например, чтобы выключить конвейеризацию тактовой частоты для подсистемы, my_dut:

hdlset_param('my_dut', 'ClockRatePipelining', 'off')

hdlset_param.Когда вы будете использовать блоки Multiport Switch, используйте CodingStyle параметр, чтобы задать, хотите ли вы сгенерировать HDL-код с если еще или операторы выбора. По умолчанию HDL Coder™ генерирует если еще операторы. Если у вас есть несколько блоков Multiport Switch в вашей модели, можно принять решение задать различный CodingStyle для каждого блока.

| Установка CodingStyle | Описание |

|---|---|

'ifelse_stmt'(Значение по умолчанию) | Сгенерируйте если еще операторы в коде Verilog или когда еще операторы в коде VHDL для блока Multiport Switch. |

'case_stmt' | Сгенерируйте операторы выбора в коде Verilog или случае - когда операторы в коде VHDL для блока Multiport Switch. |

Установить CodingStyle для Multiport Switch с помощью диалогового окна HDL Block Properties:

Щелкните правой кнопкой по блоку Multiport Switch.

Выберите HDL Code> HDL Block Properties.

Для CodingStyle выберите ifelse_stmt или case_stmt.

Видеть CodingStyle заданный для подсистемы из командной строки, использовать hdlget_param. Например, чтобы видеть настройки, заданные для блока Multiport Switch в подсистеме, my_dut:

hdlget_param('my_dut/Multiport Switch', 'CodingStyle')

ans =

'case_stmt'hdlset_param.ConstMultiplierOptimization параметр реализации позволяет вам задать использование канонической цифры со знаком (CSD) или учтенную оптимизацию CSD для обработки содействующих операций множителя в сгенерированном коде.

Следующая таблица показывает ConstMultiplierOptimization значения параметров.

| Установка ConstMultiplierOptimization | Описание |

|---|---|

'none'(Значение по умолчанию) | По умолчанию HDL Coder не выполняет CSD или оптимизацию FCSD. Код, сгенерированный для блока Gain, сохраняет операции множителя. |

'CSD' | Когда вы задаете эту опцию, сгенерированный код уменьшает область, используемую моделью при поддержании или увеличении тактовой частоты, использовании методов канонической цифры со знаком (CSD). CSD заменяет операции множителя на, добавляют и вычитают операции. CSD минимизирует количество операций сложения, требуемых для постоянного умножения путем представления двоичных чисел минимальным количеством ненулевых цифр. |

'FCSD' | Эта опция использует учтенный CSD (FCSD) методы, которые заменяют операции множителя на сдвиг и добавляют/вычитают операции на определенных факторах операндов. Эти факторы являются обычно главными, но могут также быть номером близко к степени 2, который способствует сокращению области. Эта опция позволяет вам достигнуть большего сокращения области, чем CSD, за счет уменьшения тактовой частоты. |

'auto' | Когда вы задаете эту опцию, HDL Coder выбирает между CSD или оптимизацией FCSD. Кодер выбирает оптимизацию, которая дает к большей части эффективного внедрения области, на основе количества требуемых сумматоров. Когда вы задаете |

ConstMultiplierOptimization параметр доступен для следующих блоков:

Усиление

Stateflow® график

Таблица истинности

MATLAB Function

MATLAB System

Используйте ConstrainedOutputPipeline параметр, чтобы задать неотрицательное количество регистров, чтобы поместить в блоке выходные параметры.

HDL Coder перемещает существующие задержки в рамках вашего проекта, чтобы попытаться соответствовать вашему ограничению. Новые регистры не добавляются. Если существует меньше регистров, чем кодер должен удовлетворить вашему ограничению, кодер сообщает о различии между количеством желаемых и фактических выходных регистров. Можно добавить задержки с проектом с помощью конвейеризации ввода или вывода.

Распределенная конвейеризация не перераспределяет регистры, которые вы задаете с ограниченной выходной конвейеризацией.

Задавать ограниченную выходную конвейеризацию для блока с помощью графический интерфейса пользователя:

Щелкните правой кнопкой по блоку и выберите HDL Code> HDL Block Properties.

Для ConstrainedOutputPipeline введите номер регистров, которые вы хотите в выходных портах.

Задавать ограниченную выходную конвейеризацию, в командной строке, введите:

hdlset_param(path_to_block,

'ConstrainedOutputPipeline', number_of_output_registers)subsys, в вашей модели, mymodel, Введите:hdlset_param('mymodel/subsys','ConstrainedOutputPipeline', 6)

DistributedPipelining параметр включает распределение регистра трубопровода, оптимизацию скорости, которая позволяет вам увеличить свою тактовую частоту путем сокращения критического пути.

Следующая таблица показывает эффект DistributedPipelining и OutputPipeline параметры.

| DistributedPipelining | OutputPipeline, nStages | Результат |

|---|---|---|

'off' (значение по умолчанию) | Незаданный (nStages значения по умолчанию к 0) | HDL Coder не вставляет регистры трубопровода. |

nStages > 0 | Кодер вставляет nStages выведите регистры при выходе подсистемы, блока MATLAB Function или диаграммы Stateflow. | |

'on'

| Незаданный (nStages значения по умолчанию к 0) | Кодер не вставляет регистры трубопровода.DistributedPipelining не оказывает влияния. |

nStages > 0 | Кодер распределяет nStages регистры в подсистеме, блоке MATLAB Function или диаграмме Stateflow, на основе анализа критического пути. |

Чтобы достигнуть дальнейшей оптимизации кода, сгенерированного с распределенной конвейеризацией, выполните повторную синхронизацию во время синтеза RTL, если это возможно.

Совет

Выходные данные могут быть в недопустимом состоянии первоначально, если вы вставляете регистры трубопровода. Чтобы избежать ошибок испытательного стенда, следующих из начальных недопустимых выборок, отключите выходную проверку те выборки. Для получения дополнительной информации смотрите, Игнорируют выходные данные, проверяющие (количество отсчетов).

Если вы используете блок Product для умножения матриц в вашем проекте, используйте DotProductStrategy задавать, как вы хотите реализовать умножение матриц.

DotProductStrategy опции перечислены в следующей таблице.

| Значение DotProductStrategy | Описание |

|---|---|

'Fully Parallel' (значение по умолчанию) | Расширяет операцию умножения матриц во множители и сумматоры. Например, если вы умножаетесь два 2x2 матрицы, реализация использует четыре множителя и два сумматора, чтобы вычислить результат. Примечание DotProductStrategy должен быть установлен в |

'Fully Parallel Scalarized' | Расширяет операцию умножения матриц во множители и сумматоры. Например, если вы умножаетесь два 2x2 матрицы, реализация использует восемь множителей и четыре сумматора, чтобы вычислить результат. Используйте эту опцию для матриц меньшего размера и, когда это необходимо, позволять совместно использовать и на множителях и на сумматорах. |

'Serial Multiply-Accumulate' | Использует архитектуру Serial блока Multiply-Accumulate, чтобы реализовать умножение матриц. В этой архитектуре тактовая частота должна быть быстрее, чем тактовая частота, которую вы задаете с архитектурой Parallel. Вы видите тактовую частоту в информации о Сводных данных Часов отчета Генерации кода. |

'Parallel Multiply-Accumulate' | Использует архитектуру Parallel блока Multiply-Accumulate, чтобы реализовать умножение матриц. |

DSPStyle позволяет вам сгенерировать код, который включает атрибуты синтеза для отображения множителя в вашем проекте. Можно выбрать, сопоставить ли множители конкретного блока с DSPS или логикой в оборудовании.

Для Xilinx® цели, сгенерированный код использует use_dsp атрибут. Для Altera® цели, сгенерированный код использует multstyle атрибут.

DSPStyle опции перечислены в следующей таблице.

| Значение DSPStyle | Описание |

|---|---|

'none' (значение по умолчанию) | Не вставляйте DSP, сопоставляющий атрибут синтеза. |

'on' | Вставьте атрибут синтеза, который направляет инструмент синтеза, чтобы сопоставить с DSPS в оборудовании. |

'off' | Вставьте атрибут синтеза, который направляет инструмент синтеза, чтобы сопоставить с логикой в оборудовании. |

DSPStyle параметр доступен для следующих блоков:

Gain

Product

Product of Elements с набором Архитектуры к Дереву

Subsystem

Atomic Subsystem

Variant Subsystem

Enabled Subsystem

Triggered Subsystem

Model с набором Архитектуры к ModelReference

Если вы задаете иерархию, сглаживающуюся для подсистемы, которая также имеет DSPStyle не по умолчанию установка, HDL Coder распространяет DSPStyle установка на родительскую подсистему.

Если сглаженная подсистема содержит Gain, Product или блоки Product of Elements, кодер сохраняет их DSPStyle не по умолчанию настройки и значение по умолчанию замен DSPStyle настройки со сглаженной подсистемой DSPStyle установка.

Сгенерированный код для атрибутов синтеза зависит от:

Выходной язык

DSPStyle значение

SynthesisTool значение

Следующая таблица показывает примеры атрибутов синтеза в сгенерированном коде.

| Значение DSPStyle | Значение TargetLanguage | Значение SynthesisTool | |

|---|---|---|---|

'Altera Quartus II' | 'Xilinx ISE''Xilinx Vivado' | ||

'none' | 'Verilog' |

|

|

'VHDL' |

|

| |

'on' | 'Verilog' |

|

|

'VHDL' |

|

| |

'off' | 'Verilog' |

|

|

'VHDL' |

|

| |

Необходимо задать инструмент синтеза при помощи SynthesisTool свойство.

Задавать атрибут синтеза с помощью диалогового окна HDL Block Properties:

Щелкните правой кнопкой по блоку.

Выберите HDL Code> HDL Block Properties.

Для DSPStyle выберите on, off или none.

Чтобы задать атрибут синтеза из командной строки, использовать hdlset_param. Например, предположите, что у вас есть модель, my_model, с подсистемой DUT, my_dut, это содержит a. Получите блок, my_multiplier. Вставить атрибут синтеза, чтобы сопоставить my_multiplier к DSP, введите:

hdlset_param('my_model/my_dut/my_multiplier', 'DSPStyle', 'on')

hdlset_param.Когда вы задаете DSPStyle не по умолчанию блокируйте свойство, ConstMultiplierOptimization свойство должно быть установлено в 'none'.

Входные параметры к компонентам множителя не могут использовать double тип данных.

Постоянный Gain не может быть степенью 2.

FlattenHierarchy позволяет вам удалить иерархию подсистемы из HDL-кода, сгенерированного из вашего проекта.

| Установка FlattenHierarchy | Описание |

|---|---|

'inherit' (значение по умолчанию) | Используйте установку выравнивания иерархии родительской подсистемы. Если эта подсистема является подсистемой высшего уровня, не сглаживаться. |

'on' | Сгладьте эту подсистему. |

'off' | Не сглаживайте эту подсистему, даже если родительская подсистема сглажена. |

Чтобы сгладить иерархию, у вас должен также быть MaskParameterAsGeneric глобальный набор свойств к 'off'. Для получения дополнительной информации смотрите, Генерируют параметрированный HDL-код от подсистемы маскированной.

Установить выравнивание иерархии с помощью диалогового окна HDL Block Properties:

Во вкладке Apps выберите HDL Coder. Вкладка HDL Code появляется. Выберите Subsystem и затем нажмите HDL Block Properties. Для FlattenHierarchy выберите on, off или inherit.

Щелкните правой кнопкой по Subsystem и выберите HDL Code> HDL Block Properties. Для FlattenHierarchy выберите on, off или inherit.

Чтобы установить иерархию, сглаживающуюся из командной строки, использовать hdlset_param. Например, чтобы включить иерархию, сглаживающуюся для подсистемы, my_dut:

hdlset_param('my_dut', 'FlattenHierarchy', 'on')

hdlset_param.Подсистема не может быть сглажена, если подсистема:

Synchronous Subsystem или использование блок State Control в Synchronous режим.

Реализация модели - ссылки.

Триггируемая подсистема, когда триггерный сигнал Использования, когда часы включены.

Подсистема маскированная, которая содержит любое следующее:

Шина.

Перечислимый тип данных.

Блоки интерполяционной таблицы: 1-D Lookup Table, 2-D Lookup Table, Cosine HDL Optimized, Direct LookupTable (n-D), Prelookup, Sine HDL Optimized, n-D Lookup Table.

Блок MATLAB System.

Блоки Stateflow: Chart, State Transition Table, Sequence Viewer.

Блоки с передачей или никакой-op реализацией. Смотрите Проходят, Никакой HDL и Каскадные Реализации.

Примечание

Эта опция удаляет контуры подсистемы перед генерацией кода. Это не обязательно генерирует HDL-код с абсолютно плоской иерархией.

InputPipeline позволяет вам задать реализацию с входной конвейеризацией для выбранных блоков. Значение параметров задает количество входных настроек канала связи (глубина трубопровода) в сгенерированном коде.

Следующий код задает входную глубину трубопровода двух этапов для каждого блока Sum в модели:

sblocks = find_system(gcb, 'BlockType', 'Sum');

for ii=1:length(sblocks),hdlset_param(sblocks{ii},'InputPipeline', 2), end;

Примечание

InputPipeline установка не оказывает влияния на блоки, которые не имеют входного порта.

При генерации кода для регистров трубопровода HDL Coder добавляет постфиксную строку к именам регистров трубопровода ввода или вывода. Постфиксной строкой по умолчанию является _pipe. Чтобы настроить постфиксную строку, используйте опцию Pipeline postfix в панели Global Settings / General в панели HDL Code Generation диалогового окна Configuration Parameters. В качестве альтернативы можно передать желаемый постфикс как вектор символов в makehdl свойство PipelinePostfix. Для примера смотрите постфикс Трубопровода.

Для блока MATLAB function можно использовать параметр InstantiateFunctions, чтобы сгенерировать VHDL® entity или Verilog® module для каждой функции. HDL Coder генерирует код для каждого entity или module в отдельном файле.

Опции InstantiateFunctions для блока MATLAB Function перечислены в следующей таблице.

| Установка InstantiateFunctions | Описание |

|---|---|

'off' (значение по умолчанию) | Сгенерируйте код для встроенных функций. |

'on' | Сгенерируйте VHDL |

Устанавливать параметр InstantiateFunctions с помощью диалогового окна HDL Block Properties:

Щелкните правой кнопкой по блоку MATLAB Function.

Выберите HDL Code> HDL Block Properties.

Для InstantiateFunctions выберите on.

Чтобы установить параметр InstantiateFunctions из командной строки, использовать hdlset_param. Например, чтобы сгенерировать instantiable код для функций в блоке MATLAB Function, myMatlabFcn, в вашей подсистеме DUT, myDUT, Введите:

hdlset_param('my_DUT/my_MATLABFcnBlk', 'InstantiateFunctions', 'on')Если вы хотите сгенерировать instantiable код для некоторых функций, но не других, позвольте опции сгенерировать instantiable код для функций и использование coder.inline. Смотрите coder.inline для деталей.

Программное обеспечение генерирует код, встроенный когда:

Вызовы функции в рамках условного кода или for циклы.

Любая функция вызвана с непостоянным struct входной параметр.

Функция имеет состояние, такое как персистентная переменная, и вызвана многократно.

Существует перечисление где угодно в функции проекта.

Для Cascade архитектура, можно использовать параметр InstantiateStages, чтобы сгенерировать VHDL entity или Verilog module для каждого этапа расчета. HDL Coder генерирует код для каждого entity или module в отдельном файле.

| Установка InstantiateStages | Описание |

|---|---|

'off' (значение по умолчанию) | Сгенерируйте каскадные этапы в одном VHDL |

'on' | Сгенерируйте VHDL |

LoopOptimization позволяет вам передать потоком или развернуть циклы в коде, сгенерированном от блока MATLAB Function. Потоковая передача цикла оптимизирует для области; развертывание цикла оптимизирует для скорости.

Примечание

Если вы задаете MATLAB Datapath архитектура блока MATLAB Function, можно только развернуть циклы. К потоковым циклам можно использовать оптимизацию потоковой передачи путем определения StreamingFactor. Смотрите Оптимизацию HDL Через Контур блока MATLAB function Используя MATLAB Архитектура Datapath.

| Установка LoopOptimization | Описание |

|---|---|

'none' (значение по умолчанию) | Не оптимизируйте циклы. |

'Unrolling' | Разверните циклы. |

'Streaming' | Потоковые циклы. |

Выбрать оптимизацию цикла с помощью диалогового окна HDL Block Properties:

Щелкните правой кнопкой по блоку MATLAB Function.

Выберите HDL Code> HDL Block Properties.

Для LoopOptimization выберите none, Unrolling, или Streaming.

Чтобы выбрать оптимизацию цикла из командной строки, использовать hdlset_param. Например, чтобы включить потоковую передачу цикла для блока MATLAB Function, my_mlfn:

hdlset_param('my_mlfn', 'LoopOptimization', 'Streaming')

hdlset_param.HDL Coder не может передать цикл потоком если:

Индекс цикла считает в обратном порядке. Индекс цикла должен увеличиться на 1 на каждой итерации.

Существует 2 или больше вложенных цикла на том же уровне иерархии в другом цикле.

Какая-то конкретная персистентная переменная обновляется и внутри и снаружи цикла.

HDL Coder может передать цикл потоком, когда персистентная переменная:

Обновленный в цикле и читают вне цикла.

Читайте в цикле и обновленный вне цикла.

Используйте LUTRegisterResetType параметры блоков, чтобы управлять синтезом LUT в структуру ROM на FPGA.

| Значение LUTRegisterResetType | Описание |

|---|---|

default | LUT регистр выхода имеет логику сброса по умолчанию. Когда вы сгенерируете HDL, LUT будет синтезироваться как регистры. |

none | LUT регистр выхода не имеет никакой логики сброса. Когда вы сгенерируете HDL, LUT будет синтезироваться как ROM. |

Можно задать LUTRegisterResetType для следующих блоков:

Gamma Correction

Lookup Table

Блок NCO HDL Optimized игнорирует этот параметр.

С MapPersistentVarsToRAM параметр реализации, можно использовать основанное на RAM отображение для персистентных массивов блока MATLAB Function вместо того, чтобы сопоставить с регистрами.

| Установка MapPersistentVarsToRAM | Отображение поведения |

|---|---|

| Персистентные массивы сопоставляют с регистрами в сгенерированном HDL-коде. |

| Персистентные переменные типа массив сопоставляют с RAM. Для ограничений смотрите, что RAM Сопоставляет Ограничения. |

Когда вы включаете отображение RAM, персистентный массив или пользовательская Система object™ частная собственность сопоставляют с блоком RAM, когда все следующие условия верны:

Каждый доступ для чтения или доступ для записи для одного элемента только. Например, доступ к субматрице и копии массивов не позволены.

Логика расчета адреса не зависима чтением. Например, расчет чтения или адреса записи с помощью данных, считанных из массива, не позволен.

Персистентные переменные или пользовательские частные свойства Системного объекта инициализируются к 0, если у них есть циклическая зависимость. Например, если у вас есть две персистентных переменные, A и B, у вас есть циклическая зависимость, если A зависит от B, и B зависит от A.

Если доступ в условном операторе, условный оператор использует только простые логические выражения (&&, ||, ~) или операторы отношения. Например, в следующем коде, r1 не сопоставляет с RAM:

if (mod(i,2) > 0)

a = r1(u);

else

r1(i) = u;

end Перепишите комплексные условия, такие как условия, которые вызывают функции путем присвоения их временным переменным и использования временных переменных в условном операторе. Например, чтобы сопоставить r1 к RAM перепишите предыдущий код можно следующим образом:

temp = mod(i,2);

if (temp > 0)

a = r1(u);

else

r1(i) = u;

end Персистентный массив или пользовательское значение частной собственности Системного объекта зависят от внешних входных параметров.

Например, в следующем коде, bigarray не сопоставляет с RAM, потому что он не зависит от u:

function z = foo(u)

persistent cnt bigarray

if isempty(cnt)

cnt = fi(0,1,16,10,hdlfimath);

bigarray = uint8(zeros(1024,1));

end

z = u + cnt;

idx = uint8(cnt);

temp = bigarray(idx+1);

cnt(:) = cnt + fi(1,1,16,0,hdlfimath) + temp;

bigarray(idx+1) = idx; RAMSize больше или равен RAMMappingThreshold значение. RAMSize продукт NumElements * WordLength * Complexity.

NumElements число элементов в массиве.

WordLength количество битов, которые представляют тип данных массива.

Complexity 2 для массивов с комплексным базовым типом; 1 в противном случае.

Если какое-либо из вышеупомянутых условий является ложным, персистентный массив или пользовательская частная собственность Системного объекта сопоставляют с регистром в HDL-коде.

Значение по умолчанию RAMMappingThreshold 256. Чтобы изменить порог, использовать hdlset_param. Например, следующая команда изменяет порог отображения для sfir_fixed модель к 128 битам:

hdlset_param('sfir_fixed', 'RAMMappingThreshold', 128);

Можно также изменить порог отображения RAM в диалоговом окне Configuration Parameters. Для получения дополнительной информации смотрите, что RAM сопоставляет порог (биты) раздел в Параметрах Отображения RAM.

Для примера, который показывает, как сопоставить персистентные переменные типа массив с RAM в блоке MATLAB Function, смотрите, что RAM Сопоставляет С блоком MATLAB function.

Используйте MapToRAM сопоставлять интерполяционные таблицы (LUT) с RAM.

когда Simulate RAM Delay включен., MapToRAM свойство отключено для Оптимизированного HDL Косинуса и HDL Синуса Оптимизированные блоки.

| Установка MapToRAM | Отображение поведения |

'inherit' (значение по умолчанию) | Используйте адаптивную установку конвейеризации родительской подсистемы. Если эта подсистема является подсистемой высшего уровня, используйте адаптивную установку конвейеризации для модели. |

| Интерполяционные таблицы блока (LUTs) сопоставлены с логическими срезами на FPGA. |

| Интерполяционные таблицы блока (LUTs) сопоставлены с RAM. |

OutputPipeline позволяет вам задать реализацию с выходной конвейеризацией для выбранных блоков. Значение параметров задает количество выходных настроек канала связи (глубина трубопровода) в сгенерированном коде.

Следующий код задает выходную глубину трубопровода двух этапов для каждого блока Sum в модели:

sblocks = find_system(gcb, 'BlockType', 'Sum');

for ii=1:length(sblocks),hdlset_param(sblocks{ii},'OutputPipeline', 2), end;

Примечание

OutputPipeline установка не оказывает влияния на блоки, которые не имеют выходного порта.

При генерации кода для регистров трубопровода HDL Coder добавляет постфиксную строку к именам регистров трубопровода ввода или вывода. Постфиксной строкой по умолчанию является _pipe. Чтобы настроить постфиксную строку, используйте опцию Pipeline postfix в диалоговом окне Configuration Parameters во вкладке HDL Code Generation > Global Settings > General. В качестве альтернативы можно использовать PipelinePostfix свойство с makehdl. Для примера смотрите постфикс Трубопровода.

См. также Распределенную Вставку Трубопровода для блоков MATLAB function.

Используя RAMDirective, можно задать, хотите ли вы сопоставить блоки Оперативной памяти (RAM) в своей модели Simulink с блоками Оперативной памяти FPGA. Можно сопоставить блоки памяти большой емкости, такие как ultra от семейства Xilinx и M144k от Куарта®семейство. Задайте эти значения RAMDirective для блоков RAM в вашем проекте на основе инструмента синтеза.

| Инструмент синтеза | Атрибут стиля RAM | Значения RAMDirective |

| Куарт | ramstyle |

|

| Xilinx | ram_style |

|

| Микрополу® | syn_ramstyle |

|

Когда вы задаете значение для этой установки, HDL Coder генерирует ramstyle припишите в HDL-коде. Этот атрибут задает тип модуля Оперативной памяти, который вы хотите, чтобы инструмент синтеза использовал при выведении блоков RAM в проекте.

То, когда вы не делаете, задало любое значение для этой установки, HDL Coder не генерирует ramstyle припишите в HDL-коде. Инструмент синтеза определяет тип выведенного RAM для отображения блоков RAM в вашей модели.

В библиотеке HDL RAMs, за исключением Dual Rate Dual Port RAM, можно задать RAMDirective свойство для всех других блоков RAM.

Установить RAMDirective для блока RAM в диалоговом окне HDL Block Properties:

Щелкните правой кнопкой по блоку RAM.

Выберите HDL Code> HDL Block Properties.

В свойстве RAMDirective задайте значения как перечисленные в таблице.

Можно также установить RAMDirective при помощи hdlset_param функция.

hdlset_param(<ram_block_name>, ‘RAMDirective’, <attribute_value>);

Задавать эти атрибуты в MATLAB® Рабочий процесс HDL, используйте RAMDirective пара значения параметров для hdl.RAM инстанцирование. Установите это свойство при помощи этой команды:

hRam = hdl.RAM(‘RAMType’, ‘Single Port RAM’, ‘RAMDirective’, ‘ultra’);

Например, сгенерируйте атрибут HDL для отображения блоков RAM в вашей модели к block RAM. block RAM специализированный блок памяти на FPGA. Размерами блока RAM может быть 4kb, 8kb, 16kb, и 32kb.

Сопоставлять ваши блоки RAM с block RAM:

Задайте инструмент синтеза. Необходимо предназначаться для устройства Xilinx, которое содержит block RAM ресурсы. Если целевое устройство не содержит блок RAM, инструмент синтеза игнорирует этот атрибут и может вывести RAM как распределенные RAM или Интерполяционную таблицу (LUT) срезы.

Введите значение RAMDirective как block для вашего Simulink RAM блокируется в HDL Block Properties.

Сгенерируйте HDL-код для своей модели.

Этот сгенерированный код VHDL показывает ram_style атрибут установлен в block:

attribute ram_style: string; attribute ram_style of ram : signal is "block";

Это сгенерировало код Verilog, показывает ram_style атрибут установлен в block:

(* ram_style = "block" *)

При использовании свойства RAMDirective убедитесь, что выбрали инструмент синтеза для своего проекта.

Используйте ResetType параметры блоков, чтобы подавить генерацию логики сброса.

| Значение ResetType | Описание |

|---|---|

default | Сгенерируйте логику сброса. |

none | Не генерируйте логику сброса. Сброс не применяется к сгенерированным регистрам. Поэтому несоответствия между Simulink и сгенерированным кодом происходят для некоторого количества отсчетов во время начальной фазы, когда регистры не полностью загружаются. Чтобы избежать ошибок испытательного стенда во время начальной фазы, определите количество отсчетов, требуемое полностью загружать регистры. Затем установите опцию Ignore output data checking (number of samples) соответственно. См. также Ignore output data checking (number of samples) в Стимуле Испытательного стенда и Выходных параметрах. |

Можно задать ResetType для следующих блоков:

Chart

Convolutional Deinterleaver

Convolutional Interleaver

Delay

Delay (DSP System Toolbox™)

General Multiplexed Deinterleaver

General Multiplexed Interleaver

MATLAB Function

MATLAB System

Memory

Tapped Delay

Truth Table

Unit Delay Enabled

Unit Delay

Когда вы устанавливаете ResetType на none для блока MATLAB Function HDL Coder не генерирует логику сброса для персистентных переменных в коде MATLAB.

Однако, если вы задаете другую оптимизацию для блока, кодер может вставить регистры та логика сброса использования. Кодер не подавляет генерацию логики сброса для этих регистров. Поэтому, если вы устанавливаете ResetType на none наряду с другой оптимизацией блока, ваш сгенерированный код может иметь порт сброса в верхнем уровне.

Подавить генерацию логики сброса для блока с помощью пользовательского интерфейса:

Щелкните правой кнопкой по блоку и выберите HDL Code> HDL Block Properties.

Для ResetType выберите none.

Подавить генерацию логики сброса, на командной строке, введите:

hdlset_param(path_to_block,'ResetType','none')

Например, чтобы подавить генерацию логики сброса для блока Unit Delay, UnitDelay1, в подсистеме, mySubsys, на командной строке, введите:

hdlset_param('mySubsys/UnitDelay1','ResetType','none');

Чтобы задать синхронный или асинхронный сброс, используйте ResetType параметр уровня модели. Для получения дополнительной информации смотрите тип Сброса в Настройках Сброса и Параметрах.

Используйте этот параметр на блоках Min/Max, чтобы задать разделы для последовательной каскадной архитектуры. Настройка по умолчанию использует минимальное количество разделов.

| Сгенерировать это Архитектура... | Установите SerialPartition на... |

|---|---|

| Каскадно-последовательный с явным образом заданным разделением | [p1 p2 p3...pN]: вектор из N целые числа, где N количество последовательных разделов. Каждый элемент вектора задает длину соответствующего раздела. Сумма векторных элементов должна быть равна длине вектора входных данных. Значения векторных элементов должны быть в порядке убывания, кроме последних двух элементов может быть равным. Например, для входа 8 элементов, разделы [5 3] или [4 2 2] законны, но разделы [2 2 2 2] или [3 2 3] повысьте ошибку во время генерации кода. |

| Каскадно-последовательный с автоматически оптимизированным разделением | 0 |

Это свойство также используется для последовательных архитектур фильтра. Поскольку, как сконфигурировать блоки фильтра, смотрите SerialPartition.

Используйте SharingFactor задавать количество функционально эквивалентных ресурсов, чтобы сопоставить с одним совместно используемым ресурсом. Значением по умолчанию является 0. Смотрите Разделение ресурсов.

Используйте SoftReset параметры блоков, чтобы задать, сгенерировать ли благоприятную для оборудования синхронную логику сброса или локальную логику сброса, которая совпадает с поведением симуляции Simulink. Это свойство доступно для блока Unit Delay Resettable или блока Unit Delay Enabled Resettable.

| Значение SoftReset | Описание |

|---|---|

off (значение по умолчанию) | Сгенерируйте локальную логику сброса, которая совпадает с поведением симуляции Simulink. |

on | Сгенерируйте синхронную логику сброса для блока. Эта опция генерирует код, который более эффективен для синтеза, но не совпадает с поведением симуляции Simulink. |

Когда SoftReset установите на 'off', следующий код сгенерирован для блока Unit Delay Resettable:

always @(posedge clk or posedge reset)

begin : Unit_Delay_Resettable_process

if (reset == 1'b1) begin

Unit_Delay_Resettable_zero_delay <= 1'b1;

Unit_Delay_Resettable_switch_delay <= 2'b00;

end

else begin

if (enb) begin

Unit_Delay_Resettable_zero_delay <= 1'b0;

if (UDR_reset == 1'b1) begin

Unit_Delay_Resettable_switch_delay <= 2'b00;

end

else begin

Unit_Delay_Resettable_switch_delay <= In1;

end

end

end

end

assign Unit_Delay_Resettable_1 =

(UDR_reset ||

Unit_Delay_Resettable_zero_delay ? 1'b1 : 1'b0);

assign out0 = (Unit_Delay_Resettable_1 == 1'b1 ? 2'b00 :

Unit_Delay_Resettable_switch_delay);

Когда SoftReset установите на 'on', следующий код сгенерирован для блока Unit Delay Resettable:

always @(posedge clk or posedge reset)

begin : Unit_Delay_Resettable_process

if (reset == 1'b1) begin

Unit_Delay_Resettable_reg <= 2'b00;

end

else begin

if (enb) begin

if (UDR_reset != 1'b0) begin

Unit_Delay_Resettable_reg <= 2'b00;

end

else begin

Unit_Delay_Resettable_reg <= In1;

end

end

end

end

assign out0 = Unit_Delay_Resettable_reg;

Количество параллельных информационных каналов или векторы, чтобы преобразовать в последовательные, скалярные информационные каналы мультиплексирующими время последовательными путями данных и совместным использованием аппаратных ресурсов. Значение по умолчанию 0, который реализует полностью параллельные информационные каналы. См. также Потоковую передачу.

Можно использовать этот режим с блоками Product в режимах Divide и Reciprocal. Это свойство становится доступным, когда вы устанавливаете архитектуру HDL для блоков к ShiftAdd. Эта архитектура использует алгоритм деления невосстановления, который выполняет, несколько переключают и добавляют операции, чтобы вычислить частное. ShiftAdd архитектура обеспечивает улучшенную точность по сравнению с методом приближения Ньютона-Raphson.

Когда вы используете ShiftAdd архитектура, можно использовать UsePipelines параметр реализации, чтобы задать, использовать ли конвейерную или неконвейерную реализацию деления невосстановления.

| Установка UsePipelines | Отображение поведения |

|---|---|

| Используйте конвейерную реализацию невосстановления, переключают и добавляют операцию для блоков Reciprocal и Divide. Эта установка добавляет больше задержек с вашим проектом, но достигает более высокой максимальной тактовой частоты на целевом устройстве FPGA. Количество трубопроводов вставило, совпадает с количеством итераций, которых алгоритм требует, чтобы вычислить частное или обратную величину. |

| Используйте неконвейерную реализацию невосстановления, переключают и добавляют операцию для блоков Reciprocal и Divide. Эта установка не добавляет задержки с вашим проектом. Когда деление и обратная величина являются ресурсоемкими операциями, чтобы достигнуть более высоких тактовых частот на целевом FPGA, установить UsePipelines на |

Установить UsePipelines для подсистемы от диалогового окна HDL Block Properties:

Щелкните правой кнопкой по подсистеме.

Выберите HDL Code> HDL Block Properties.

Для UsePipelines выберите on или off.

Установить UsePipelines для блока из командной строки использовать hdlset_param. Например, чтобы выключить UsePipelines для блока Divide в подсистеме, my_dut:

hdlset_param('my_dut/divide', 'UsePipelines', 'off');

hdlset_param.UseRAM параметр реализации позволяет использовать основанное на RAM отображение для блока вместо того, чтобы сопоставить со сдвиговым регистром.

| Установка UseRAM | Отображение поведения |

|---|---|

| Задержка сопоставляет со сдвиговым регистром в сгенерированном HDL-коде, кроме одного случая. Для получения дополнительной информации смотрите Эффекты Потоковой передачи и Распределенной Конвейеризации. |

| Задержка сопоставляет с двухпортовым блоком RAM, когда следующие условия верны:

Если какое-либо условие является ложным, задержка сопоставляет со сдвиговым регистром в HDL-коде, если это не объединяет с другими задержками, чтобы сопоставить с одним RAM. Для получения дополнительной информации смотрите Отображение Нескольких Задержек с RAM. |

Этот параметр реализации доступен для блока Delay в библиотеке Simulink Discrete и блока Delay (DSP System Toolbox) в библиотеке DSP System Toolbox Signal Operations.

HDL Coder может также объединить несколько задержек равной длины в одну задержку и затем сопоставить объединенную задержку с одним RAM. Эта оптимизация предоставляет следующие преимущества:

Увеличенное заполнение на одном RAM

Совместное использование логики генерации адресов, которая минимизирует дублирование идентичного HDL-кода

Отображение задержек с RAM, когда отдельные задержки не удовлетворяют порогу

Следующие правила управляют, могут ли несколько задержек объединить в одну задержку:

Задержки должны:

Будьте на том же уровне иерархии подсистемы.

Используйте тот же скомпилированный шаг расчета.

Имейте UseRAM установите на on, или быть сгенерированным путем потоковой передачи или разделение ресурсов.

Имейте тот же ResetType установка, которая не может быть none.

Общий размер слова объединенной задержки не может превысить 128 битов.

RAMSize из объединенной задержки больше или равен RAMMappingThreshold значение. RAMSize продукт DelayLength * WordLength * VectorLength * ComplexLength.

DelayLength общее количество задержек.

WordLength количество битов, которые представляют тип данных объединенной задержки.

VectorLength число элементов в векторной задержке. VectorLength 1 для скалярной задержки.

ComplexLength 2 для комплексных задержек; 1 в противном случае.

RAMMappingThreshold поскольку следующая модель составляет 100 битов.

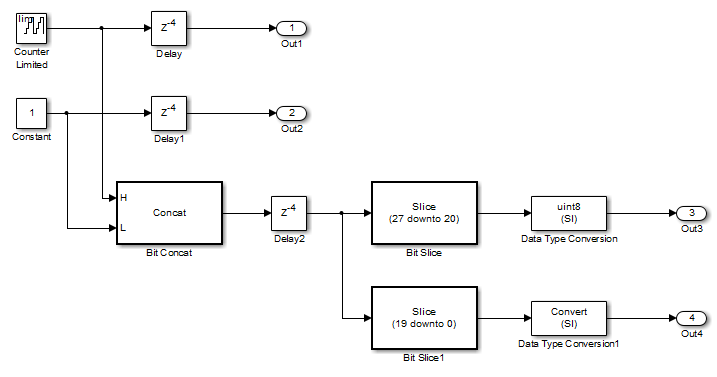

Задержка и Delay1 блокируют слияние и карту к двухпортовому RAM в сгенерированном HDL-коде путем удовлетворения следующим условиям:

Оба блока задержки:

На том же уровне иерархии.

Используйте тот же скомпилированный шаг расчета.

Установите UseRAM на on в диалоговом окне свойств блока HDL.

Имейте ту же установку ResetType default.

Общий размер слова объединенной задержки составляет 28 битов, который является ниже 128-битного предела.

RAMSize из объединенной задержки 112 битов (4 задержки * 28-битный размер слова), который больше порога отображения 100 битов.

Когда вы генерируете HDL-код для этой модели, HDL Coder генерирует дополнительные файлы, чтобы задать отображение RAM. Кодер хранит эти файлы в том же исходном месте как другие сгенерированные файлы HDL, например, hdlsrc папка.

Когда UseRAM off для блока Delay HDL Coder сопоставляет задержку со сдвиговым регистром по умолчанию. Однако кодер изменяет UseRAM установка на on и попытки сопоставить задержку с RAM при следующих условиях:

Потоковая передача включена для подсистемы с блоком Delay.

Распределенная конвейеризация отключена для подсистемы с блоком Delay.

Предположим, что распределенная конвейеризация включена для подсистемы с блоком Delay.

Когда UseRAM off, блок Delay участвует в повторной синхронизации.

Когда UseRAM on, блок Delay не участвует в повторной синхронизации. HDL Coder не разбивает задержку, отмеченную для отображения RAM.

Рассмотрите подсистему с двумя блоками Delay, тремя блоками Constant и тремя блоками Product:

Когда UseRAM on для блока Delay справа, та задержка не участвует в повторной синхронизации.

Следующие сводные данные описывают, пытается ли HDL Coder сопоставить задержку с RAM вместо сдвигового регистра.

UseRAM Установка для блока задержки | Оптимизация, Enabled для подсистемы с блоком задержки | ||

|---|---|---|---|

| Распределенная конвейеризация только | Потоковая передача только | Обе распределенных конвейеризации и потоковая передача | |

| On | Да | Да | Да |

| Off | Нет | Да, потому что отображение с RAM вместо сдвигового регистра может предоставить эффективный областью проект. | Нет |

Предупреждение

VariablesToPipeline не рекомендуется. Использование coder.hdl.pipeline вместо этого.

Параметр VariablesToPipeline позволяет вам вставить регистр трубопровода при выходе одной или нескольких переменных MATLAB. Задайте список переменных как вектор символов с пробелами, разделяющими переменные.

См. также Трубопровод Выражения MATLAB.