В этом примере показано, как можно сгенерировать HDL-код для простой встречной модели в Simulink®. Эта модель совместима для генерации HDL-кода. Чтобы создать эту встречную модель, смотрите, Создают Совместимую с HDL Модель Simulink.

Можно или создать собственную совместимую с HDL модель, такую как встречная модель или выбрать из:

Модели HDL Coder™ в качестве примера, доступные в hdlcoderdemos папка.

cd (fullfile(matlabroot,'toolbox','hdlcoder','hdlcoderdemos'))

Эти модели доступны на MATLAB® path. Например, можно выбрать симметричную КИХ-Модель Фильтра. Использовать эту модель, введите:

sfir_fixed

Simulink обрабатывает по шаблону для генерации HDL-кода. Можно использовать шаблоны для регистров модели, ROM, основных арифметических операций, комплексных множителей, сдвиговых регистров, и так далее.

Чтобы выбрать ваш шаблон, на панели инструментов MATLAB, нажимают![]() кнопку, и затем перешли к разделу HDL Coder. Смотрите Использование Шаблоны Simulink для генерации HDL-кода.

кнопку, и затем перешли к разделу HDL Coder. Смотрите Использование Шаблоны Simulink для генерации HDL-кода.

Прежде, чем сгенерировать HDL-код, можно проверять и обновить модель для совместимости HDL при помощи Советника по вопросам HDL-кода. Смотрите Совместимость HDL Проверки Модели Simulink Используя Советника по вопросам HDL-кода.

Откройте эту модель, чтобы видеть простой счетчик. Модель подсчитывает от нуля до порогового значения и затем переносится назад, чтобы обнулить. Пороговое значение установлено в 15. Чтобы изменить пороговое значение, измените значение входа к count_threshold порт. Разрешать сигнал задает, рассчитывает ли счетчик вверх или содержит предыдущее значение. Значение 1 указывает, что счетчик рассчитывает вверх постоянно.

Для встречной модели, HDL_DUT подсистема является DUT. Сгенерировать код для DUT:

Во вкладке Apps выберите HDL Coder.

Выберите DUT Subsystem в своей модели и убедитесь, что это имя Subsystem появляется в опции Code for на вкладке HDL Code. Чтобы помнить выбор, прикрепите эту опцию. Нажмите Generate HDL Code.

По умолчанию HDL Coder генерирует код VHDL в целевом hdlsrc папка.

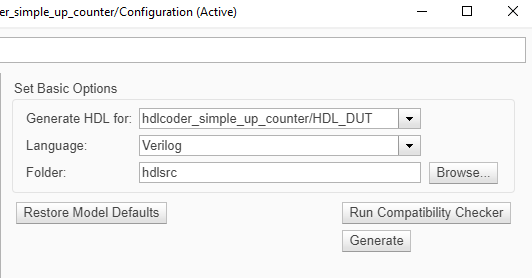

Сгенерировать код Verilog для встречной модели:

Во вкладке HDL Code нажмите Settings.

В панели HDL Code Generation, для Language, выбирают Verilog. Нажмите Apply и затем нажмите Generate.

HDL Coder компилирует модель прежде, чем сгенерировать код. В зависимости от параметров отображения модели, таких как типы данных порта, модель может изменение внешности после генерации кода. В то время как генерация кода продолжает, HDL Coder отображает сообщения о ходе выполнения в командной строке MATLAB со ссылками на конфигурацию модели и сгенерированные файлы. Чтобы просмотреть файлы в редакторе MATLAB, щелкните по ссылкам.

Процесс завершается и отображает сообщение:

### HDL Code Generation Complete.

Значок папки для hdlsrc папка появляется в текущей папке. Чтобы просмотреть весь сгенерированный код и файлы скрипта, дважды кликните hdlsrc папка, и затем дважды кликает папку, которая имеет то же имя как модель для который вы сгенерированный HDL-код.

HDL_DUT.vhd: VHDL® код, который содержит определение сущности и архитектуру RTL, реализующую счетчик, который вы спроектировали. Если вы сгенерировали код Verilog, вы получаете HDL_DUT.v файл.

HDL_DUT_compile.do: Mentor Graphics® ModelSim® скрипт компиляции.

HDL_DUT_map.txt: Отображение регистрирует, который сопоставляет сгенерированные сущности или модули в HDL-коде к подсистемам в модели, которая сгенерировала их. См., что Код Трассировки Использует Файл Отображения.

HDL_DUT_report.html: Отчет проверки HDL отображает состояние генерации HDL-кода и предупреждения или сообщения.

gm_hdlcoder_simple_up_counter.slx: Сгенерированная модель, которая поведенчески представляет HDL-код в среде моделирования Simulink.

HDL Coder создает поведенческую модель HDL-кода, названного generated model. Сгенерированное имя модели совпадает с исходной моделью и имеет префиксный gm_. Сгенерированная модель битно-верна и цикл - с точностью до сгенерированного HDL-кода. Эта модель показывает эффект реализаций блока и скорости и оптимизации области, что вы задали. См. также Скорость и Оптимизацию области в HDL Coder.

Открыть сгенерированную модель для счетчика, введите:

gm_hdlcoder_simple_up_counter

Для встречной модели, когда оптимизация отключена, сгенерированная модель идентична исходной модели.

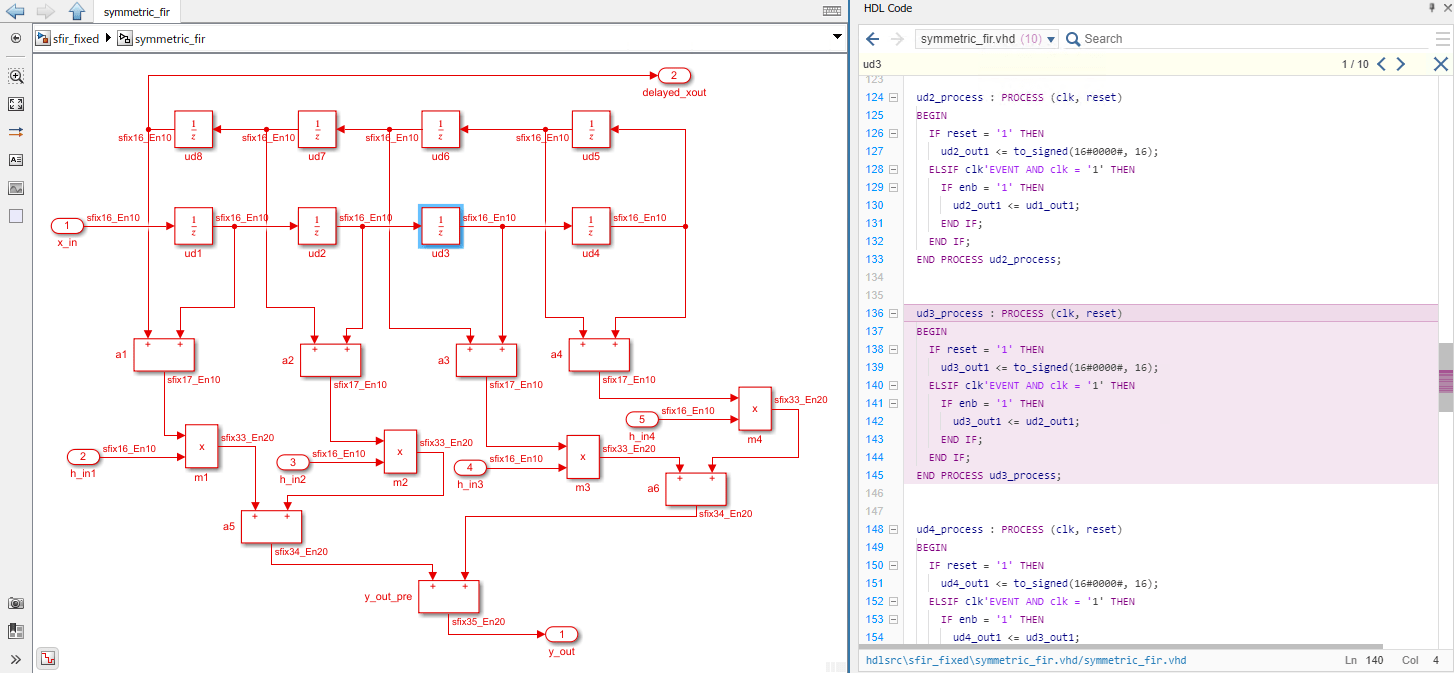

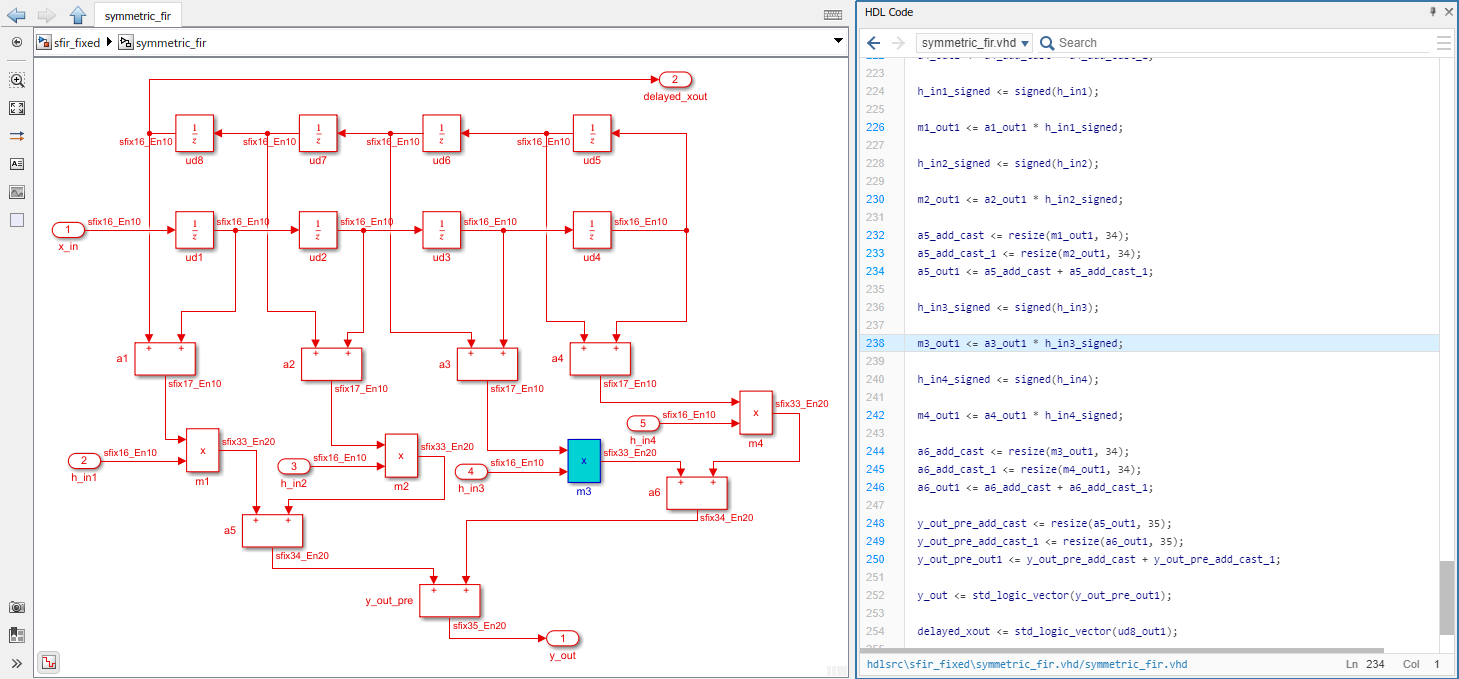

Чтобы просмотреть ваш сгенерированный HDL-код вместе с вашей моделью, можно использовать Представление кода. После того, как вы сгенерируете HDL-код для своей модели, Представление кода отображает сгенерированный код справа от вашей модели. Чтобы вручную открыть Представление кода, откройте приложение HDL Coder. На Simulink панель инструментов нажимают кнопку View Code. Выберите файл, который вы хотите отобразить при помощи выпадающего списка наверху Представления кода. Можно прикрепить или расстыковать Представление кода из редактора и минимизировать или расширить Представление кода с помощью значка контакта в правом верхнем углу Представления кода.

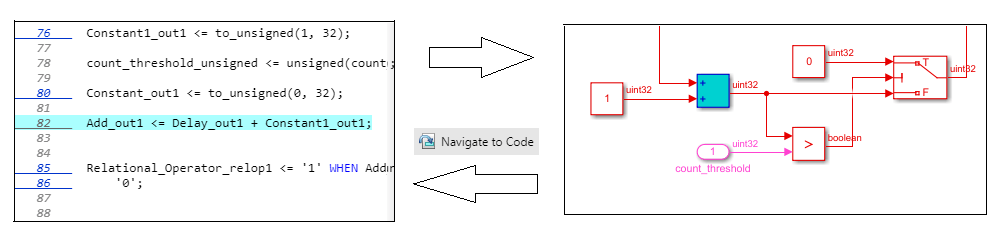

Чтобы идентифицировать отображение между исходной моделью и сгенерированным HDL-кодом более легко, сгенерируйте отчет трассируемости. Используйте отчет перейти от блока в вашей модели к сгенерированному коду для того блока и от кода до блока в вашей модели.

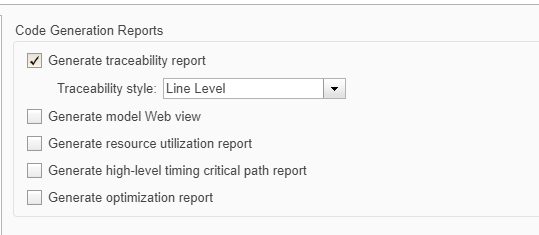

Сгенерировать отчет трассируемости:

Во вкладке HDL Code нажмите Settings> Report Options.

В HDL Code Generation> панель Report, выберите Generate traceability report, и затем сгенерируйте HDL-код для HDL_DUT подсистема

После того, как вы сгенерируете код, окно Code Generation Report открывается. HDL Coder записывает файлы отчета генерации кода в hdlsrc\html\ папка папки сборки. Если вы закрываете отчет, можно перейти к этой папке, чтобы вновь открыть отчет.

Чтобы перейти от HDL-кода до модели, следуйте за любым из этих рабочих процессов:

Используйте Представление кода:

Кликните по панели Представления кода справа, которая появляется после генерации HDL-кода, или вручную нажмите кнопку View Code на панели инструментов Simulink приложения HDL Coder.

Чтобы перейти от элементов модели до их сгенерированного кода, в вашей модели, кликают по блоку. Представление кода подсвечивает код для блока и прокруток к подсвеченным строкам кода.

В Представлении кода кликните по гиперссылке номера строки, или комментарий к коду соединяются, чтобы подсветить блок, до которого прослеживает строка кода. Вы можете соединительные линии кода к элементам модели, от которых они были сгенерированы.

Используйте отчет генерации кода:

В Отчете Генерации кода перейдите к разделу Traceability Report, и затем щелкните по ссылкам в разделе Code Location.

Выберите гиперссылку на строку кода, чтобы подсветить соответствующий блок в вашей модели.

Чтобы перейти от блока в вашей модели к HDL-коду, выберите тот блок, и затем нажмите кнопку Navigate to Code в разделе Review Results вкладки HDL Code.

Смотрите перешли между моделью Simulink и HDL-кодом при помощи трассируемости и создают и используют отчеты генерации кода.

В разделе Generated Source Files, если вы кликаете по файлу HDL HDL_DUT, вы видите сигналы clkсброс, и clk_enable. Эти сигналы являются часами, сбросом, и часы включают сигналы, которые управляют триггерами на целевом компьютере. HDL Coder генерирует эти сигналы в коде в зависимости от последовательных элементов, таких как блоки Delay, которые вы используете в своей модели. Смотрите Генерацию Сигналов Пакета Часов в HDL Coder.

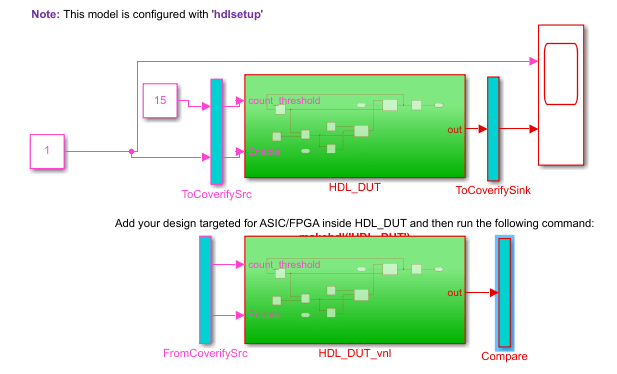

Чтобы подтвердить поведенческую модель HDL-кода с вашей исходной моделью, сгенерируйте модель валидации. Модель валидации содержит обоих исходная модель и сгенерированная модель. Это сравнивает выходные параметры обеих моделей при помощи тестовых векторов, которые вы обеспечили в исходной модели.

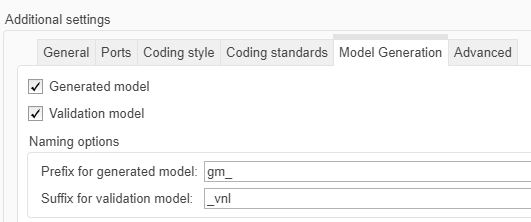

Сгенерировать модель валидации:

Во вкладке HDL Code нажмите Settings.

Во вкладке HDL Code Generation> Global Settings> Model Generation выберите Validation model, и затем сгенерируйте HDL-код для HDL_DUT подсистема.

В журналах генерации кода вы видите ссылку на модель валидации. Модель валидации имеет тот же префикс как сгенерированная модель и также имеет суффиксный _vnl. Для встречной модели модель валидации имеет имя gm_hdlcoder_simple_up_counter_vnl.slx. Можно найти эту модель в той же папке как сгенерированная модель. Открыть эту модель, введите:

gm_hdlcoder_simple_up_counter_vnl

После того, как вы симулируете модель, дважды кликаете Compare подсистема, и затем перешла в Assert_Out подсистема. Если вы открываете блок Scope, вы видите что err сигнал имеет значение нуля, что означает, что сгенерированная модель выводила соответствия исходная модель.

Прежде чем вы развернете свой проект на целевом компьютере, проверите сгенерированный HDL-код. От hdlsrc папка, перейдите к текущей рабочей папке. Смотрите Проверяют Сгенерированный HDL-код из Модели Simulink.

makehdl | hdlset_param | hdlsetup