Преобразуйте скалярный поток или меньшие векторы к векторному сигналу

HDL Coder / Операции HDL

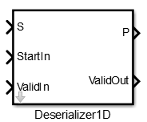

Буфера блоков Deserializer1D более быстрый, скалярный поток или вектор сигнализируют в больший, более медленный векторный сигнал. Более быстрый входной сигнал преобразован в более медленный сигнал на основе Ratio и значений Idle Cycle, преобразование изменяет шаг расчета. Кроме того, выходной сигнал задерживается один медленный цикл сигнала, потому что сериализированные данные должны быть собраны, прежде чем это сможет быть выведено как вектор. Смотрите примеры ниже для получения дополнительной информации.

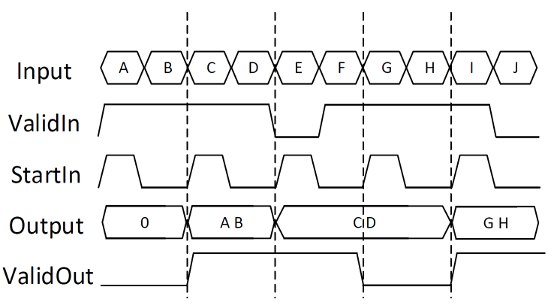

Можно сконфигурировать десериализацию, чтобы зависеть от допустимого входного сигнала, ValidIn и запуск сигнализируют о StartIn. Если ValidIn и параметры блоков StartIn оба выбраны, сбор данных запускается, только если и сигналы ValidIn и StartIn верны. Рассмотрите этот пример:

Ratio является 2 и Idle Cycles является 0, таким образом, каждый выходной цикл является двумя входными сигналами долго со всеми рассмотренными точками данных.

ValidIn и StartIn выбраны, таким образом, сбор данных может начаться только, когда и сигналы StartIn и ValidIn верны.

ValidOut выбран.

В первом цикле ValidIn и StartIn верны, таким образом, сбор данных начинается для A и B. Блок выводит десериализованный вектор в следующем допустимом цикле, таким образом, вектор AB выводится в следующем цикле. Это также верно во втором цикле для C и D.

В третьем цикле, запускающемся в E, StartIn верен, но ValidIn не. E пропущен. В F ValidIn верен, но StartIn не, таким образом, F также пропущен. Поскольку это не может собрать данные для E или F, Deserializer1D выходные параметры предыдущий вектор цикла, CD, но изменения ValidOut во лжи.

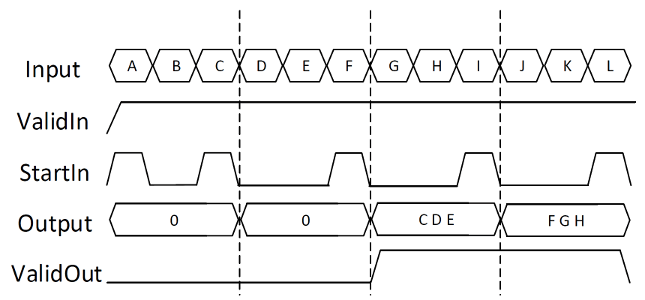

Другой сценарий, чтобы рассмотреть - когда сигнал StartIn прибывает слишком рано. Если длина между двумя сигналами StartIn не достаточно долга, чтобы собрать полный цикл отношения, недостаточные данные сигнала пропущен. Рассмотрите этот пример:

Ratio является 3, таким образом, каждый цикл является двумя разделами долго.

Idle Cycles является 0, таким образом, все вводы данных рассматриваются.

ValidIn и StartIn выбраны, таким образом, сбор данных может начаться только, когда и сигналы StartIn и ValidIn верны.

ValidOut выбран.

В первом цикле ValidIn и StartIn верны, таким образом, сбор данных может начаться для A и B. Однако в C другой сигнал StartIn прибывает, прежде чем три сигнала могут быть собраны. Поскольку StartIn прибыл рано, A, и B пропущены, и никакой допустимый вектор не собран во время первого цикла. Поэтому выход второго цикла является все еще нулевым. Десериализация начинается в StartIn в C, для C, D, и E. Этот вектор выводится в следующем допустимом цикле, который является циклом 3. Точно так же десериализация запускается снова в StartIn в F и выводит вектор FGH в четвертом цикле.

Вы задаете блок выход в течение первого периода выборки со значением параметра Initial condition.

Введите отношение десериализации. Значением по умолчанию является 1.

Отношение является размером выходного вектора, разделенным на размер входного вектора. Отношение должно быть делимым размером входного вектора.

Введите номер неактивных циклов, добавленных в конец каждого сериализированного входа. Значением по умолчанию является 0.

Значение Idle Cycles влияет на десериализованную норму выработки. Например, если Ratio является 2 и входным сигналом является A, B, B, C, D, D, ..., без неактивных циклов выходом был бы AB, BC, DD.... Однако для того же входа и отношения с набором Idle Cycles к 1, выходом является AB, CD.... Неактивные циклы, B и D, пропущены.

Поведение Deserializer1D изменяется, если Idle Cycles не является нулем, и ValidIn или StartIn включены. Неактивное значение циклов влияет только на норму выработки, в то время как ValidIn и StartIn управляют тем, какие входные данные десериализовывается.

Задайте начальный выход симуляции. Значение по умолчанию 0.

Выберите, чтобы активировать порт StartIn. Значение по умолчанию выключено.

Выберите, чтобы активировать порт ValidIn. Значение по умолчанию выключено.

Выберите, чтобы активировать порт ValidOut. Значение по умолчанию выключено.

Введите размер сигнала входных данных. Входной размер должен быть делимым отношением плюс количество неактивных циклов. По умолчанию блок наследовал размер на основе контекста в модели.

Введите временной интервал между хитами шага расчета или задайте другой соответствующий шаг расчета такой как непрерывный. По умолчанию блок наследовал свой шаг расчета на основе контекста в модели. Для получения дополнительной информации смотрите Шаг расчета.

Задайте тип входного сигнала блока как autoдействительный, или complex.

SВходной сигнал, чтобы десериализовать. Типы данных шины не поддерживаются.

ValidInУказывает на допустимый входной сигнал. Используйте с блоком Serializer1D. Этот порт доступен, когда вы устанавливаете флажок ValidIn.

Тип данных: Boolean

StartOutУказывает, где запустить десериализацию. Используйте с блоком Serializer1D. Этот порт доступен, когда вы устанавливаете флажок StartOut.

Тип данных: Boolean

PДесериализованный выходной сигнал. Типы данных шины не поддерживаются.

ValidOutУказывает на допустимый выходной сигнал. Этот порт доступен, когда вы устанавливаете флажок ValidOut.

Тип данных: Boolean